(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ умножения двух сигналов | 1978 |

|

SU748437A1 |

| Электронный счетчик электроэнергии | 1979 |

|

SU866491A1 |

| Измеритель энергии искры | 1982 |

|

SU1078347A1 |

| Аналого-цифровое множительное устройство | 1978 |

|

SU769557A1 |

| Устройство для измерения интервалаВРЕМЕНи МЕжду дВуМя СигНАлАМи | 1978 |

|

SU838659A1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Аналоговый перемножитель | 1984 |

|

SU1166143A1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1525915A1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| Устройство для определения одномерных начальных моментов К-го порядка случайного сигнала | 1983 |

|

SU1108464A1 |

1

Изобретение относится к области измерительной и вычислительной техники .

Известны устройства, использующие для умножения дву}с сигналов прицип двойного интегрирования. Они содержат интеграторы, сргшиивающие устройства, ключи, логические элементы 1 .

Недостатком таких устройств является то, что в них произведение входных сигнсшов получается как результат двух последовательных операций: накопления величины одного из сомножителей в интеграторе (заряд) в течение определенного отрезка времени и разряда интегратора постоянным током, причем мерой величины произведения служит время разряда. Наличие двух разнесенных во времени операций - заряда и разряда - не позволяет непосредственно получить произведение двух сигналов в виде пропорционального ему периода следования импульсов (между периодами следования, несущими полезную информацию, располагаются интервалы времени, не связанные с произведением) Период Т между двумя соседними моментами начала заряда интегратора

состоит из времени его заряда t. и времени его разряда tp Т t -)- t р .

При этом произведению входных сигналов X, Y пропорционален интервал tp

tp XY,

Т t + ХУ.

Интервал связан не с произведеoнием, а только с одним из сомножителей, поэтому наличие его в сумме вносит методическую ошибку преобразования.

Наиболее близким техническим ре5шением к данному изобретению является устройство для умножения 2, содержащее два интегратора, схему сравнения, нуль-орган, элемент И, триггер, ключ, формирователь импульсов,

0 источник опорного напряжения, источники входных сигнсшов, причем вход первого интегратора через ключ соединен с первым источником входного сигнала, а выход первого интеграто5ра соединен со входом нуль-органа, выход второго интегратора соединен с первым входом схемы сравнения.

Иапряжение одного из сомножителей интегрируется первым интеграто0ром в течение -постоянного интервс1ла

времени. Затем этот интегратор начинает интегрировать постоянное напряжение обратной полярности. Одновременно второй интегратор начинает интегрировать напряжение второго сомножителя, в комент, когда первый интегратор возвращается в исходное

положение, второй интегратор начинает интегрировать указанное выое постоянное напряжение обратной полярности. Интервал времени, за который второй интегратор возвращается в исходное положение, измеряется с помощью постоянной частоты.

Это устройство обладает недостаточной точностью, т.е. имеет методическую погрешность, связанную с преобразованием одн-ой из умножаемых величин в интервал времени.

Целью изобретения является повышение точности.

Это достигается тем, что предлагаемое устройство содержит дополнительный источник опорного напряжени подключенный ко входу первого интегратора, второй вход cxerviH сравнения соединен со вторым источником входного сигнаша, а выход схемы сравнения соединен с нулевым входом триггера, нулевой выход которого соединен с первым входом элемента И и с управляющим входом второго интегратора, единичный вьзход триггера соединен с управляющим входом ключа выход нуль-органа подключен ко вторму входу элемента И, выход которого соединен с единичным входом триггера и с входом формирователя импульсов, вход второго интегратора соединен с основным источником опорного напряжения.

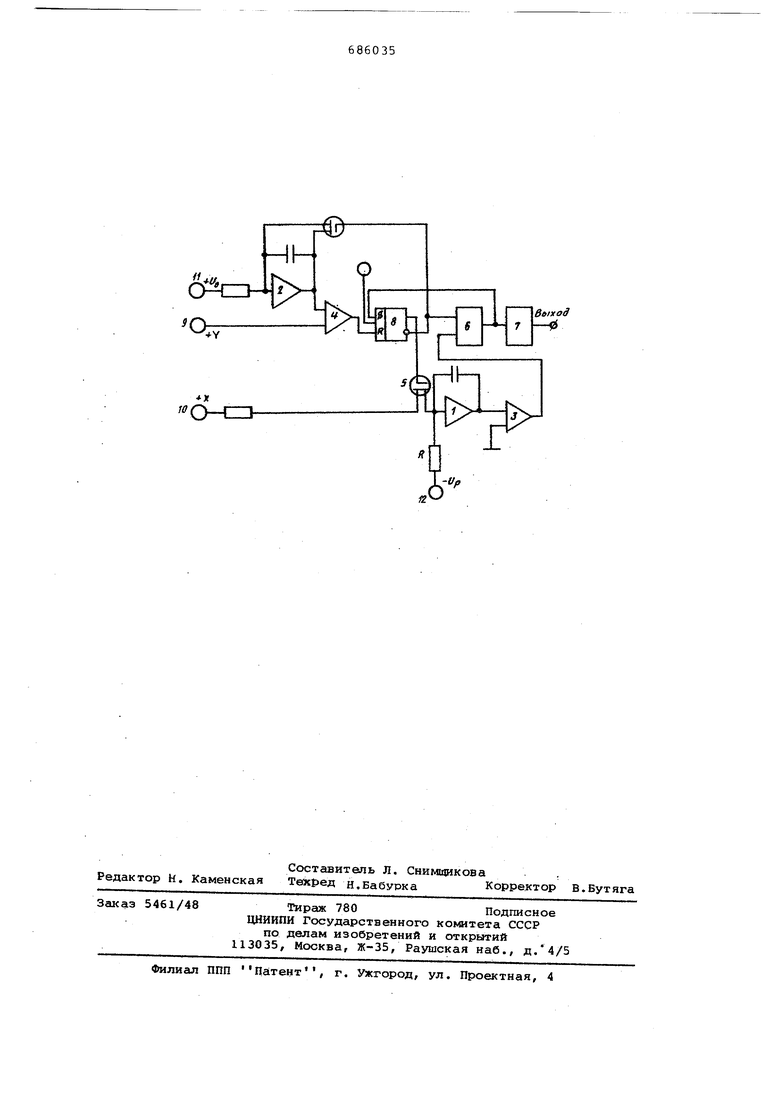

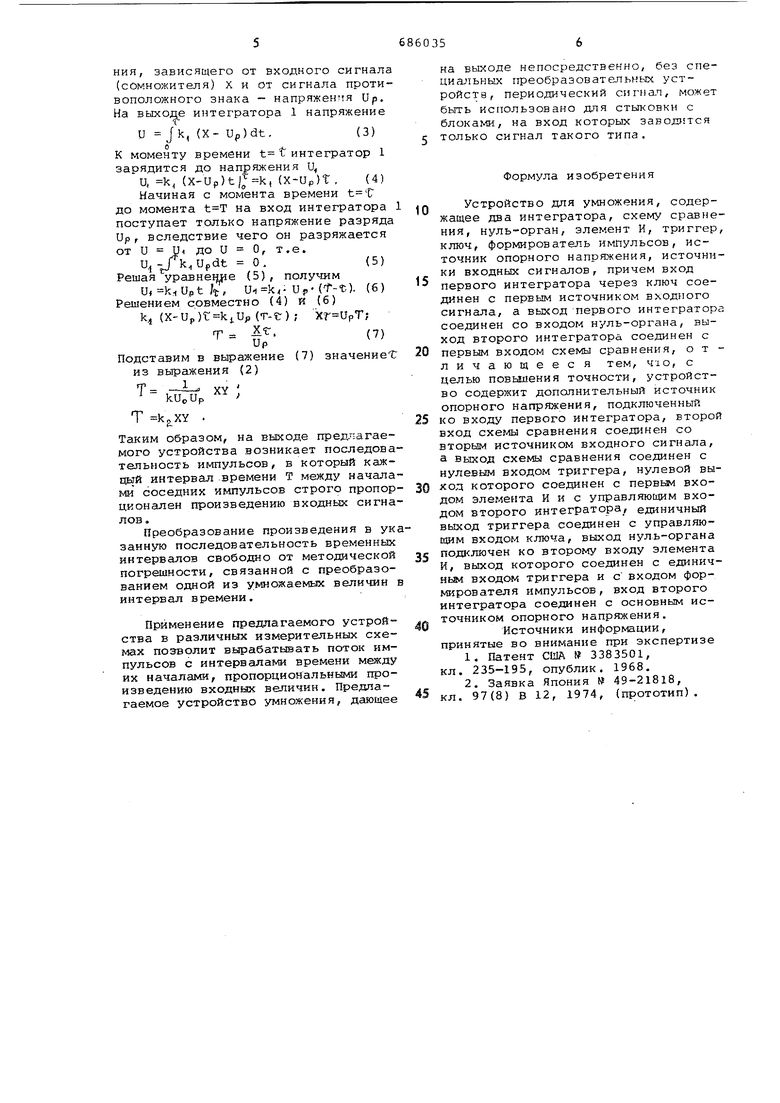

На чертеже показана функциональная схема предлагаемого устройства.

Оно содержит два интегратора 1, 2, нуль-органа 3, схему сравнения 4, ключ 5, элемент И 6, формирователь импульсов 7, триггер 8, источники 9, 10 входных сигналов, источник опорного напряжения 11 (и,,) той же полярности, что и входные сигналы, источник опорного напряжения 12 (-Up) обратной полярности.

Устройство работает следующим обра зрм.

В схеме постоянно действуют напряжения Uo, -Up. Пусть в момент времени в результате предшествующего цикла преобразования, или по сигналу цепи первоначального пуска, триггер 8 окажется приведенным по единичному входу в положение . В этот момент времени интеграторы 1 и 2 разряжены и напряжения на их выходах равны нулю. Начиная с этого момента времени отпирается ключ 5, вследствие чего на вход интегратора 1 через ключ 5 поступит от источника 10 входная величина X - первый сомножитель. При этом на интегратор 1 постоянно действует еще и напряжение разряда -Up противоположное по знаку сигналу X. В этот же момент времени интегратор 2 заряжается напряжением V от источника 11.

По мере заряда интегратора 2 напряжение на его выходе увеличивается и в момент времени t достигает значения, равного величине сигнала Y источника 9 (второй сомножитель). Тогда срабатывает схема сравнения 4 и своим выходным сигналом устанавливает триггер 7 в положение О . Вследствие этого на управляющий вход интегратора подается сигнал, закроется ключ 5 и подготовится к работе логический элемент И б. С этого момента времени прекращается накопление величины X в интеграторе 1 а интегратор 2 быстро разряжается через ключ до нуля. На входе интегра тора 1 продолжает действовать только напряжение разряда и$ (для того, чтобы устройство было работоспособным, минимальная величина сигнала X должна быть больше напряжения Up). Через некотбрый интервал времени (Т-Т) интегратор 1 также разрядится до нуля. Тогда произойдет срабатывание нуль-органа 3, который своим выходным сигналом откроет ранее подготовленный элемена- И. Выходной сигнал элемента И б установит триггер 8 в состояние , вапедствие чего начинается новый цикл преобразозания, адекватный описанному вьзше. Получаемый на выходе элемента И б сигнал (интервал времени Т между началами импульсов), пропсфционален произведению входных сигналов - Y-X. Этот сигнал, сформированный в формирователе, поступает на выход устройства.

То, что любой временной интервал между началами двух соседних импульсов на выходе логического элемента И пропорционален произведению ХУ, доказьшается следующим образом. Начиная с момента времени интегратор 2 начинает заряжаться напряжением Uo. При этом текущее значение напряжения у на выходе интегратора 2 выражается как

у J ,(I)

о

где t f- момент времени, при котором у У,

k - коэффициент пропорциональности . Из выражения {I) следует, что

.ТY

(2)

kU

На вход интегратора 1 в течение промежутка времени от до t С поступает сигнал некоторого напряжения, зависящего от входного сигнала (сомножителя) X и от сигнала противоположного знака - напряжения Up. На выходке интегратора 1 напряжение

и Jk, (Х- Up)dt.(3)

К моменту времени t tинтегратор 1 зарядится до напряжения и

и, k (X-Up), {X-Up)T, (4)

Начиная с момента времени до момента на вход интегратора поступает только напряжение разряда Up, вследствие чего он разряжается от и У до и О, т.е.

.Updt 0.(5)

Решая у азнец е (5), получим

и k:, Up t Jt, Ut k и p (f-г). (6) Решением совместно (4) к (6)

k (X-Up).Up(T-tr) ;

T .(7)

Up

Подставим в выражение (7) значение : из выражения (2)

Т - -i YV

kUcUp Т .

Таким об-разом, на выходе предлагаемого устройства возникает последовательность импульсов, в который каждый интервал-времени Т между началаt-ш соседних импульсов строго пропорционален произведению входных сигналов,

Преобразование произведения в указанную последовательность временных интервалов свободно от методической погрешности, связанной с преобразованием одной из умножаемых величин в интервал времени.

Применение предлагаемого устройства в различных измерительных схемах позволит вырабатывать поток импульсов с интервалами времени между их началами, пропорциональными произведению входных величин. Предлагаемое устройство умножения, дающее

на выходе непосредственно, без специальных преобразовательных устройств, периодический сягнап, может быть использовано для стыковки с блоками, на вход которых завод} тся 5 только сигнал такого типа.

Формула изобретения

длУстройство для умножения, содержащее два интегратора, схему сравнения, нуль-орган, элемент И, триггер, ключ, формирователь импульсов, источник опорного напряжения, источники входных сигнсшов, причем вход

15 первого интегратора через ключ соединен с первым источником входного сигнала, а выход первого интегратора соединен со входом нуль-органа, выход второго интегратора соединен с 0 первым входом схемы сравнения, отличающееся тем, 410, с целью повьшения точности, устройство содержит допалнительный источник опорного напряжения, подключенный 5 ко входу первого интегратора, второй вход схемы сравнения соединен со вторым источником входного сигнала, а выход схемы сравнения соединен с нулевым входом триггера, нулевой вы0 ход которого соединен с первым входом элемента И и с управляющим входом второго интегратора, единичный выход триггера соединен с управляющим входом ключа, выход нуль-органа 5 подключен ко второму входу элемента И, выход которого соединен с единичньм входом триггера и с входом формирователя импульсов, вход второго интегратора соединен с основным ис точником опорного напряжения. Источники инфорг иции,

принятые во внимание при экспертизе

//

вйгход

-0.

Авторы

Даты

1979-09-15—Публикация

1977-06-27—Подача