дополнительных элементов И-НЕ. Выход . первого элемента И-НЕ соединен с первым входом второго элемента И-НЕ, выход которого подключен к управляющему входу первого ключевого элемента и входу третьего триггера, выход которого присоединенко второму входу третьего дополнительного элемента И-НЕ, выход которого является выходом устройства. Выходчетвертого триггера соединен со вторыми входами первого элемента И-НЕ и второго дополнительного элемента И-НЕ, выход которого подключен ко второму входу второго триггера. Нервый -и второй входы первого дополнительного элемента И-НЕ соединены соответственно с первым и вторы.м входами четвертого триггера. Выход пятого триггера подключен к управляющему входу второго ключевого элемента. Выходы реверсивного счетчика присоединены ко входам четвертого дополнительного элемента И- НЕ, выход которого соединен с третьими входами четвертого, пятого и шестого триггеров. Выход щестого триггера подключен к блокирующему входу реверсивного счетчика. Первый выход седьмого триггера присоединен ко входу «Счет вперед реверсивного счетчика и первому входу пятого дополнительного элемента И-НЕ. Второй выход седьмого триггера подключен ко входу «Счет назад реверсивного счетчика, счетный вход которого соединен со счетным входом выходного счетчика и первым выходом генератора эталонной частоты, второй выход которого подключен к счетному входу блока управления, первый выход которого присоединен, к управляющему входу третьего ключевого элемента.- Второй выход блока управления подключен к первому входу третьего элемента И-НЕ и первым входам шестого и седьмого триггеров. Второй вход третьего элемента И-НЕ соединен с входом установки в исходное состояние устройства. Выход третьего элемента И-НЕ присоединен к входам установки в исходное состояние всех триггеров, блока управления, реверсивного и выходного счетчиков. Третий выход блока управления подключен ко второму входу пятого дополнительного элемента , выход которого соединен со вторым входом пятого триггера, а через блок задержки - со вторым входом седьмого триггера. Четвертый и пятый выходы блока управления присоединены соответственно к четвертому входу четвертого триггера и управляющему входу блока коррекции дрейфа. Вь1ход первого элемента И- НЕ подключен к управляющему входу четвертого ключевого элемента.Выход первого дополнительного элемента И-НЕ соединен с третьим входо пятого дополнительного элемента И-НЕ.

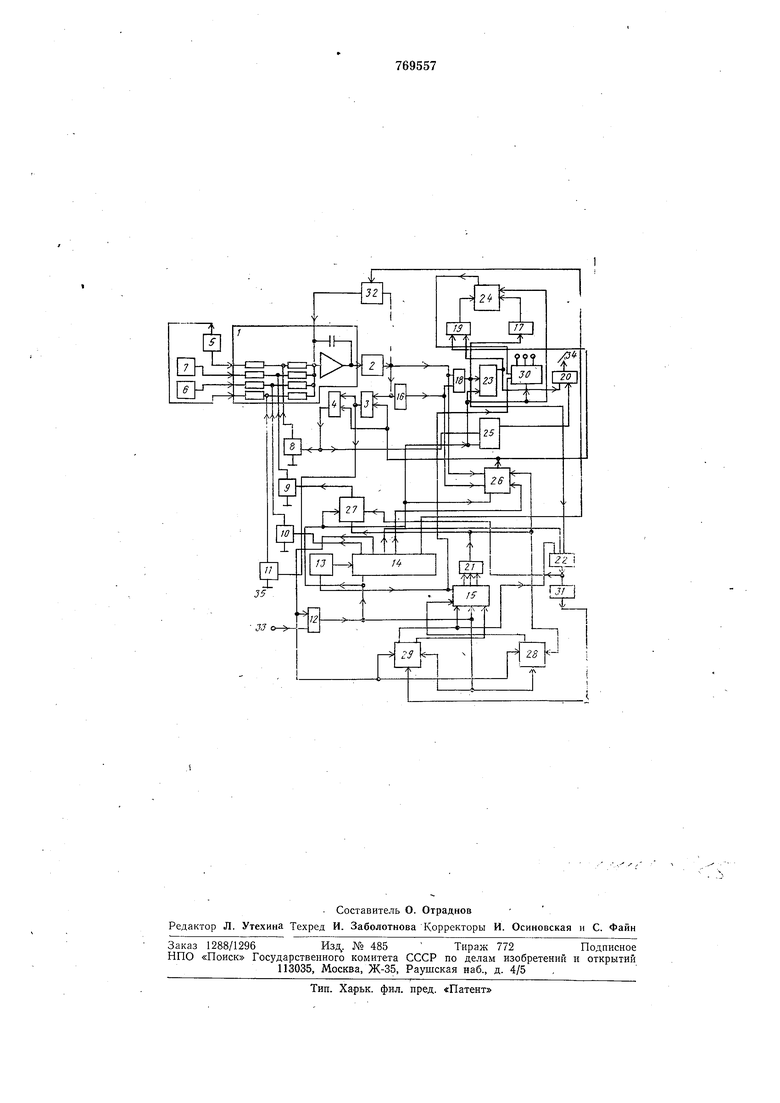

Функциональная схема предложенного аналого-цифрового множительного устройОно содержит интегратор 1, нуль-орган 2, первый и второй элементы И-НЕ 5 и 4, источник эталонного напряжения .5, первый и второй источники напряжений - .сомножителей 6 i 7, первый, второй, третий и четвертый ключевые элементы 8, 9, 10 и //, элемент И-НЕ 12, генератор эталонной частоты 13, блок управления 14, ре версивный счетчик 15, первый и второй инвертирующие элементы 16 и 17, первый, второй, третий, четвертый и пятый дополнительн.ые элементы И-НЕ 18, 19, 20, 21, 22, первый, второй, третий, четвертый, пятый, шестой и седьмой триггеры 23, 24, 25, 26,

27, 28 и 29, ВЫХОДНОЙ счетчик 30, блок задержки 31, блок коррекции дрейфа 32, вход установки в исходное состояние 33 и выход 34 устройства и щину нулевого потенциала 35.

Устройство работает следующим образом.

Импульсом, поступающим оо входа установжи в исходное состояние, все триггеры 23-29, счетчики /5 и 30 и блок управлеН|ИЯ /4 устанавливаются в исходное состояние. На первом щаге блока управления 14 в момент време:ни /i единичным импульсом с его первого выхода размыкается ключевой элемент W и на второй вход интегратора / поступает сигнал от первого источника напряжения-сомножителя 6. Остальные ключевые элементы 8, 9 и // в это время замкнуты. В результате на выходе интегратора / формируется напряжение.

f/.(0 4

(1)

J f

где Т - постоянная интегрирования;

и. - напряжение первого источника напряжения-сомножителя 6;

/ь 2 - моменты времени от начала до конца интегрирования.

В момент времени t при переходе блока управления 14 с первого на второй щаг импульсом со второго выхода блока управления 14 триггеры 28-ц 29 перебрасываются в

нулевое состояние. «Логическая 1 с1инверсного выхода седьмого триггера 29 поступает на вход «Счет Вперед, в «Логический О на вход «Счет назад счетчика J5. С инверсного выхода триггера 28 на блокирующий вход-счетчика /5.поступает сигнал разрешения счета в момент времени г2. Счётчик 15 начинает заполняться импульсами, поступающими от генератора эталонной частоты 13.

Импульс с четвертого выхода блока управления 14 устанавливает триггер 26 в единичное состояние, с выхода которого «1 поступает на входы элементов 33 и 34, которые осуществляют выбор полярности комлонного напряжения 5. для напряженийсомножнтелей. В зависимости от полярности выходного сигнала нуль-органа 2 размыкается ключевой элемент 11 или 8 и на интегратор / поступает положительное или отрицательное напряжение от источника эталонного напряжения 5. На выходе интегратора /формируется линейно - изменяющийся компенсирующий сигнал в полярности, противоположной сигналу, определяемому выражением U-,( U,d, где t/э - напряжение источника эталонного напряжения 5; /3 - момент компенсации выходного напряжения . интегратора 1. Из условия компенсации следует и, - и, С учетом выражений (2) и (3) можно найти, что длительность шага блока управления 14 должна быть равна постоянной интегрирования. В момент компенсации на выходе нульоргана 2 формируется сигнал, который в зависимости от полярности проходит непосредственно на элемент И-НЕ 18 или через элемент 16, и с его выхода через элемент И-НЕ 22 и блок задержки 31 переводит триггер 29 в единичное состояние. На вход счетчика 15 «Счет назад поступает «1. на вход «Счет вперед «О. Счетчик 15 начинает очищаться импульсами, поступающими на его счетный вход с генератора эталонной частоты 13. Этот же выходной сигнал нуль-органа 2 устанавливает триггер 27 в нулевое состояние, и его выходной сигнал размыкает ключевой элемент 9. Сигнал Qo второго источника напряжения-сомножителя 7 поступает на интегратор 1 и интегрируется, в течение промежутка времени, за который происходит очистка счетчика 15. В момент очистки t счетчика 15 срабатывает четвертый дополнительный элемент И-НЕ 21, и на его выходе формируется «О, который устанавливает триггер 27 в единичное состояние. В результате с помощью ключевого элемента 9 отключается второй источник напряжения-сомножителя 7. Устанавливается в нулевое состояние триггер 25, с инверсного выхода которого поступает разр|ешение на элементы И-НЕ 3 и 4 на выбор полярности компенсирукзщеГо эталонного напряжения. Устанавливается в единичное состояние триггер 28 с инверсного выхода которого «О поступает на блокирующий вход счетчика 15. За время очистки счетчика 15 выходной сигнал интегратора / равен Ut, K-U,Uy. где К - коэффициент пропорциональности;Uy - величина напряжения второго источника напряжения-сомножителя 7. В момент 4 в зависимости от полярности сигнала на выходе нуль-органа 2 на вход интегратора / через элементы И-НЕ 3 и 4 с помощью ключевых, элементов 8 и // подключаются один или второй выводы источника эталонного напряжения 5, которое интегрируется до равенства нулю выходного напряжения интегратора 1. В этот момент /5 на выходе нуль-органа 2 формируется сигнал, который устанавливает триггер 26 в единичное состояние, и «О с инверсного выхода триггера 26 блокирует входы элементов И-НЕ 5 и . Длительность промежутка времени, в течение которого компенсируется сигнал источника напряжения-сомножителя 7, равна Л,зм ,Uy, Таким образом длительность этого промежутка времени пропорциональна произведению двух входных напряжений-сомножителей. Этот временный интервал выделяется триггером 24, инвертирующим элементом 17 и дополнительным элементом И-НЕ 19. С инверсного выхода триггера 24 на продолжительность этого временного интервала на блокирующий вход выходного счетчика 30 поступает сигнал разрещения счета. Количество импульсов, поступающих от генератора эталонной частоты -13, пропор ционально произведению двух напряжеНИИ-сомножителей. Знак произведения формируется триггером 25 и дополнительным элементом И-НЕ 20. Opji поступлении сигнала с выхода нуль-оргЪна 2 устанавливается в положение «1 триггер 23, сигнал с которого поступает на элемент И- НЕ 20. На другой вход этого элемента сигналы поступают с прямого выхода триггера 25. При умножении напряжений одинаковой полярности за один цикл умножения на счетный вход триггера 25 приходят два импульса, поэтому к моменту компенсации на прямом выходе триггера 25 присутствует «О, а на выходе элемента И-НЕ 20 «i, которая соответствует положительному знаку произведения. Нри умножении напряжений разной полярности, за один цикл умножения на счетный вход триггера 25 приходит один импульс, поэтому на прямом выходе триггера 25 присутствует «1, а на выходе элемента И-НЕ 20 «О, который соответствует отрицательному знаку произведения.

После завершения цикла умножения блок управления 14 выдает сигнал на включение блока коррекции., дрейфа 32, благодаря-чему компенсируются нестабильности интегратора / и нуль-органа 2.

Таким образом, предложенное устройство можно использовать в качестве ч«тырехквадратногб множительного устройства, что означает расширение диапазона величин перемыкаемых напряжений.

Формула изобретения

Аналого-цифровое множительное устр;ОЙство, содержащее ип егратор, выход которого соединен со входом нуль-органа, первый вход интегратора подключен а одному выводу источника эталонного напряжения, второй и третий входы интегратора, присоединены к выходам соответственно первого п второго ИСТОЧНИКОВ напряжений-сомножителей, четвертый вход интегратора -соединен со вторым выводом источника эталонного напряжения, первый, второй, третий и четвертый управляющие входы интегратора . через соответствующие ключевые элементы подключень к щине нулевого потенциала, выход нуль-органа через блок коррекции дрейфа соединен с дополнительным входом интегратора, в з1ход нуль-органа присоединен к первому входу первого элемента И-НЕ, второй вход ноторого соедине;; со вторым входом второго элемента И-НЕ, трЬтий элемент И-НЕ, генератор эталонной частоты, блок управления, реверсивный счетчик и блок задержки, отличающеес я тем, что, с целью расширения диапазона входных напряжений-сомножителей, в него введены инвертирующие элементы, триггеры, дополнительные элементы И-НЕ и выходной счетчик, причем выход нульорта на через первый инвертирующий элемент соединён с первым входом первого дополнительного элемента И-НЕ, второй вход которого подключен к вь1ходу нульоргана, выход первого дополнительного элемента И-НЕ присоединен к первому входу первого триггера, а через второй инвертирующий элемент подключен к первому входу второго триггера, выход которого соединен с управляющим входом выходного счетчика, выход первого триггера присоединен к первым входам второго и третьего дополнительных элементов И-НЕ, выход первого элемента И-НЕ соединен с первым входом второго элемента И-НЕ, выход которого подключен к управляющему входу первого ключевого элемента и входу третье о триггера, выход которого присоединен ко второму входу третьего дополнительного элемента , выход которого является

выходом устройства, выход четвертого триггера соединен со вторыми входами первого элемента И-НЕ и второго дополнительного элемента И-НЕ, выход которого подключен ко второму входу второго триггера, первый и второй входы первого дополнительного элемента И-НЕ соединены соответственно с первым и вторым входами четвертого триггера, выход пятого триггера подключен ж управляющему входу второго ключевого элемента, вь1ходы реверсивного счетчика присоединены ко входам четвертого гдонолнительного элемента И-НЕ, выход которого соединен с третьими входами четвертого, пятого и шестого триггеров, выход шестого триггера подключен к блокирующему входу реверсивного счетчика, первый выход седьмого- триггера присоединен ко входу «Счет вперед реверсивного счетчика и первому входу пятого дополнительного эл.емента И-НЕ, второй выход седьмого триггера подключен ко входу «Счет назад реверсивного счетчика, счетный вход, которого соединён со счетным входом выходного счетчика и первым выходом генератора эталонной частоты, второй выход которого подключен к счетному входу блока управления, первый выход которого присоединен к управляющему входу третьего ключевого элемента, второй выхоЬ блока управления подключен к первому входу третьего . элемента И-НЕ и первым входом щестого и седьмого триггеров, второй вход третьего элемента И-НЕ

соединен с входом установки в исходное состояние, устройства, выход третЬего элемента И-НЕ присоединен к входам .установки в исходное состояние всех триггеров, блока управления, реверси.вного и выходного счетчика, третий выход блока управления подключен ко второму входу пятого дополнительного элемента И-НЕ, выход которого соединен со вторым входом пятого триггера, а через блок задержки со вторым входом седьмого триггера, четвертый и пятый выходы блока управления присоединены соответственно к четвертому входу четвертого триггера и управляющему входу блока коррекции

дрейфа, выход первого элемента И-НЕ подключен к управляющему входу четвертого Ключевого элемента, выход первого дополнительного элемента И-НЕ соединён с третьим входом пятого дополнительного

элемента И-НЕ.

Источники информации, принятые во внимание при экспертизе:

. Авторское свидетельство СССР № 631936, кл. О 06 G7/16, 1977.

2. Авторское свидетельство СССР № 449445, кл. Н 03 К 13/20, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностный интегратор | 1980 |

|

SU900283A1 |

| Множительно-делительное устройство | 1980 |

|

SU900294A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1800616A1 |

| Способ интегрирующего аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1381709A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Преобразователь величины мощности и действующего значения напряжения в цифровой код | 1986 |

|

SU1404952A1 |

| Логарифмический преобразователь отношения сигналов | 1978 |

|

SU723602A1 |

| Множительно-делительное устройство | 1979 |

|

SU1023344A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Устройство преобразования сигнала с датчика | 1989 |

|

SU1651364A1 |

Авторы

Даты

1980-10-07—Публикация

1978-10-11—Подача