(54) СПОСОБ УМНОЖЕНИЯ ДВУХ СИГНАЛОВ

Изобретение относится к области измерительной и вычислительной техники. Известны способы умножения двух сигналов, использующие принцип двой ного интегрирования 1 . Общим недостатком таких способов является то, что произведение входных сигналов получается как рёзультат двух последовательных операций (интегрирования одного из сомножителей в течение определенного време ни и разряд интегратора постоянным током). Причем мерой величины произ ведения служит время разряда интегратора. Наличие двух разнесенных во врем ни операций не позволяет непосредст венно получить произведение двух Сигналов в виде пропорционального ему периода следования импульсов (между периодами следования, несущими полезную информацию, располагаются интервалы времени, не свя занные с произведением). Период Т между двумя соседними ментами начала заряда интегратора тоит из времени его заряда и врем ни его разряда ,-vtp. При этом произведению входных сигалов X, у пропорционален интервгш . Интервалtj связан не с прдизведением, а только с одним из сомножителей, поэтому наличие его в сумме вносит методическую ошибку произведения. Наиболее близким техническим решением является способ умножения двух сигналов 2 . Этот рпособ предназначен для случая, когда один из сомножителей представлен в виде интервала времени, а другой - в виде напряжения (или может быть преобразован в напряжение) . Способ заключается в том, что сомножитель, представленный напряжением, интегрируется в течение интервала времени, пропорционального второму сомножителю. Когда закончится интервал времени, представляющий второй сомножитель, начинается разряд интегратора с помощью сигнала, представленного напряжением, полярность которого противоположная полярности проинтегрированного сигнала. 3jaTeM измеряется интервал времени, в течение которого интегратор разряжается до нуля, и по Нейу судят о величине произведения. -----Согласно описанному рпособу можно получить результирующий сигнал в виде пропорциональных произведению отрезков времени, интервалы между которыми не несут полезной информации. Однако, очень часто бывает необходимость соединения множительного устройства с блоком, воспринимающим только периодический сигнал. По рассматриваемому способу для получения выходного сигнала в виде частоты потребовались бы дополнительные преобразования.

Целью изобретения является повышение точности путем получения непрерывного потока измеряемых интервалов времени. .

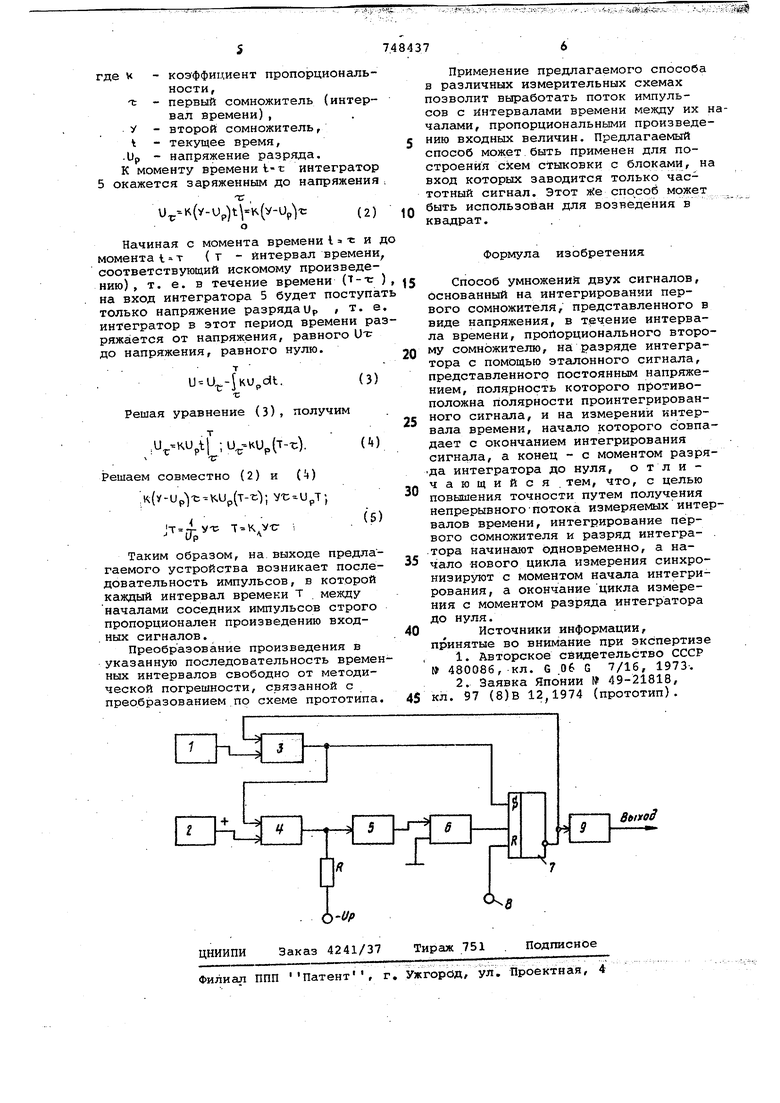

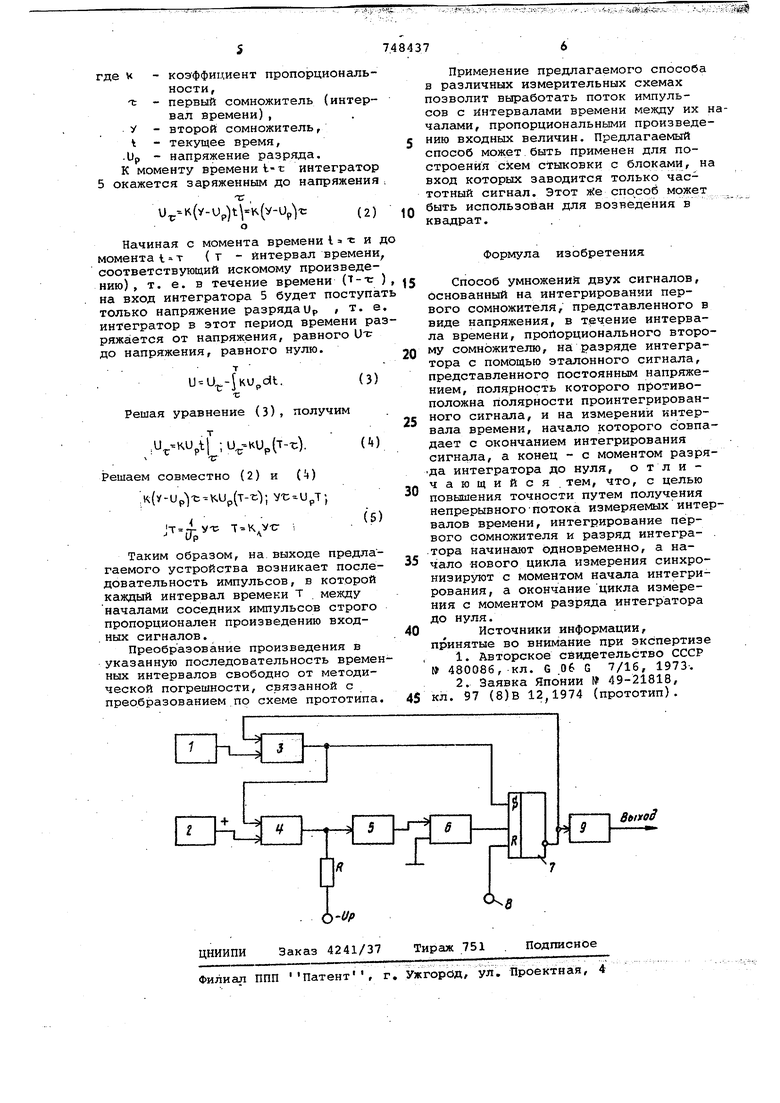

Цель достигается тем, что в способе умножения двух сигналов, основанном на интегрировании первого сомножителя, представленного в виде напряжёнйй, в течение интервала времени, пропорционального второму сомножителю, на разряде интегратора с помощью эталонного сигнала, представленного :постоянным напряжением, полярность которого противоположна полярности проинтегрированного сигнала, и на измерении интервала времени, начало которого совпадает с окончанием интегрирования сигнала, а конец с моментом разряда интегратора до нуля, интегрирование первого сомножителя и разряд интегратора начинают одновременно, а начало нового цикла измерения синхронизируют с моментом начала интегрирования, а окончание цикла измерения - с моментом разряда интегратора до нуля. Hai чертеже приведена блок-схема устройства, в котором может быть осуществлен предлагаемый способ умнжения.

Блок-схема содержит источник 1 пвого сомножителя (У-) , источник 2 второго сомножителя (У ), преобразователь 3 сигнала ; .во временной интервал tr , ключ 4, интегратор 5, схему сравнения б, триггер 7, источник 8 сигналов первоначальной устанки триггера, фЪрмиров&тель 9.

Источник 1 первого сомножителя соединен с преобразователем 3 (

; источник 2 второго сомножителя (V ) соединен с ключом 4, с которым связан также и выход преобразователя 3 Со входом интегратора 5 соединен кл 4 и цепь разряда (сопротивлениеR ). Пос-кольку схема построена на принципе одновременного заряда и разряда интегратора, величина напряже.ния разряда (J р. ) должна быть 1меньше минимального значенияпер-. вого сомнр чсителя. Выход интегратора

„.§.. .н со схемой сравнения (нульрргана) 6, соединенной с нулевым

748437

установочным, входом триггера 7. Единичный установочный вход триг гера 7 связан с выходом преЪбразователя 3. Нулевой выход триггера 7 соединен со входами преобразователя 3 И формирователя 9. 5 Работ а ёт cxieMa следующим образом.

В схеме постоянно действует напрйжение цепи разряда -Up . Пусть в результате предшествующего цикла., преобразования интегратор 5 разря0 дился до нуля. Тогда сработает схема сравнения 6 и ее выходной сигнал установит триггер 7 по нул вому установочному входу в положение О. С инверсного выхода триггера

5 7 сигнал по цепи синхронизации запустит преобразователь 3.

Преобразователь 3 будет оставаться включенным в течение времени -с , пропорционального сомножителю х. С

Q выхода преобразователя 3 сигнал поступит на ключ 4, откроет его и удержит в таком состоянии в течение времени -с . Этот же сигнал уста1новит триггер 7 по единичному установочному входу .в положение 1. При

открытом ключе 4 .потенциал второго

сомножителя ( У ) заряжает интегратор 5 в течение временит . Поскольку напряжение разряда -L/p действует постоянно, одновременно с зарядом

0 интегратора 5 происходит и его разряд напряжением. По окончании времени т: снимается потенциал с единичного установочного входа триггера 7, за- Кроется ключ 4 и прекратится-заряд

5 интегратора 5, аНа его входе будет продолжать действовать только напряжение разряда. Как только интегратор 5 разрядится до нуля, произойдет срабатывание схемы сравнения 6, выходной

о сигнал которой установит триггер в нулевое положение. (Далее процесс повторяется) . - . .

Для координации первоначалбного запуска схемы на нулевой установоч- ч ный вход триггера может подаваться

сигнал от источника 8 сигналов первоначального пуска.

С выхода триггера 7 сигналы поступают на вход формирователя 9, с выхода которого снимается сигнал, прю0 порционалбный произведению.Vr.

Получаемый на выходеформирователя 9 полезный сигнал представляет, собой временный интервал между началами его выходных импульсов. То,

5 что каждый временный интервал между началами двух соседних импульсов на выходе формйроватёля 9 пропорционален Произведению доказывается следующим образом.

Начиная с момента времени f я О интегратор 5 заряжается напряжением V в течение времени t . Текутдёе значениена пряжения и на выходе интегратора выражается как

(y-Up)dt, .(1)

Авторы

Даты

1980-07-15—Публикация

1978-06-27—Подача