1

Изобретение относится к вычислительной технике, может быть использовано в составе контрольно-измерительных систем и систем автоматического управления.

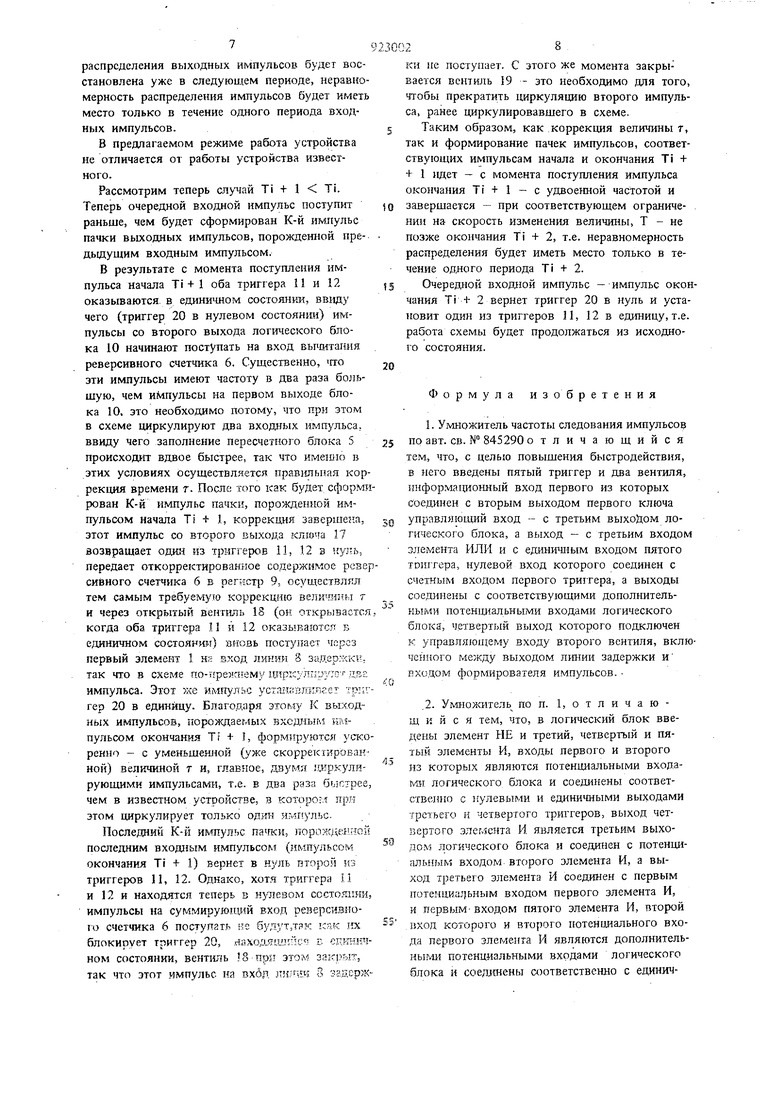

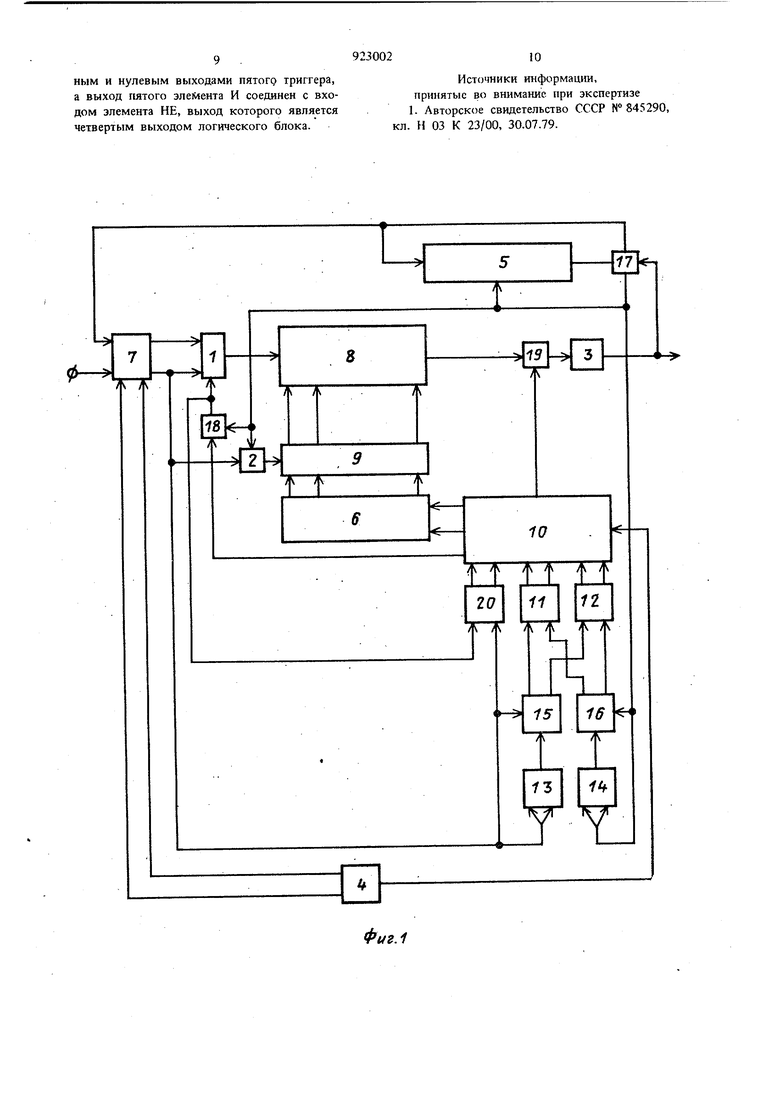

По основному авт. св. № 845290 известен умножитель частоты следования импульсов, содержащий реверсивный счетчик импульсов, и блок разделения, элемент ИЛИ, регистр, логический блок, триггеры, ключи, линию задержки, включенную между выходом элемента ИЛИ и входом формирователя импульсов, выход которогосоединен с импульсным входом первого ключа, первый выход которого соединен со счетным, а второй - с обнуляющим входами пересчетного блока, подключенного выходом к управляющему входу первого ключа, генератор импульсов, выход которого соединен с импульсным входом логического блока, выходы которого подключены к входам сложения и вычитания реверсивного счетчика импульсов, а тактовые выходы - к тяк-товым входам блока разделения , первый информационный вход которого подключен к входной тине, второй информационный входк счетному входу пересчетного блока, а первый выход - к первому входу первого элемента ИЛИ, второй выход - ко второму входу первого элемента ИЛИ, импульсному входу третьего ключа, счетному входу первого триггера и первому входу второго элемента ИЛИ, второй вход которого соединен с обнуляющим входом пересчетного блока, импульсным входом четвертого ключа и счетным входом второго триггера, а выход - с управляющим входом регистра, входы которого соединены с разрядными выходами реверсивного счетчика импульсов, а выходы - с управляющими входами линии задержки,. при этом выходы, первого и второго триггеров соединены с управляющими входами соответственно третьего и четвертого ключей, подключенных выходами соответственно к единичным и нулевым входам третьего и четвертого триггеров, выходы которых подключены к потенциальным входам логического блока, содержащего элемент ИЛИ, линию задержки, первый и второй элементы И, выходы которых, являясь выходами логического блока, соединены соответственно со входами сложения и вычитания реверсивного счетчика импульсов, импуль сный вход логического блока соединен с импульсным входом первого элемента И и через линию задержки и непосредственно с первым и вторым входами элемента ИЛИ, выход которого соединен с импульсным входом второго элемента И, при этом потенциальные вхо ды первого и второго элемента И, являются потен1Д1альными входами логического блока и соединены соответственно с нулевыми и единичными входами третьего и четвертого триггеров 1. Недостатком известного устройства является низкое быстродействие в том, случае, когда Ti +1 Ti (где Ti i-ый интервал между вход ными импульсами устройства ,2 ..). Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в умножитель частоты следования импульсов, содержащий реверсивный счетчик импульсов, линию задержки, вход которой соединен с вы ходом элемента ИЛИ, формирователь импульсов, выход, которого соединен с импульсным входом ключа, первый выход которого сое. динен со счетным, второй выход - с обнуляющим входами пересчетного блока, а управляющий вход - с выходом пересчетного блока, блок разделения, дополнительный элемент ИЛИ, регистр, логический блок, триггеры, дополнительные ключи и генератор импульсов, выход которого соединен с импульсным входом логического блока, первый и второй выходы которого подключены к входам сложения и вычитания реверсивного счетчика импул сов, а тактовые выходы - с тактовыми входами блока разделения, первый информационный вход которого подключен к входной шине, второй информационный вход - к счетному входу пересчетного блока, а первый выход - к первому входу элемента ИЛИ, второ выход - ко второму входу элемента ИЛИ, им пульсному входу первого дополнительного ключа, счетному входу первого триггера и первому -входу дополнительного элемента ИЛИ второй вход которого соединен с обнуляющим входом пересчетного блока, импульсным входом второго дополнительного ключа и счет ным входом второго триггера, а выход - с управляющим входом регистра, входы которого соединены с разрядными выходами ревер сивного счетчика импульсов, а выходы - с управляющими входами линии задержки при этом выходы первого и второго триггеров со единены с управляющими входами соответственно первого и второго дополнительных ключей, выходы первого дополнительного клю ча соединены с единичными, а. выходы второго дополнительного ключа - с нулевыми вхо4дами третьего и четвертого триггеров, выходы которых подключены к потенциальным входам логического блока, при логический блок содержит элемент ИЛИ, линию задержки и первый и второй элементы. И, выходы которых являясь первым и вторым выходами логического, блока соединены соответственно со входами сложения и вычитания реверсивного счетчика импульсов, импульсный вход логического блока соединен с импульсным входом первого элемента И и через линию задержки и непосредственно с первым и вторым входами элемента ИЛИ, выход которого соединен с импульсным входом второго элемента И, введены пятый триггер и два вентиля, информаищонный вход первого из которых соединен со вторым выходом первого ключа, управляющий вход - с третьим выходом логического блока, а выход - с третьим входом элемента ИЛИ и с единичным входом пятого триггера, нулевой вход которого соединен со счетным входом первого триггера, а выходы соединены с соответствующими дополнительными потенциальными входами логического блока, четвертый выход которого подключен к управляющему входу второго вентиля, включенного между выходом линии задержки и входом формирователя импульсов, а в логический блок введены элемент НЕ, третий, четвертый и пятый элементы И, входы первого и второго из которых являются потенциальными входами логического блока и соединены соответственно с нулевыми и единичным и выходами третьего и четвертого три1теров, выход четвертого элемента И является третьим выходом логического блока и соединен с потенциальным входом второго элемента И, а выход третьего элемента И соединен с первым потенциальным входом первого элемеН та И и первым входом пятого элемента И, второй вход которого и второго потенциального входа первого элемента И являются дополнительными потенциальными входами логического блока и соединены соответственно с единичным и нулевым выходами пятого триггера, а выход пятого элемента И соеди- , нен с входом элемента НЕ, выход которого является четвертым выходом логического блока. На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема логического блока. Устройство содержит элементы 1,2 ИЛИ, формирователь 3 импульсов, генератор 4 импульсов, блок 5 пересчетный, реверсивный счетчик 6 импульсов, блок 7 разделения им.пульсов во времени, линия задержки 8, регистр 9, блок 10 логический, триггеры 11-14, ключи 15-17, вентили 18, 19, пятый триггер 20. Логический блок 10 состоит из первого 5 и второго элементов И 21, 22, элемента 23 ИЛИ, линии 24 задержки, третьего, четвертого и пятого элементов И 25-27, элемент 28 НЕ. Устройство работает следующим образом, В исходном состоянии блок 5 установлен в нуль, а его коэффициент пересчета задан равным требуемому коэффициенту К умножения частоты следования импульсов, в соответствии с коэффициентом К и периодом Т повторения входных импульсов устанавлива-. ется состояние реверсивного счетчика 6 и совпадающее с ним состояние регистра 9, задающее время задержки т Т/К, необходиг мое для получения равномерного распределения выходных импульсов умножителя триггер И установлен в единичное, а остальные триггеры 12, 13 14 и 20 - в нулевое состояние (при этом импульсы на входы реверсивного счетчика.б не поступают, вентиль 18-закрыт, вентиль 19 открыт), первый выход блока 7 разделения импульсов соединен через ключ 15 с единичным входом триггера 11, а второй выход ключа 17 соединен через ключ 16 - с нулевым входом этого триггера; импульсный вход ключа 17 соединен с его первым выходом, т.е. со счетным входом пересчетного бло ка 5 и вторым информационным входом бло ка 7.. В соответствии с величиной К установлена частота импульсов на выходе генератора 4 импульсов. Первый входной импульс передается тактовым импульсом генератора 4, на первый выход блока 7, т.е. на вход линии 8 через элемент 1, на единичный вход триггера И через ключ 15, на счетный вход триггера 13, нулевой вход триггера 20 и - через элемент 8 на управляющий вход регистра 9. При этом триггеры 11, 20, а также регистр 9 не изменяют своего со стояния,, триггер 13 переходит в единицу, подключая импульсный вход ключа 15 к единичному входу триггера 12. Спустя время г появится импульс на выходе линии 8 он пройдет через открытый вентиль 19 и формирователь 3 и поступит через ключ 17 на счетный вход пересчетного блока 5 и далее через блок 7 и элемент 1 снова на вход линии 8 задержки. Этот импульс буде циркулировать указанным образом по кольцу: выход линии 8 задержки - вентиль 19 - фор мирователь 3 импульсов - ключ 17 - блок 7 разделения импульсов - элемент 1 - вход пи нии 8 задержки, в каждом цикле добавляя единицу к содержимому пересчетного блока 5 Па выходе формирователя 3 импульсов вырабатывается при этом пачка импульсов с п рипдом т. Так будет продолжаться до тех пор пока число импульсов этой пачки (и равное ему числа в пересчетном блоке 5 не достигнет значения К-1. При этом появится единичный сигнал на управляющем входе первого ключа 17, импульсный вход которого окажется соединенным с его вторым выходом. Очередной, а именно К-ый, импульс с выхода формирователя 3 импульсов поступит теперь через ключ 17 на обнуляющий вход пересчетного блока 5, в результате чего циркуляция импульса прекращается, пересчетный блок. 5 возвращается в исходное нулевое состояние; кроме того этот же К-ый импульс через ключ 16 возвратит в нуль триггер 11. Если время т установлено правильно, т.е. момент формирования К-го выходного импульса совпадает во времени с приходом очередного входного импульса, то триггер 12 устанавливается в единицу; и, поскольку состояние триггеров И и 12 по прежнему различны, импульсы на входы реверсивного счетчика 6 не поступают, т.е. время г остается без изменения. Триггер 11 остается в единишом состоянии в интервалах времени между моментами поступления нечетных входных импульсов первого, третьего и т.д.) и моментами появления на выходе формирователя 3 импульсов К-х и.мпульсов пачек, порождаемых соответствующими входными импульсами. Иначе говоря, триггер 11 устанавливается в единицу каждым i-ым (i 1, 3, 5 ... .) входным импульсом и возвращается в нуль последним К-ым импульсом каждой пачки, состоящей из К импульсов, порожденной i-ым входным импульсом. Аналогично работает триггер 12, но с четными входными импульсами. Если Ti + 1 Ti, то К-ый импульс, порожденный импульсом начала Ti + 1 приходит раньще импульса его окончания, т.е. очеррдного входного импульса, в результате в интервале времени между указанными импульсами, длительность которого Ai T Ti + 1 -Ti, оба триггера 11 и 12 оказываются в нулевом состоянии. Ввиду этого импульсы с первого выхода логического блока 10 поступают в течение AIT на суммирующий вход реверсивного счетчика 6, благодаря чему время задержки т изменится ровно на столько, чтобы выполнялось равенство г Ti + 1/К. Изменение времени задержки произойдет, когда очередной входной импульс, поступив через элементы 7 и 8 на управляющий вход регистра 9, передаст в него новое, откорректированное содержимое реверсивного счетчика 6. Таким образом при увеличении периода следования входных импульсов равномерность

распределения выходных импульсов будет восстановлена уже в следующем периоде, неравномерность распределения импульсов будет иметь место только в течение одного периода входных импульсов.

В предлагаемом режиме работа устройства не отличается от работы устройства известного.

Рассмотрим теперь случай Ti + 1 Ti. Теперь очередной входной импульс поступит раньше, чем будет сформирован К-й импульс пачки выходных импульсов, порожденной предыдущим входным импульсом.

в результате с момента поступления импульса начала Ti + 1 оба триггера 11 и 12 оказываются в единичном состоянии, ввиду чего (триггер 20 в нулевом состоянии) импульсы со второго выхода логического блока 10 начинают поступать на вход вьгапания реверсивного счетчика 6. Существенно, что зти импульсы имеют частоту в два раза большую, чем иМпульсы на первом выходе блока 10. это необходимо потому, что при этом в схеме циркулируют два входных импульса. ввиду чего заполнение пересчетного блока 5 происходт- вдвое быстрее, так что имешю в этих условиях осуществляется, правильп.ая коррекция времени г. После того как будет сформирован К-й импульс пачки, порожденной импульсом начала Ti -f- 1, коррекция завершена, этот импульс со второго выхода г лю-га 17 возвращает один из триггеров 11, 12 в нуль, передает откорректированное содержимое реверсивного счетчика б в регистр 9, осуществлял тем самым требуемую коррекцию велкшз-;ы т к через открытый веттшь 18 (он откррз вается когда оба триггера 11 и 12 оказываются Б единичном состоянии) вновь поступает чпрсз первьш элемент 1 нк вход линии 8 задержки, так что в схеме по-ирешйм;/ц.пркулггрзГочДВЕ импульса. Этот же илшульс устализлкягст триггер 20 в единицу. Благодаря этому К выходных импульсов, порождаемых вхсддьпи ii iпульсом окончания ТI -i- 1, формируются у(Л ;орекно - с уменьшенной (уже скорректированной) величиной т и, главное, двумя зшркулирующими импульсами, т.е. в два раза бьстрее, чем в известном устройстве, в котором при этом циркулирует только один .

Последний К-й импульс , порождйиюй последним входным импульсом (импульсом окончания Ti + 1) вернет в нуль второй из триггеров И, 12. Однако, хотя триггера П и 12 и находятся теперь в нулевом состоянии, импульсы на суммирующий вход реверсивного счетчика 6 поступать из будут, г;ак кх блокирует триггер 20, находйшийс Е состоянии, вентиггь 18 при этом закрыт, так что этот импульс на вхбд .iTK;-viK 3 эадсрж30028

кн ie поступает. С этого же момента закрывается вентиль 19 - это необходимо для того, чтобы прекратить вдркуляцию второго импульса, ранее циркулировавшего в схеме.

5 Таким образом, как коррекция величины т, так и формирование пачек имггульсов, соответствующих импульсам начала и окончания Ti + + 1 вдет - с момента поступления импульса окончания Ti + 1 - с удвоершой частотой и

0 заверщается - при соответствующем ограничении нэ скорость изменения величины, Т - не позже окончания Ti + 2, т.е. неравномерность распределения будет иметь место только в течение оддого периода Ti + 2.

3 Очередной входной импульс - импульс окончания Ti + 2 вернет триггер 20 в нуль и установит один из триггеров 11, 12 в единицу, т.е. работа схемы будет продолжаться из исходного состояния.

Формула изобретения

1. Умножитель частоты следования импульсоэ по авт. св. N 845290 отличающийся тем, что, с целью повыщения быстродействия, в него введены пятый триггер и два вентиля, информационный вход первого из которых соединен с вторым выходом первого ключа управляющий вход - с третьим выходом логического блока, а выход - с третьим входом элемента ИЛИ и с единичным входом пятого триггера, нулевой вход которого соединен с счетным входом первого триггера, а выходы соединены с соответствующими дополнительными потенщ1альными входами логического блока, четвертый выход которого подключен к управляющему входу второго вентиля, включенгюго между выходом лшши задержки и Еходо-м формирователя импульсов.

.2. Умножитель по п. 1,отличающ к и с я тем, что, в логический блок введены элемент НЕ и третий, четвертый и пятый элементы И, входы первого и второго нз которых являются потенщ1альными входами логического блока и соединены соответственно с }1улевыми и единичными выходами третьего и четвертого триггеров, выход четвертого элемента И. является третьим выходом -погического блока и соединен с потенциальным входом второго элемента И, а выход третьего элемента И соединен с первым потенаиа;;ьным входом первого элемента И, и первым- входом пятого элемента Р1, второй вход которого и второго 1готенциального входа первого элемента И являются дополнительными потенциальными входами логического блока и соеддшены соответственно с единичным и нулевым выходами пятогр триггера, а выход пятого И соединен с входом элемента НЕ, выход которого является четвертым выходом логического блока.

92300210

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР N 845290, кл. Н 03 К 23/00, 30.07.79.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU845290A1 |

| Селектор кодовых посылок | 1983 |

|

SU1091328A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| УСИЛИТЕЛЬ ВРЕМЯИМПУЛЬСНЫХ СИГНАЛОВ | 1971 |

|

SU312375A1 |

| Устройство преобразования медленноменяющейся частоты в код | 1977 |

|

SU687589A1 |

| Анализатор сопротивления изоляции | 1975 |

|

SU610033A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU907794A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| Устройство для цифрового измерения разности частот электрических колебаний | 1973 |

|

SU495616A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

0-

Фиг. 1

Авторы

Даты

1982-04-23—Публикация

1980-08-08—Подача