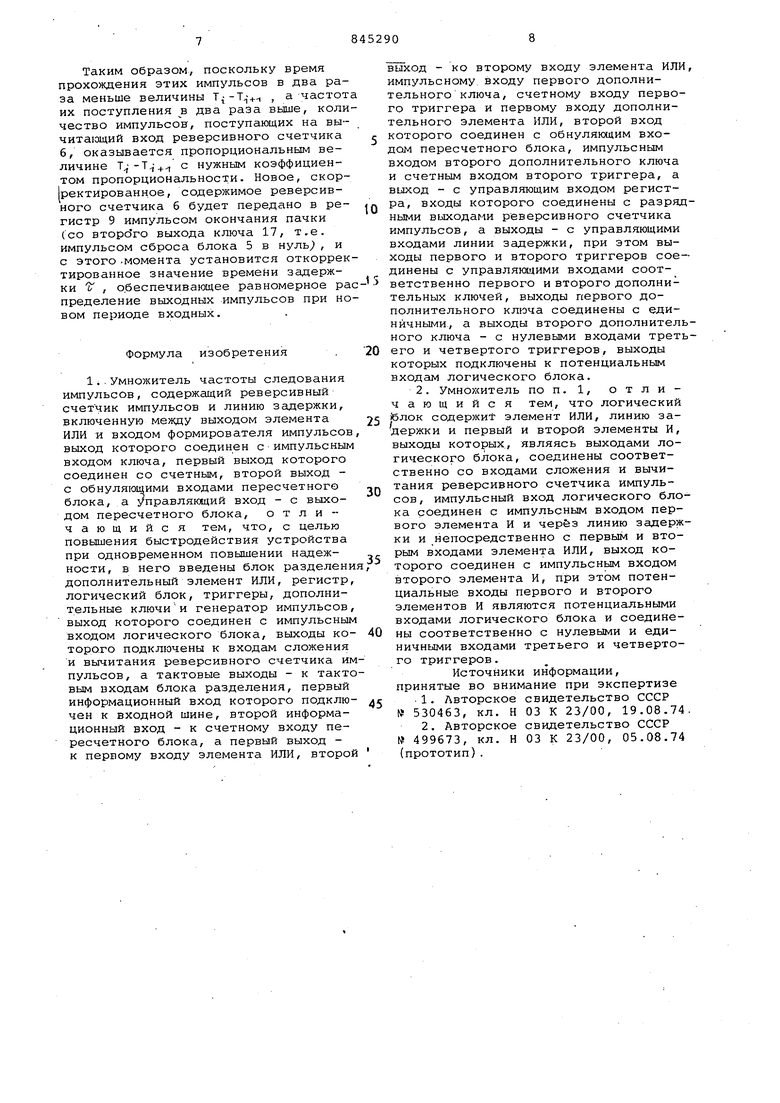

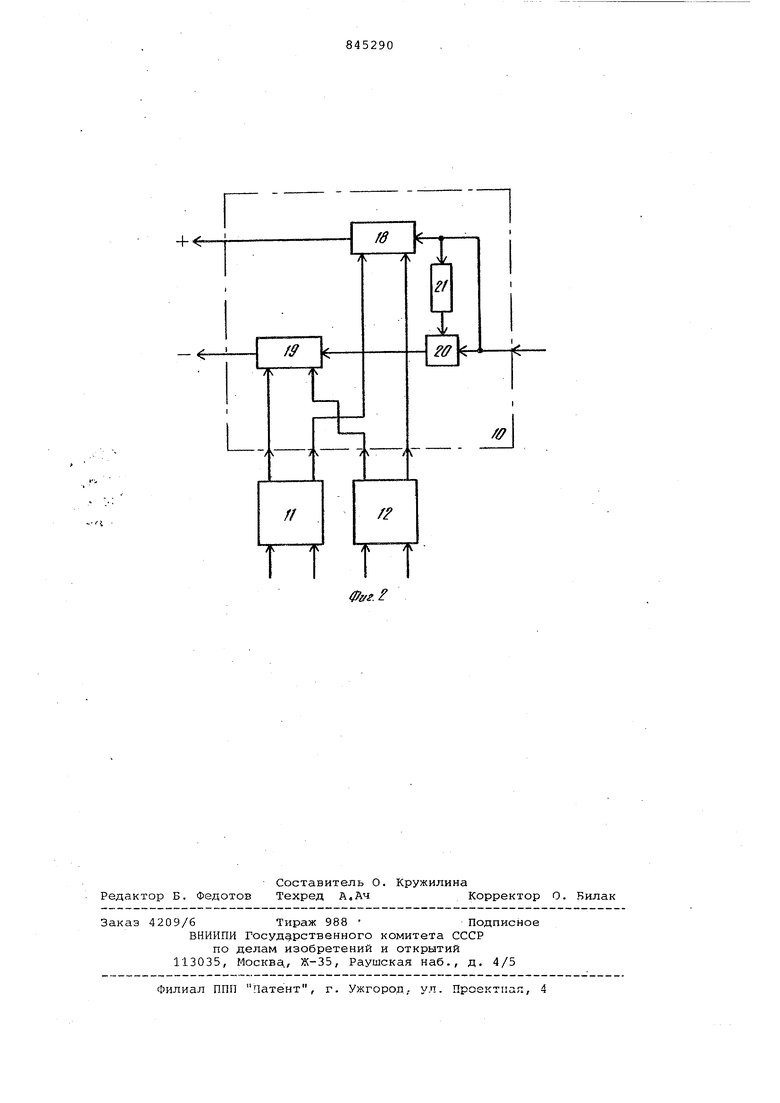

Изобретение относится к вычислительной технике и может быть использовано в составе контрольно-измерител ных систем и систем автоматического управления. Известно пересчетное устройство, содержащее линию задержки, ком1 1утатор, элемент ИЛИ, делитель частоты, триггер, элемент И и счетчик импульсов Г1 . Недостатком данного устройства яв ляется невозможность получения равно мерного распределения выходных импульсов во времени. Наиболее близко к предлагаемому устройство для умножения частоты сле дования импульсов, содержащее ключ, элемент ИЛИ, формирователь импульсов выход которого соединен с первым импульсным входом ключа, импульсный вы ход которого соединен со входом элемента ИЛИ и со счетным входом пересчетного блока, выходы сброса которо го подключены к выходу сброса ключа, два элемента И, реверсивный счетчик импульсов, два генератора строба, ли нию задержки, включенную между элементом ИЛИ и формирователем импульсо управляющие входы {«оторой соединены с выходами реверсивного счетчика импульсов, входы которого через элементы И подключены к выходам генераторов строба, вход первого из которых соединен с одним из входов второго элемента И и обнуляющим входом пересчетного блока, а вход второго с источника импульсов и вторым входом первого элемента И Г27. Недостатки данного устройства невысокое быстродействие и низкая надежность. Целью изобретения является повышение быстродействия устройства при одновременном повышении надежности. С этой целью в умножитель частоты следования импульсов, содержащий реверсивный счетчик импульсов и линию задержки, включенную между выходом элемента ИЛИ и входом формирователя импульсов, выход которого соединен с импульсным входом ключа, первый выход которого соединен с импульсным входом ключа, первый выход которого соединен со счетным, вторйй выход t обнуляющим входами пересчетного блока, а управляющий вход - с выходом пересчетного блока, введены блок разделения, дополнительный элемент ИЛИ, регистр, логический блок, триггеры, дополнительные ключи и генератор импульсов, выход которого соединен с импульсным входом логического блока, выходы которого подключены к входам сло;хения и вычитания реверюивного счетчика импульсов, а тактовые выходы - с тактовыми входами блока раз деления, первый информационный вход которого подключен к входной шине, второй информационный вход - к счетному входу пересчетного блока, а пер вый выход - к первому входу элемента ИЛИ, второй выход - ко второму входу элемента ИЛИ, импульсному входу первого дополнительного ключа, счетному входу первого триггера и первому вхо ду дополнительного элемента ИЛИ, вто рой вход которого соединен с обнуляю щим входом пересчетного блока, импульсным входом второго дополнительного ключа и счетным входом второго триггера, а выход - с управляющим входом регистра, входы которого соединены с разрядньми выходами, реверсивного счетчика импульсов, а выходы с управляющими входами линии задержки. Выходы первого и второго триггеро соединены с управляющими входами соответственно первого и второго допол нительных ключей, выходы первого дополнительного ключа соединены с единичными, а выходы второго дополнительного ключа - с нулевыми входами третьего и четвертого триггеров, выходы которых подключены к потенциаль ным входам логического блока, содержащего второй элемент ИЛИ, линию задержки и первый и второй элементы И, выходы которых, являясь выходами логического блока, соединены соответственно со входами сложения и вычитания реверсивного счетчика импульсов . Импульсный вход логического блока соединен с импульсным входом первого элемента И и через линию задержки и непосредственно - с первым и вторым входаг1И элемента ИЛИ, выход KOtoporo соединен с импульсным входом второго элемента И. Потенциальные входы первого и второго элементов И являются потенциальными входами логического блока и соединены соответственно с нулевыми и единичными входами третьего и четвертого триггеров На фиг. 1 представлена структурна электрическая схема умножителя часто ты 4дедования импульсов;, на фиг. 2 структурная электрическая схема логического блока. Умножитель частоты следования импульсов содержит элементы ИЛИ 1, 2, формирователь 3 импульсов, генератор 4 импульсов, пересчетный блок 5, реверсивный счетчик б импульсов, бло 7 разделения импульсов во времени, линию задержки 8, регистр 9, логичес кий блок 10, триггеры 11-14, ключи 15-17, Логический блок содержит элементы И 18, 19, элемент ИЛИ 20, линию задержки 21. Пусть входные импульсы следуют с периодом Т, а , пусть очередной период Т-2. входных импульсов оказывается больше предыдущего, т.е. последний импульс пачки, порожденной предыдущим входным импульсом, формируется раньше прихода очередного входного импульса, и равномерность распределения выходных импульсов нарушается. Для сохранения этой равномерности необходимо обеспечить равенство . г tuc г к it - 1 (здесь дТ , д С -) , т.е. увеличить время задержки линий задержки 2 пропорционально разности ,)Если же Т Т , т.е. очередной входной импульс приходит раньше формирования последнего импульса пачки выходных, порожденных предыдущим входным импульсом, для равномерного распределения выходных импульсов следует уменьшить время задержки линий задержки 2 на величину, пропорциональную разности . Существенно, что коэффициент пропорциональности равен при этом 1/К, т.е. определяется коэффициентом умножения частоты (.его величина регулируется изменением частоты импульсов на корректируюо1ем выходе генератора импульсов 4) . Именно такая коррекция времени задержки реализуется в предлагаемом устройстве путем добавления в .реверсивный счетчик б числа импульсов, пропорционального величине (Т,-Т)/К в случае , и величине (Т -Т )/К в случае Т,Т . В исходном состоянии блок 5 установлен в нуль и задан коэффициент пересчета, равный требуемому коэффициенту умножения частоты. В соответствии с этим коэффициентом и периодом Tg повторения входных импульсов устанавливается состояние реверсивного счетчика 6 и совпадающее с ним состояние регистра 9, время задержки, необходимое для равномерного распределения выходных импульсов умножитель, триггер 11 устанавливается в единичное, а триггеры 12-14 - у нулевое состояние (при этом импульсы на входы реверсивного счетчика 6 не поступают; , первый выход блока 7 соединен через ключ 15 с единичным входом триггера 11, а второй выход ключа 17 через КЛЕОЧ 16 - с нулевым входом этого триггера. В соответствии с величиной К устанавливается частота импульсов на корректирующем выходе генератора 4. Первый входной импульс, поступив на первый информационный вход блока 7, передается импульсом с первого та тового выхода генератора 4 на первый выход блока 7, т.е. на вход линии задержки 8 (через элемент 1) , на еди ничный вход триггера 11 (через ключ 15) , а также через элемент 2 - на уп равляклдий вход регистра 9. Триггер 11 и регистр 9 при этом остаются в исходном состоянии. Спустя время Т импульс с выхода л нии задержки 8 поступает на вход фор мирователя 3., с выхода которого - че рез ключ 17 - на счетный вход блока и через блок 7 и элемент 1 - снова н вход линии задержки В. Этот импульс будет циркулировать указанным образом, формируя пачку выходных импульсов с интервалами IX, до тех пор, пок число на блоке 5 не достигнет величины К-1, При этом на его выходе появится единичный сигнал и очередной т.е. К-тый импульс с выхода формирователя 3 поступит теперь на второй выход ключа 17, т.е. возвратит блок 5 в нуль, а также установит в нуль через ключ 16 - триггер 11. Если время i; .установлено правильно, момент формирования К-того выходного импульса т,е. импульса на втором выходе ключа 17) совпадает во времени с приходом очередного входного, импульса, устанавливающего в единицу триггер 12 (так как триггер 13 был установлен в единицу) . Таким образом, состояния триггеров 11 и 12 по-прежнему оказываются различными, т.е. импульсы на входы реверсивного счетчика б не поступают. Триггер 11 находится в единичном состоянии в интервалах между моментами поступления нечетных входных им пульсов (первого, третьего и т.д. и моментами появления на вьоходе устройства К-тых импульсов - пачек, поро)хденных соответствующими нечетными входными импульсами. Иначе говоря триггер 11 устанавливается в единицу каждым i-тым входным импульсом (, 3, 5...) и опрокидывается в ну последним импульсом каждой пачки, по рожденной i-тым входным импульсом. Аналогично рггботает триггер 12, но с четными входными импульсами. Если Т, Т.,, момент возврата в нуль триггера 11 совпадает с моментом установки в единицу триггера 12 и наоборот, т.е. их состояния все время различны, и импульсы на входы реверсивного счетчика не поступают. Пусть теперь f )+ i -s- К-тый импульс i-той пачки приходит раньше чем i+1-й входной импульс. В этом случае в интервале времени Т,- триггера оказываются в нулевом состоянии, ввиду чего импульсы с ,блока 10 начинают поступать на суммирующий вход р€5версивного счетчика Количество этих импульсов пропорционально величине д, благодаря чему (с учетом того, что частота корректирующих импульсов генератора 4 установлена в соответствии с реализуемым коэффициентом умножения К) время задержки т изменится ровно настолько, чтобы выполнялось равенствоС - -Изменение времени задержки произойдет, когда i+1-й входной импульс, поступив через блок 7 и элемент 2 на управляющий вход регист ра 9, передаст в него новое, откорректированное указанным образом, содержимое реверсивного счетчика 6. Таким образом, если период входных импульсов увеличился, то уже в следующем периоде равномерность выходных импульсов будет восстановлена (появится только один интервал между последним импульсом i-той пачки и первым импульсом i+1-й пачки) . Рассмотрим теперь случай, когда Т- . Очередной входной 1+1-й импульс поступает теперь раньше последнего импульса пачки, порожденной предыдущим i-тым импульсом. В результате с момента поступления i+1-го входного импульса и до момента прихода последнего импульса пачки, пороходенной предьщущим i-тым входным импульсом, триггеры 11 и 12 находятся в единичном состоянии. Существенно, что длительность этого интервала времени оказывается в два раза меньше величины Т i4-i - входной импульс поступает в линию задержки 8 и начинает циркулировать в схеме вместе с предыдугцим входным импульсом. Импульсы на счетный вход пересчетного устройства попадают теперь вдвое чаще, благодаря чему число их, недостающее до k, набирается вдвое быстрее, чем в случае отсутствия второго входного импульса, т.е. при циркуляции в схеме одного импульса. Поскольку, как указывалось выше, для равномерного распределения выходных импульсов при сократившемся периоде входных требуется уменьшать время задержки С на величину, пропорциональную разности T, тре буется подать пропорциональное этой разности число импульсов на вычитаю;щий вход реверсивногосчетчика б, причем коэффициент пропорциональности должен быть тот же, что и в случае Т.,Т . Такой алгоритм реализуется следующим образом: с момента установления триггеров 11 и 12 в единичное состояние импульсы, поступаквдие на импульсный вход логического блока 10, проходят на выход элемента 19, т.е. на вычитающий вход реверсивного счетчика 6, как непосредственно, так и через линию задержки 21, т.е. парами. Таким образом, поскольку время прохождения этих импульсов в два раза меньше величины , а частот их поступления JB два раза вьдше, коли чество импульсов, поступающих на вычитающий вход реверсивного счетчика 6, оказывается пропорциональным величине . с нужным коэффициентом пропорциональности. Новое, скор ректированное, содержимое реверсивного счетчика 6 будет передано в регистр 9 импульсом окончания пачки (со второго выхода ключа 17, т.е. импульсом сброса блока 5 в нуль, и с этого.момента установится откоррек тированное значение времени задержки , обеспечивающее равномерное ра пределение выходных импульсов при но вом периоде входных. Формула изобретения 1..Умножитель частоты следования импульсов, содержащий реверсивный счетчик импульсов и линию задержки, включенную между выходом элемента ИЛИ и входом формирователя импульсов выход которого соединен с импульсным входом ключа, первый выход которого соединен со счетным, второй выход с обнуляющими входами пересчетного блока, а Управляющий вход - с выходом пересчетного блока, отличающийся тем, что, с целью повышения быстродействия устройства при одновременном повышении надежности, в него введены блок разделен дополнительный элемент ИЛИ, регистр логический блок, триггеры, дополнительные ключии генератор импульсов выход которого соединен с импульсным входом логического блока, выходы ко торо.го подключены к входам сложения и вычитания реверсивного счетчика и пульсов, а тактовые выходы - к такт вым входам блока разделения, первый информационный вход которого подклю чен к входной шине, второй информационный вход - к счетному входу пересчетного блока, а первый выход к первому входу элемента ИЛИ, второ выход - ко второму входу элемента ИЛИ, импульсному входу первого дополнительного ключа, счетному входу первого триггера и первому входу дополнительного элемента ИЛИ, второй вход которого соединен с обнуляющим входом пересчетного блока, импульсным входом второго дополнительного ключа и счетным входом второго триггера, а выход - с управляющим входом регистра, входы которого соединены с разрядными выходами реверсивного счетчика импульсов, а выходы - с управляющими входами линии задержки, при этом выходы первого и второго триггеров соединены с управляющими входами соответственно первого и второго дополнительных ключей, выходы первого дополнительного ключа соединены с единйчныгли, а выходы второго дополнительного ключа - с нулевыми входами третьего и четвертого триггеров, выходы которых подключены к потенциальным входаии логического блока. 2. Умножитель по п. 1, отличающийся тем, что логический ёлок содержит элемент ИЛИ, линию задержки и первый и второй элементы И, выходы которых, являясь выходами логического блока, соединены соотйетственно со входами сложения и вычитания реверсивного счетчика импульсов, импульсный вход логического блока соединен с импульсным входом первого элемента И и через линию задержки и непосредственно с первым и вторым входами элемента ИЛИ, выход которого соединен с импульсньм входом второго элемента И, при этом потенциальные входы первого и второго элементов И являются потенциальными входами логического блока и соединены соответственно с нулевыми и единичными входами третьего и четвертого триггеров. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 530463, кл. Н 03 К 23/00, 19.08.74. 2. Авторское свидетельство СССР № 499673, кл. Н 03 К 23/00, 05.08.74 (прототип).

ГТ 11

Фг/г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1980 |

|

SU923002A2 |

| Устройство формирования и регистрации путевых параметров для управления шахтной подъемной установкой | 1989 |

|

SU1835383A1 |

| Устройство формирования много-СТупЕНчАТОгО КВАзиСиНуСОидАльНОгОТРЕХфАзНОгО НАпРяжЕНия | 1978 |

|

SU809437A1 |

| Адаптивный цифровой фазометр | 1978 |

|

SU788031A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Цифровой измеритель длительности пачки импульсов | 1980 |

|

SU892412A1 |

| Преобразователь цифровых кодов в скважность импульсов | 1980 |

|

SU886235A1 |

| Анализатор сопротивления изоляции | 1975 |

|

SU610033A1 |

Авторы

Даты

1981-07-07—Публикация

1979-07-30—Подача