(54) УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ

.выходы основного и дополнительного блоков усреднения соединена соответственно с первым и вторым входами дополнительного перемножителя, выход которого соединен с соответствующим входом дополнительного сумматора,

Кроме того, вычислитель выполнен в виде последовательно включенных первого накопителя, блока деления и функционального преобразователя, при этом второй вход блока деления соединен с выходом второго накопителя , входы первого и второго накопителей являются соответственно первым и вторьм входами вычислителя, выходом которого является выход функционального преобразователя; вычислитель может, быть выполнен в виде последовательно включенных сумматора, первогс ключа и элемента ИЛИ, второй вход которого через второй соединен с первым входом сумматора, а второй вход первого ключа соединен с выходом инвертора, вход котоЕЮго соединен с вторым входом второго ключа, при этом первый и второй входы второго ключа являются соответственно первым и вторым входами вычислителя, выходом которог является выход элемента ИЛИ; кроме того, в устройство введен весовой блок, включенный ме;кду входом инвертора и входом су 1матора.

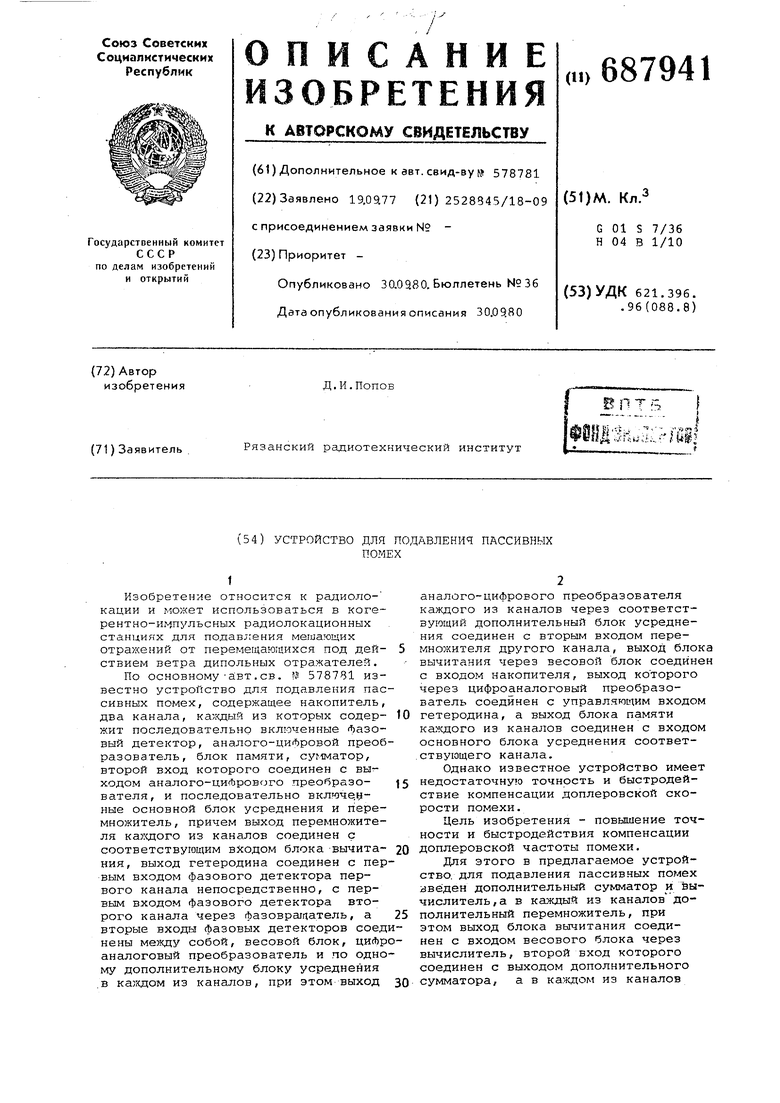

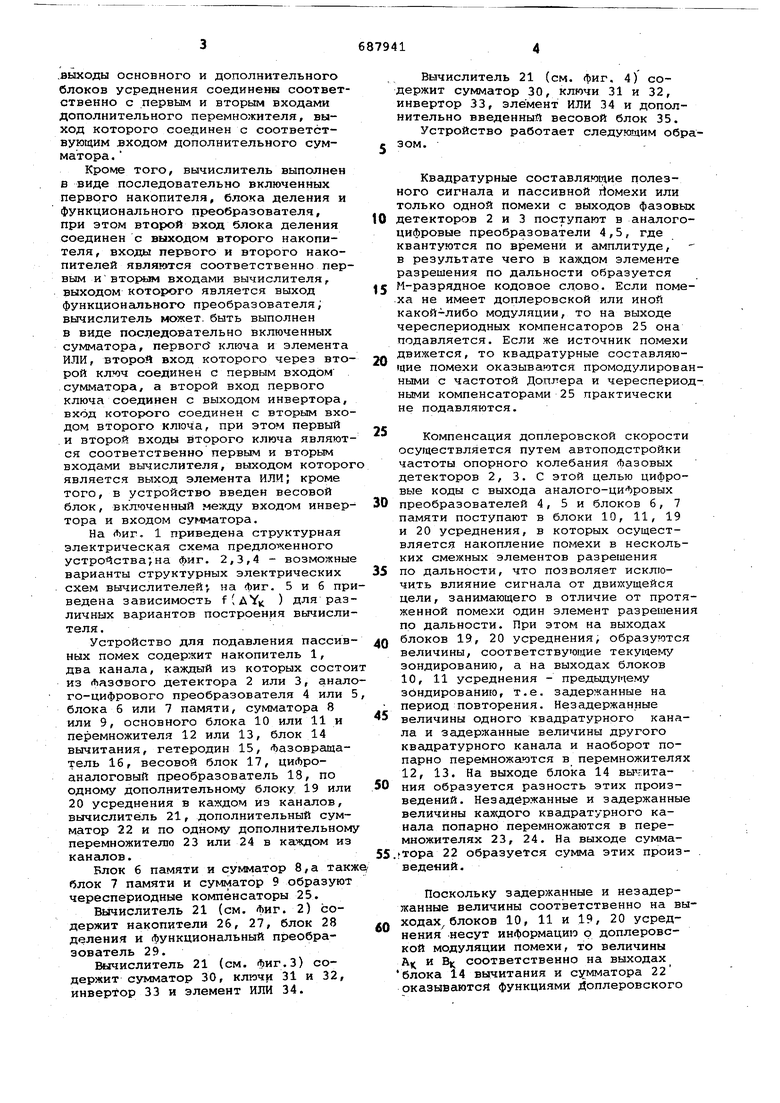

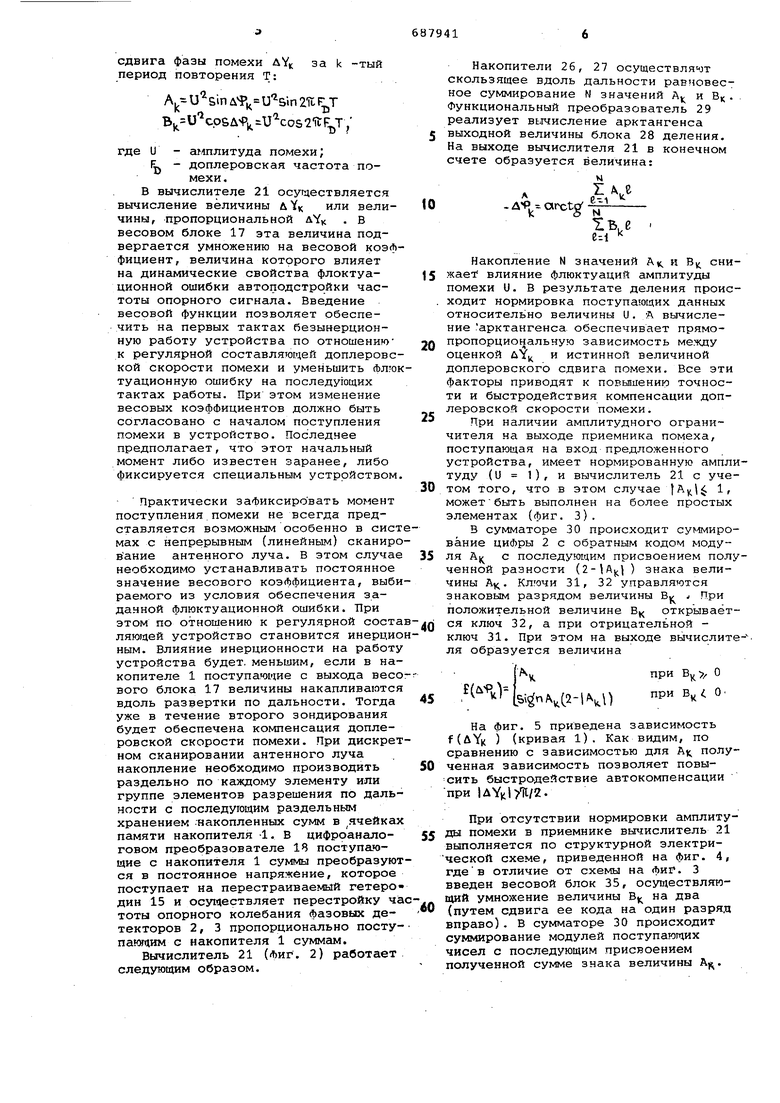

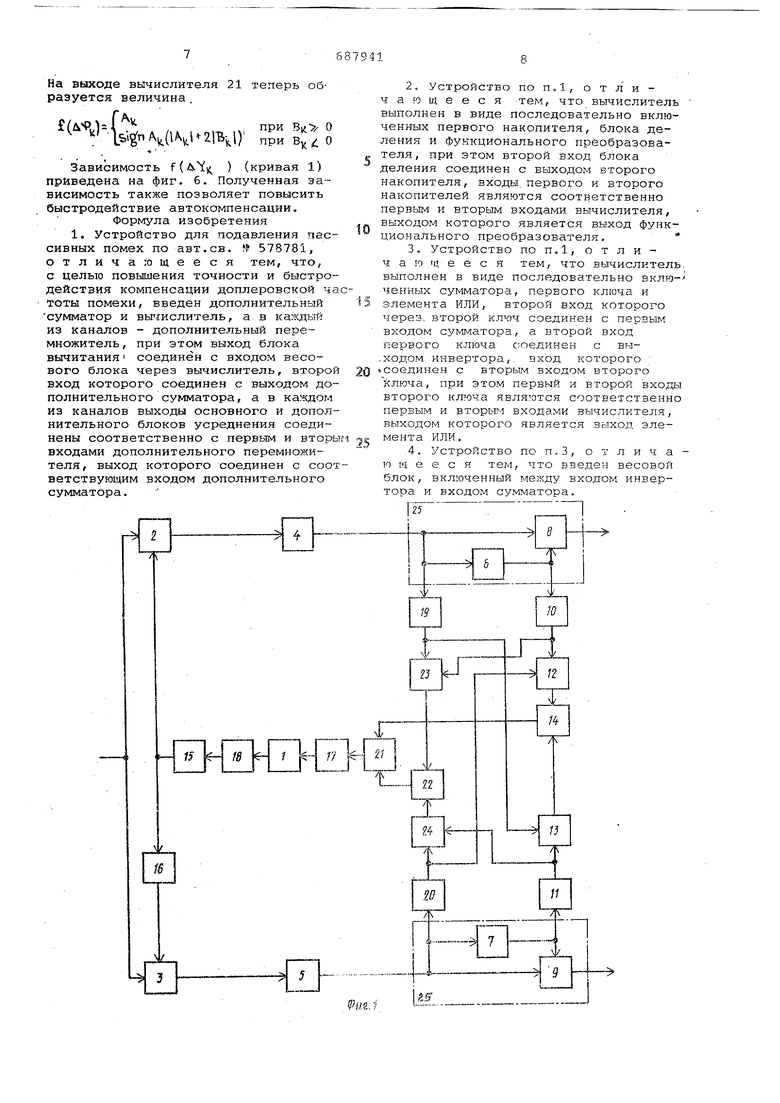

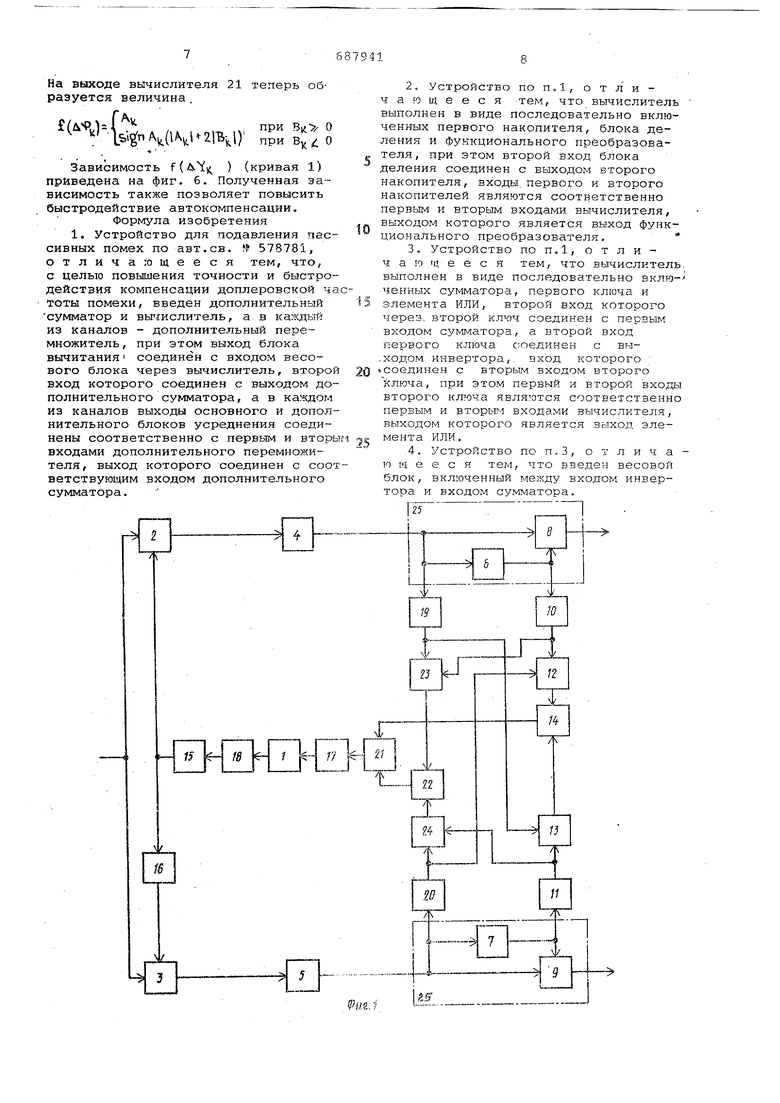

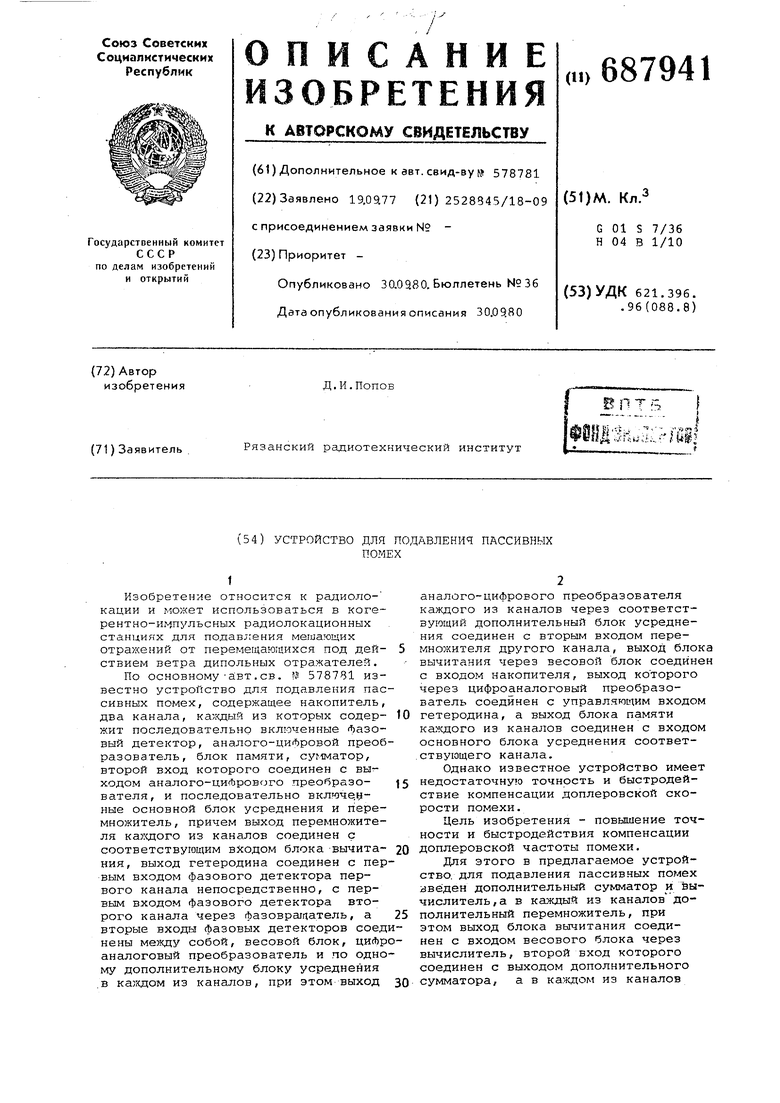

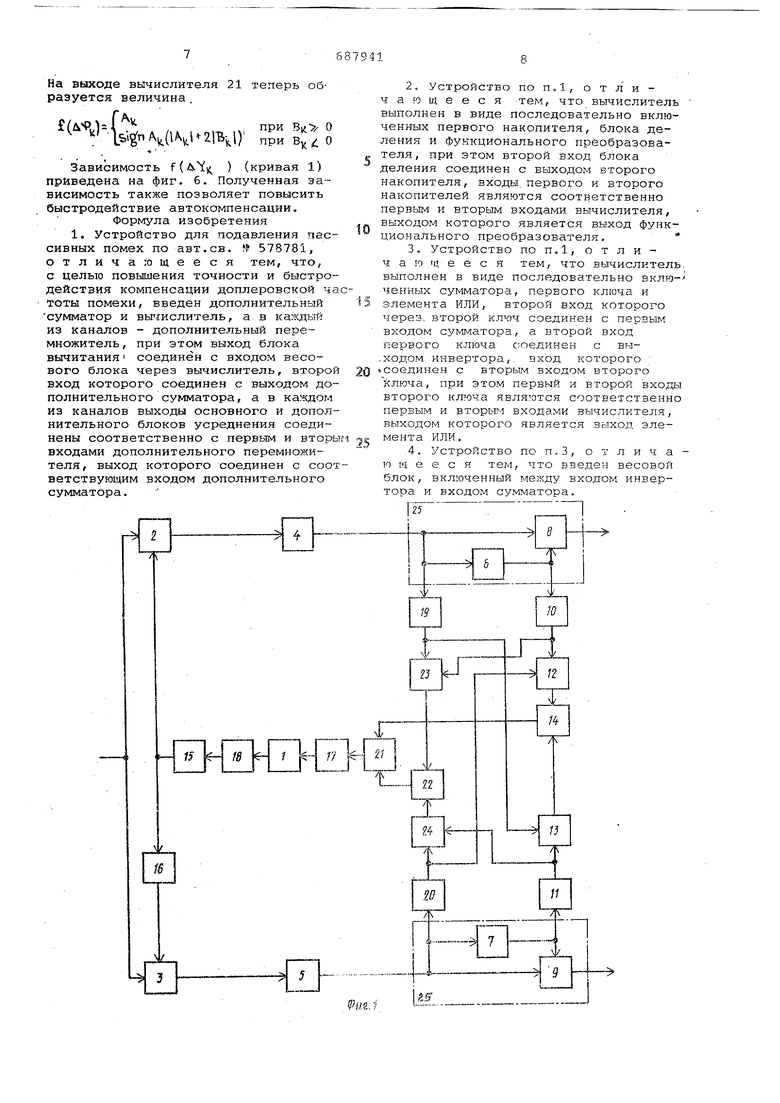

На Лиг, 1 приведена структурная электрическая схема предложенного устройства;на фиг. 2,3,4 - возможные варианты структурных электрических схем вычислителей; на фиг. 5 и 6 приведена зависимость f ДУц ) для различных вариантов построения вычислителя.

Устройство для подавления пассивных помех содержит накопитель 1, два канала, каждый из которых состои из Лавового детектора 2 или 3, аналого-цифрового преобразователя 4 или 5 блока б или 7 памяти, сумматора 8 или 9, основного блока 10 или 11 и перемножителя 12 или 13, блок 14 вычитания, гетеродин 15, Фазовращатель 16, весовой блок 17, циЛроаналоговый преобразователь 18, по одному дополнительному блоку 19 или 20 усреднения в каждом из каналов, вычислитель 21, дополнительный сумматор 22 и по одному дополнительному перемножителю 23 или 24 в каждом из каналов.

Блок 6 памяти и сумматор 8,а такж блок 7 памяти и сумматор 9 образуют череспёриодные компенсаторы 25.

Вычислитель 21 (см. фиг. 2) содержит накопители 26, 27, блок 28 деления и функциональный преобразователь 29.

Вычислитель 21 (см. фиг.3) содержит сумматор 30, ключи 31 и 32, инвертор 33 и элемент ИЛИ 34.

Вычислитель 21 (см. фиг. 4) содержит сумматор 30, ключи 31 и 32, инвертор 33, элемент ИЛИ 34 и дополнительно введенный весовой блок 35.

Устройство работает следующим образом.

Квадратурные составляющие полезного сигнала и пассивной помехи или только одной помехи с выходов фазовы детекторов 2 и 3 поступают в аналогоцифровые преобразователи 4,5, где квантуются по времени и амплитуде, в результате чего в каждом элементе разрешени.я по дальности образуется М-разрядное кодовое слово. Если помеха не имеет доплеровской или иной какой-либо модуляции, то на выходе череспериодных компенсаторов 25 она подавляется. Если же источник помехи движется, то квадратурные составляю|цие помехи оказываются промодулироваными с частотой Доплера и череспериоными компенсаторами 25 практически не подавляются.

Компенсация доплеровской скорости осу цествляется путем автоподстройки частоты опорного колебания фазовых детекторов 2, 3. С этой целью цифровые коды с выхода аналого-ци)ровых преобразователей 4, 5 и блоков 6, 7 памяти поступают в блоки 10, 11, 19 и 20 усреднения, в которых осуществляется накопление помехи в нескольких смежных элементов разрешения по дальности, что позволяет исключить влияние сигнала от движущейся цели, занимающего в отличие от протяженной помехи один элемент разрешени по дальности. При этом на выходах блоков 19, 20 усреднения, образуются величины, соответствующие текущему зондированию, а на выходах блоков 10, 11 усреднения - предыдущему зондированию, т.е. задержанные на период повторения. Незадержанные величины одного квадратурного канала и задержанные величины другого квадратурного канала и наоборот попарно перемножаются в перемножителях 12, 13. На выходе блока 14 вычитания образуется разность этих произведений. Незадержанные и задержанные величины каждого квадратурного канала попарно перемножаются в перемножителях 23, 24. На выходе сумма.гтора 22 образуется сумма этих произведений.

Поскольку задержанные и незадержанные величины соответственно на выходах, блоков 10, 11 и 19, 20 усреднения несут информацию о доплеровской модуляции помехи, то величины А и В| соответственно на выходах блока 14 вычитания и сумматора 22 оказываются функциями Доплеровского

сдвига фазы помехи ДУ за k -тый период повторения Т:

А, и Sin 211 B U cpSAS(-U cos2ii:F T,

где и - агтлитуда помехи;

1 - доплеровская частота помехи .

В вычислителе 21 осуществляется вычисление величины д YK или величины, пропорциональной дУц . В весовом блоке 17 эта величина подвергается умножению на весовой коэффициент, величина которого влияет на динамические свойства флоктуационной ошибки автоподстройки частоты опорного сигнала. Введение весовой функции позволяет обеспечить на первых тактах безынерционную работу устройства по отношению к регулярной составляющей доплеровской скорости помехи и уменьшить флтактуационную ошибку на последующих тактах работы. При этом изменение весовых коэффициентов должно быть согласовано с началом поступления помехи в устройство. Последнее предполагает, что этот начальный момент либо известен заранее, либо фиксируется специальным устройством.

Практически зафиксировать момент поступления помехи не всегда представляется возможным особенно в систмах с непрерывным (линейным) сканирование антенного луча. В этом случае необходимо устанавливать постоянное значение весового коэффициента, выбираемого из условия обеспечения заданной флюктуационной ошибки. При этом по отношению к регулярной состаляющей устройство становится инерционым. Влияние инерционности на работу устройства будет, меньшим, если в накопителе 1 поступающие с выхода весового блока 17 величины накапливаются вдоль развертки по дальности. Тогда уже в течение второго зондирования будет обеспечена компенсация доплеровской скорости помехи. При дискретном сканировании антенного луча накопление необходимо производить раздельно по каждому элементу или группе элементов разрешения по дальности с последующим paздeльны хранением .накопленных сумм в ячейках памяти накопителя -1. В цифроаналоговом преобразователе 18 поступающие с накопителя 1 суммы преобразуются в постоянное напряжение, которое поступает на перестраиваемый гетеродин 15 и осуществляет перестройку чатоты опорного колебания фазовых детекторов 2, 3 пропорционально поступаюгцим с накопителя 1 суммам.

Вычислитель 21 (Фиг. 2) работает следующим образом.

Накопители 26, 27 осуществляют скользящее вдоль дальности равновесное суммирование N значений А и в. Функциональный преобразователь 29 реализует вычисление арктангенса выходной величины блока 28 деления. На выходе вычислителя 21 в конечном счете образуется величина:

ы

А Z e -A-P -arctgrlb

Ть.е е-1

Накопление N значений , и В снижает влияние флюктуации амплитуды

помехи и. В результате деления проис. ходит нормировка поступающих данных относительно величины U. А вычисление арктангенса обеспечивает прямоQ пропорциональную зависимость между оценкой дУ и истинной величиной доплеровского сдвига помехи. Все эти факторы приводят к повышению точности и быстродействия компенсации доплеровской скорости помехи.

При наличии амплитудного ограничителя на выходе приемника помеха, поступающая на вход предложенного устройства, имеет нормированную амплитуду (и 1), и вычислитель 21 с учетом того, что в этом случае f Ау( 1, можетбыть выполнен на более простых элементах (фиг. 3).

В сумматоре 30 происходит cy миpoвание цифры 2 с обратным кодом модуля А( с последующим присвоением полученной разности (2-)А),| ) знака величины . Клгачи 31, 32 управляются знаковым разрядом величины В j При положительной величине В открываётjQ ся ключ 32, а при отрицательной ключ 31. При этом на выходе вычислителя образуется величина

при В О

Y е при В О

5i n C2-|M)

На фиг. 5 приведена зависимость f(uYK ) (кривая 1), Как видим, по сравнению с зависимостью для А, полученная зависимость позволяет повысить быстродействие автокомпенсации при |дУц1Д/2.

При отсутствии нормировки амплитуД помехи в приемнике вычислитель 21 выполняется по структурной электрической схеме, приведенной на фиг. 4, гдев отличие от схемы на фиг. 3 введен весовой блок 35, осуществляющий умножение величины В на два (путем сдвига ее кода на один разряд вправо). В сумматоре 30 происходит суммирование модулей поступающих чисел с последующим присвоением полученной сумме знака величины А. На выходе вычислителя 21 теперь образуется величина . (S)( при В(4 о № (,0 при О Зависимость f(ti.)C ) (кривая 1) приведена на фиг. б. Полученная зависимость также позволяет повысить быстродействие автокомпенсации. Формула изобретения 1. Устройство для подавления пас сивных помех по авт.св. № 578781, отличающее ся тем, что, с целью повышения точности и быстро действия компенсации доплеровской ч tOTH помехи/ введен дополнительный сумматор и вкпислитель, а в калсдый из каналов - дополнительный перемножитель, при этом выход блока вычитания соединён с входом весового блока через вычислитель, второ вход которого соединен с выходом до полнительного сумматора, а в каждом из каналов выходы основного и допол нительного блоков усреднения соединены соответственно с первым и втор входами дополнительного перемножителя, выход которого соединен с соо ветствующим входом дополнительного сумматора. 2.Устройство по П.1, о т л и чающееся тем, что вычислитель выполнен в виде последовательно включенных первого накопителя, блока делеиия и функционального преобразователя, при этом второй вход блока деления соединен с выходом второго накопителя, входы, первого и второго накопителей являются соответственно первым и вторым входами вычислителя, выходом которого является выход функционального преобразователя. 3.Устройство по П.1, о т л и ч а ю Ц е е с я тем, что вычислитель, выполнен в виде последовательно включенных сумматора, первого ключа и элемента ИЛИ, второй вход которого через, второй ключ соединен с первым входом сумгдатора, а второй вход первого ключа соединен с вы,ходом инвертора,, вход которого соединен с вторым входом второго кл.юча, при этом первый и второй входы второго ключа являются соответственно первым и вторым входами вычислителя, выходом которого является выход элемента ИЛИ. 4.Устройство по п,3, о т л и ч а то щ веся тем, что введен весовой блок, включенный между входом, инвертора и входом сумматора. -п

Ak

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1977 |

|

SU711849A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| РЕЖЕКТОРНЫЙ ФИЛЬТР | 1980 |

|

SU934816A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1977 |

|

SU778514A2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1982 |

|

SU1090136A1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ АДАПТИВНОГО РЕЖЕКТИРОВАНИЯ ПОМЕХ | 2015 |

|

RU2582871C1 |

| АДАПТИВНЫЙ ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТИРОВАНИЯ ПОМЕХ | 2015 |

|

RU2582874C1 |

| УСТРОЙСТВО АДАПТИВНОЙ РЕЖЕКЦИИ ПАССИВНЫХ ПОМЕХ | 1981 |

|

SU1098399A1 |

| ФИЛЬТР РЕЖЕКЦИИ ПАССИВНЫХ ПОМЕХ | 2021 |

|

RU2765852C1 |

9ueJ

f{& Ш

Pue.5

Риъ.

f(fk)

л%

Vuz.ff

Авторы

Даты

1980-09-30—Публикация

1977-09-19—Подача