11

Изобретение относится к автоматик и вычислительной технике и может быт использовано для преобразования напряжения постоянного тока в цифровой код.

Цель Изобретения - повышение точт ности и надежности за счет упрощения устройства.

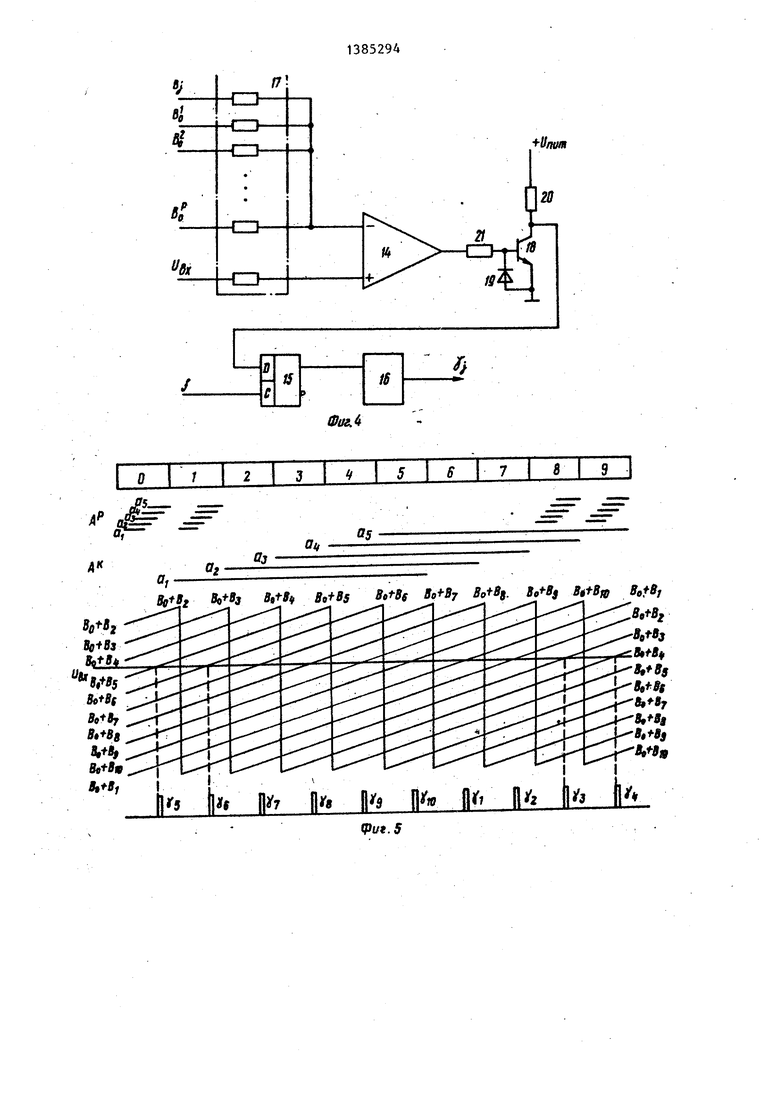

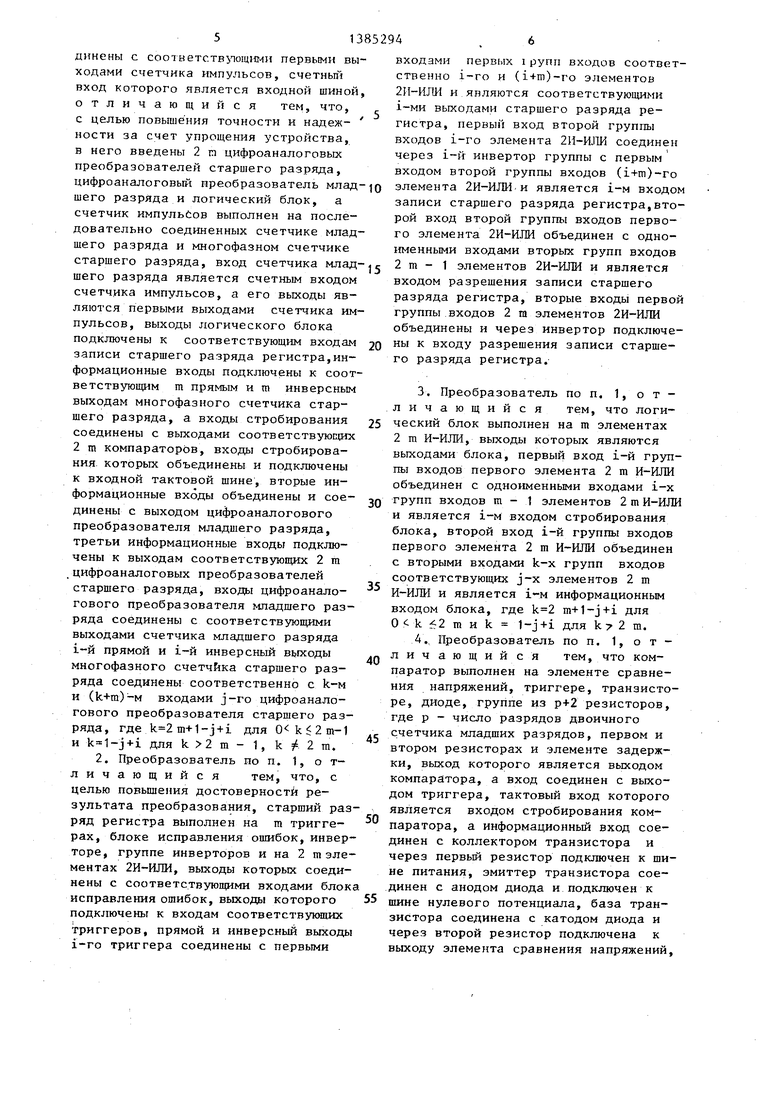

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - схема старших разрядов регистра} на фиг. 3 - схема логического блока; на фиг. 4 - схема компаратора; на фиг.5 диаграммы, поясняющие формирование развертывающих напряжений с помощью цифроаналоговых преобразователей; на фиг. 6 - схема многофазного счетчика старшего разряда.

Аналого-цифровой преобразователь (фиг. 1) содержит счетчик 1 импульсов, выполненный на счетчике младшего разряда и многофазном счетчике старшего разряда, цифроаналоговый преобразователь 2 младшего разряда,

2m цифроаналоговых преобразователей

3старшего разряда, 2 m компараторов 4, элемент ИЛИ 5, логический блок 6 и регистр 7. Старший разряд регистра 7 (фиг. 2) выполнен на m триггерах 8, блоке 9 исправления ошибок, 2т элементах 2И-ИЛИ 10, группе 11 из m инверторов и инверторе 12. Ло:- гический блок 6 (фиг. 3) выполнен на m элементах 2 m И-ИЛИ 13. Компараторы 4 (фиг. 4) выполнены на элементе 14 сравнения напряжений, D-тригге- ре 15, элементе 16 задержки, группе 17 резисторов, транзисторе 18,диоде

20 образующие код счетчика старшего раз ряда в линейно нарастающее напряжени отличаются от цифроаналогового преоб разователя 2 младших разрядов наличи ем преобразователя кодов на его вхо

25 де. Преобразователь кода преобразует код Либау-Крейга в единичный (га - 1) позиционный код и для m 5 может бы

реализован на основе следующих логических соотношений

30

,

l5-

5

4

Ч

1з-

ll

,

а,+а,

Ч

1 а.

5

1 ,

7 l и а.

35

3 5 -9 , г-де ., „ „, прямой и инверсный сигналы i-ro разряда счетчика старших разрядов; 1, - выходной сигнал преобразователя кода. Соединение входов цифроаналоговых преобразователей старшего разряда с выходами счетчика разряда выполняется в соответствии с выражени19 и двух резисторах 20 и 21. Счетчик 40 ем k 2 m + 1 - j + i - для прямых старшего разряда (фиг. 6) выполнен на триггерах 22, группе 23 элементов И и счетном триггере 24.

Аналого-цифровой преобразователь работает следующим образом. 45

Счетчик 1 работает в непрерывном циклическом режиме, суммируя поступающие на его вход импульсы частоты f ех За каждый цикл счетчик импульсов полностью заполняется и возвраща- п етея в нулевое состояние. При этом старший разряд счетчика 1 импульсов выполнен на многофазном счетчике, например в коде Либау-Крейга (фиг. 6). Триггеры 22 счетчика в коде Либау- гг Крейга соединены между собой в кольцо через элементы И группы 23. Вторые входы соответствуюпщх элементов И группы соединены соответственно с.

выходов разряда счетчика k 3 m + + 1 - j + i - для инверсных выходов, где i - номер выхода счетчика старшего разряда, j - номер цифроаналогового преобразователя старшего разряда, k - номер входа j-ro цифроаналогового преобразователя 3 старшего разряда. Если значение k 2 га, то из полученного значения вычитается число кратное 2 т; значение k 2 m указывает на отсутствие связи между данным прямым или инверсным выходом счетчика старшего разряда с входом данного j-ro цифроаналогового преобразователя 3 старшего разряда.

Сигнал с выхода цифроаналогового преобразователя 2 младшего разряда поступает на вторые информационные входы всех 2 m компараторов 4, на

прямым и инверсным выходами счетного триггера 24, вход которого является счетным входом счетчика старшего разряда. Выходами счётчика являются прямые а и инверсные а- , выходы триггеров 22, при этом код числа А представляется в виде последователь1)4 11

ных множеств сигналов с уровнем О

Г

и U и, например, для числа А 3 при основании 10 имеет вид 3 1110000011.

Сигналы младшего разряда счетчика 1 импульсов преобразуются в аналоговое напряжение, изменяющееся по линейно нарастающему закону, с помощью цифроаналогового преобразователя 2 младшего разряда. Цифроаналоговые преобразователи 3 старшего разряда, преобразующие код счетчика старшего разряда в линейно нарастающее напряжение, отличаются от цифроаналогового преобразователя 2 младших разрядов наличием преобразователя кодов на его входе. Преобразователь кода преобразует код Либау-Крейга в единичный (га - 1) позиционный код и для m 5 может быть

реализован на основе следующих логических соотношений

0

,

l5-

5

4

Ч

1з-

ll

,

а,+а,

Ч

1 а.

5

1 ,

7 l и а.

5

3 5 -9 , г-де ., „ „, прямой и инверсный сигналы i-ro разряда счетчика старших разрядов; 1, - выходной сигнал преобразователя кода. Соединение входов цифроаналоговых преобразователей старшего разряда с выходами счетчика разряда выполняется в соответствии с выражением k 2 m + 1 - j + i - для прямых

выходов разряда счетчика k 3 m + + 1 - j + i - для инверсных выходов, где i - номер выхода счетчика старшего разряда, j - номер цифроаналогового преобразователя старшего разряда, k - номер входа j-ro цифроаналогового преобразователя 3 старшего разряда. Если значение k 2 га, то из полученного значения вычитается число кратное 2 т; значение k 2 m указывает на отсутствие связи между данным прямым или инверсным выходом счетчика старшего разряда с входом данного j-ro цифроаналогового преобразователя 3 старшего разряда.

Сигнал с выхода цифроаналогового преобразователя 2 младшего разряда поступает на вторые информационные входы всех 2 m компараторов 4, на

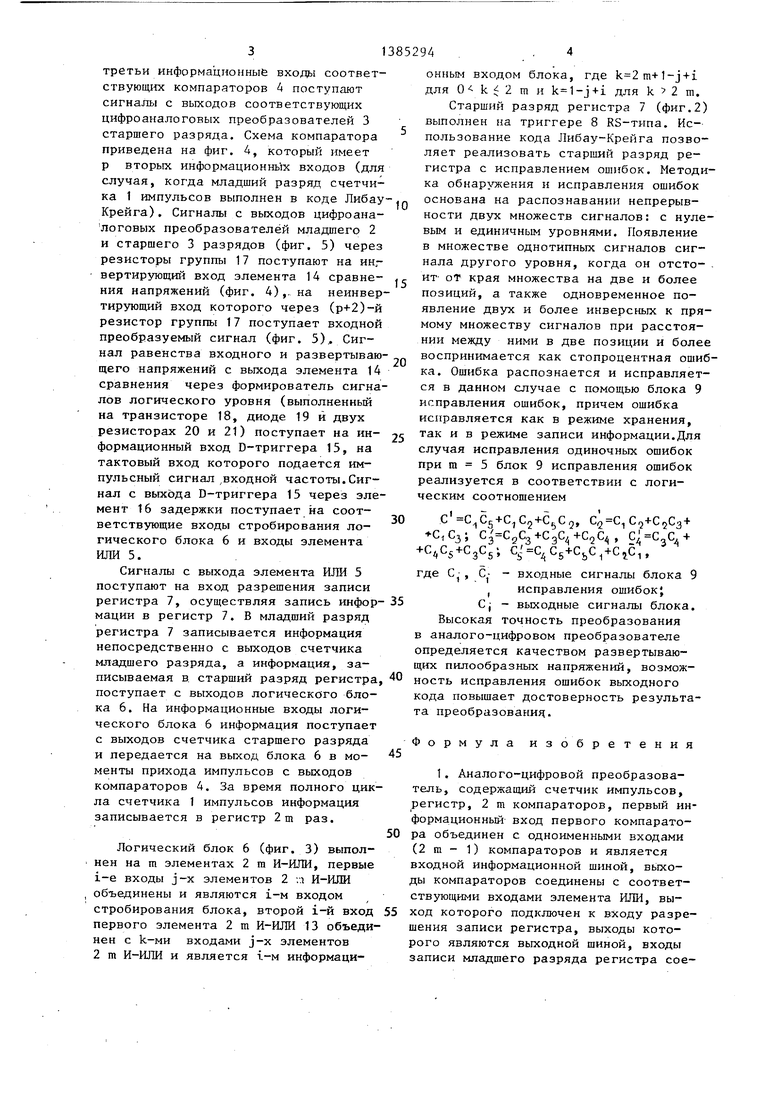

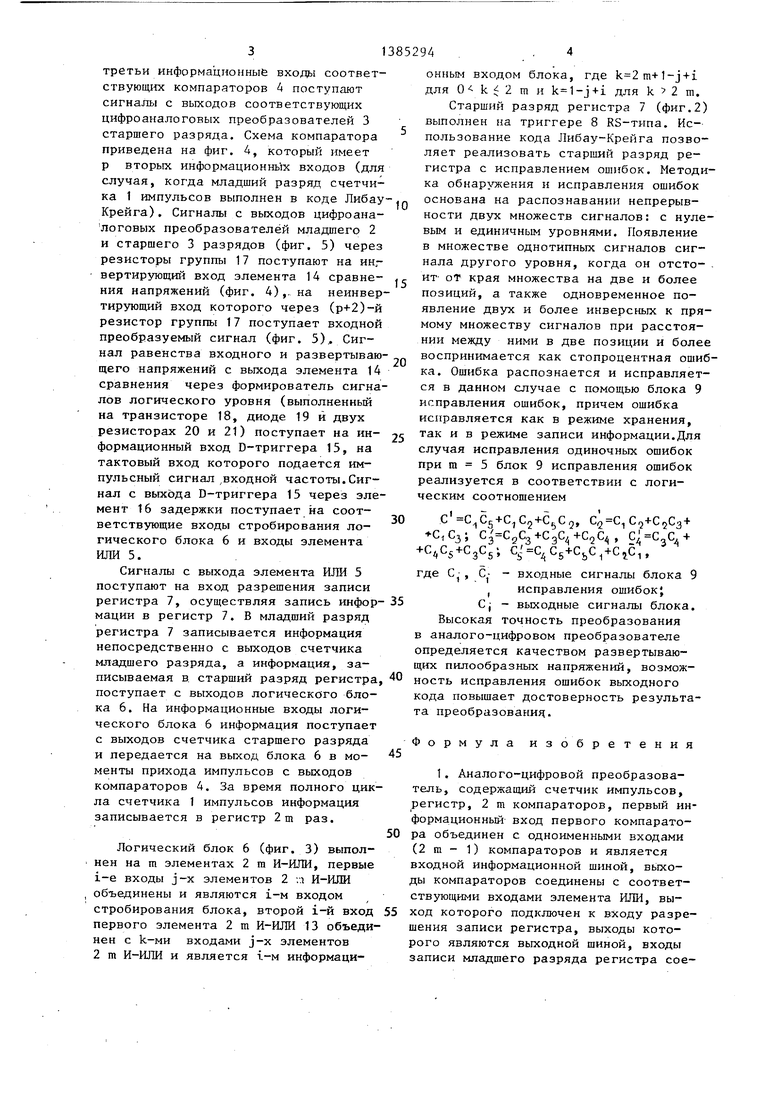

третьи информационные входь; соответ- ствующ компараторов 4 поступают сигналы с выходов соответствующих цифроаналоговых преобразователей 3 старшего разряда. Схема компаратора приведена на фиг. 4, который имеет р вторых информационнь1х входов (для случая, когда младший разряд счетчика 1 импульсов выполнен в коде Либау Крейга). Сигналы с выходов цифроана- логовых преобразователей младшего 2 и старшего 3 разрядов (фиг. 5) через резисторы группы 17 поступают на инг вертирующий вход элемента 14 сравнения напряжений (фиг. 4),, на неинвертирующий вход которого через (р+2)-й резистор группы 17 поступает входной преобразуемый сигнал (фиг. 5), Сигнал равенства входного и развертывающего напряжений с выхода элемента 14 сравнения через формирователь сигналов логического уровня (выполненный на транзисторе 18, диоде 19 и двух резисторах 20 и 21) поступает на информационный вход D-триггера 15, на тактовый вход которого подается импульсный сигнал ,входной частоты.Сигнал с выхода D-триггера 15 через элемент 16 задержки поступает на соответствующие входы стробирования логического блока 6 и входы элемента ИЛИ 5.

Сигналы с выхода элемента ИЛИ 5 поступают на вход разрешения записи регистра 7, осуществляя запись информации в регистр 7. В младший разряд регистра 7 записывается информация непосредственно с выходов счетчика младшего разряда, а информация, записываемая B старший разряд регистра поступает с выходов логического блока 6. На информационные входы логического блока 6 информация поступает с выходов счетчика старшего разряда и передается на выход блока 6 в моменты прихода импульсов с выходов компараторов 4. За время полного цикла счетчика 1 импульсов информация записывается в регистр 2т раз.

Логический блок 6 (фиг. 3) выполнен на m элементах 2 га И-ИЛИ, первые i-e входы J-X элементов 2 г. И-ИЛИ объединены и являются i-м входом стробирования блока, второй i-й вход первого элемента 2 m И-ИЛИ 13 объединен с k-ми входами j-x элементов 2 m И-ИЛИ и является 1-м информаци10

5

0

5

0

5

0

5

0

5

онным входом блока, где m+l-j+i для 0 k 2 m и k 1-j+i для k 2 ш.

Старший разряд регистра 7 (фиг.2) выполнен на триггере 8 RS-типа. Использование кода Либау-Крейга позволяет реализовать старший разряд регистра с исправлением ошибок. Методика обнарлгжения и исправления ошибок основана на распознавании непрерывности двух множеств сигналов: с нулевым и единичным уровнями. Появление в множестве однотипных сигналов сигнала другого уровня, когда он отсто- . ит- от края множества на две и более позиций, а также одновременное появление двух и более инверсных к прямому множеству сигналов при расстоянии между ними в две позиции и более воспринимается как стопроцентная ошибка. Ошибка распознается и исправляется в данном случае с помощью блока 9 исправления ошибок, причем ошибка исправляется как в режиме хранения, так и в режиме записи информации.Для случая исправления одиночных ошибок при m 5 блок 9 исправления ошибок реализуется в соответствии с логическим соотношением

I - - 1 .С -С. Ct с п, Сл С- оС

, ,jC + -hC C -f-CgCj-, C C C5-fCbC +C C,,

где , С- - входные сигналы блока 9

I исправления ошибокJ Cj - выходные сигналы блока. Высокая точность преобразования в аналого-цифровом преобразователе определяется качеством развертываю- щжс пилообразных напряжений, возможность исправления ошибок выходного кода повышает достоверность результата преобразование.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий счетчик импульсов, регистр, 2 m компараторов, первый информационный вход первого компаратора объединен с одноименными входами (2 га - 1) компараторов и является

входной информационной шиной, ВЬ1ХОды компараторов соединены с соответствующими входами элемента ИЛИ, выход которого подключен к входу разрешения записи регистра, выходы которого являются выходной шиной, входы записи младшего разряда регистра сое,

динены с соответс.тв пощш-т первь ми выходами счетчика импульсов, счетньш вход которого является входной шиной отличающийся тем, что, с целью повышения точности и надежности за счет упрощения устройства, в него введены 2 п цифроаналоговых преобразователей старшего разряда, цифроаналоговый преобразователь младшего разряда и логический блок, а счетчик импульсов выполнен на последовательно соединенных счетчике младшего разряда и многофазном счетчике старшего разряда, вход счетчика младшего разряда является счетным входом счетчика импульсов, а его вькоды являются первыми выходами счетчика импульсов, выходы логического блока подключены к соответствующим входам записи старшего разряда регистра,информационные входы подключены к соответствующим m прямым и m инверсным выходам многофазного счетчика старшего разряда, а входы стробирования соединены с выходами соответствующих 2 m компараторов, входы стробирования которых объединены и подключены к входной тактовой шине, вторые информационные входы объединены и соединены с выходом цифроаналогового преобразователя младшего разряда, третьи информационные входы подключены к выходам соответствующих 2 m .цифроаналоговых преобразователей старшего разряда, входы цифроанало гового преобразователя младшего разряда соединены с соответствующими выходами счетчика младшего разряда 1-й прямой и i-и инверсный вьгходы многофазного счетчика старшего разряда соединены соответственно с k-м и (k+m)-M входами j-ro цифроаналогового преобразователя старшего разряда, где m+1-j + i для и k 1-j+i для k 2 m - 1, k 2 m.

2. Преобразователь по п. 1, отличающийся тем, что, с целью повьщ1ения достоверности результата преобразования, старший разряд регистра выполнен на га тригге- pax, блоке исправления ошибок, инверторе, группе инверторов и на 2 m элементах 2И-ИЛИ, выходы которых соединены с соответствующими входами блок исправления ошибок, выходы которого подключены к входам соответствующих триггеров, прямой и инверсный выходы i-ro триггера соединены с первыми

.-

5

д г2025

55

30

35

40

входами перв1 1х i рупп входов соответственно i-ro и ()-ro элементов 2И-ИЛИ и являются соответствующими i-ми выходами старшего разряда регистра, первый вход второй группы входов i-ro элемента 2И-Ш 1И соединен через i-й инвертор группы с первым входом второй группы входов (i+m)-ro элемента 2И-ИЛИ И является i-м входом записи старшего разряда регистра,второй вход второй группы входов первого элемента 2И-ИЛИ объединен с одноименными входами вторых групп входов 2 m - 1 элементов 2И-ИЛИ и является входом разрешения записи старшего разряда регистра, вторые входы первой группы входов 2 m элементов 2И-ИЛИ объединены и через инвертор подключены к входу разрешения записи старшего разряда регистра.

3. Преобразователь по п, 1, отличающийся тем, что логический блок выполнен на m элементах 2 га И-ИЛИ, выходы которых являются выходами блока, первый вход i-й группы входов первого элемента 2 m И-ИЛИ объединен с одноименными входами i-x групп входов га - 1 элементов 2 m И-ИЛИ и является 1-м входом стробирования блока, второй вход i-й группы входов первого элемента 2 ш И-ИЛИ объединен с вторыми входами k-x групп входов соответствующих j-x элементов 2 m И-ИЛИ и является 1-м информационным входом блока, где m+1-j+i для О k f 2 m и k 1-j+i для k 2 m.

4,, Преобразователь по п. 1, о т - личающийся тем, что компаратор выполнен на элементе сравнения напряжений, триггере, транзисторе, диоде, группе из р+2 резисторов, где р - число разрядов двоичного счетчика младших разрядов, первом и втором резисторах и элементе задержки, выход которого является выходом компаратора, а вход соединен с выходом триггера, тактовый вход которого является входом стробирования компаратора, а информационный вход соединен с коллектором транзистора и через первый резистор подключен к шине питания, эмиттер транзистора соединен с анодом диода и подключен к шине нулевого потенциала, база транзистора соединена с катодом диода и через второй резистор подключена к выходу элемента сравнения напряжений.

Чт

-0 I

1Г;7

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Устройство для определения корреляционной функции | 1984 |

|

SU1363255A1 |

| Устройство для управления @ -фазным вентильным преобразователем | 1989 |

|

SU1721756A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Преобразователь позиционного кода в кодлибау-крейга | 1978 |

|

SU911725A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования напряжения постоянного тока в цифровой код. Цель изобретения - по- вьшение точности и надежности за счет упрощения устро1 ства. Аналого-цифровой преобразователь содержит счетчик 1 импульсов, цифроаналоговый преобразователь 2 младших разрядов, 2mцифроаналоговых преобразователей 3 старших разрядов, 2 m компараторов 4, элемент ШШ 5, логический блок 6 и регистр 7. Старшие разряды регистра 7 выполнены в коде Либау-Крейга на m триггерах, блоке исправления.ошибок, 2 m элементах 2 H-IinH, группе из m инверторов и инверторе. Логический блок 6 выполнен на элементах 2 m И-ИЛИ. Компараторы 4 вьтолнены на компараторе напряжения, триггере, элементе задержки, группе резисторов, транзисторе, диоде и двух резисторах. Выполнение старших разрядов счетчика 1 импульсов и регистра 7 в коде Либау-Крейга и введение 2 ш цифроана- логовых преобразователей 3 старших разрядов позволило повысить точность преобразования за счет повьшения линейности развертывающих напряжений на входах компараторов 4. 3 з.п. ф,, 6 ил. о (Л

ifm ... i /

Vut.3

a,.-as

А дСУ .- ° -

Л«Ог

ajL

Oj

Оч

05

В«+Вз 5jt5« Boi-Bs Sei-Bf Bo+Bf. So+Bj Bti-B BofBj

вⱫ

ir, k ПУт ВУ. ЯГ7 |б К

Bei-Bf BotBy

фу«.5

| Проектирование микроэлектронных цифровых устройств./Под ред | |||

| С.А.Майорова | |||

| М.: Сов | |||

| радио, 1977, Авторское свидетельство СССР № 327602, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-30—Публикация

1986-04-22—Подача