вертого делителя частоты, разрядные входы - с соответствующими выходами третьего запоминающего устройства, вход сброса которого соединен с соответствующими входами сброса первого и второго запоминающих устройств, разрядные входы - с разрядными выходами сумматора кодов, первые разрядные входы которрго подключены к соот ветствующим выходам второго счетчика импульсов, вторые разрядные входы - к кодовой шине коэффициента умножения, а вход списьшания - к соответствующим входам первого и второго счетчиков импульсов.

2. Умножитель частоты по п.1, отличающийся тем, что каждый из делителей частоты содержит элемент ИЛИ, счетчик импульсов, счетный вход которого является входом делителя частоты, компаратор кодов, первйя и вторая группы входов которо го соединены соответственно с разрядными выходами счетчика импульсов и разрядными входами делителя частоты, выход - с выходом делителя частоты и первым входом элемента ИЛИ, второй вход которого соединен с входом Сброс делителя частоты, а выход с входом Сбрдс счетчика импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Цифровой умножитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU824440A1 |

| Умножитель частоты следования периодических импульсов | 1976 |

|

SU542338A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Дискретный умножитель частоты повторения импульсов | 1977 |

|

SU692065A1 |

| Умножитель-нормализатор частотныхСигНАлОВ | 1979 |

|

SU847505A1 |

| Умножитель частоты следования импульсов | 1978 |

|

SU790344A1 |

| Устройство для умножения частоты следования импульсов | 1982 |

|

SU1040598A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1188846A1 |

1. УМНОЖИТЕЛЬ ЧАСТОТЫ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ, содержащий генератор опорной частоты, выход которо го подключен к счетному, входу первого делителя частоты, разрядные входы которого соединены с шиной кода коэффициента умножения, выход - со счетным входом первого счетчика импульсов, разрядные выходы которого подключены к соответствующим входам первого запоминающего устройства, выходы которого подкл

Изобретение относится к импульсной технике и может быть использовано в цифровых фазометрах, частотомет pax и синхронизаторах систем автоматического регулирования для умножения частоты периодических импульсов.

В указанных устройствах возникает необходимость умножения частоты за один или несколько периодов умножаемой частоты.

Известно устройство, содержащее генератор опорной частоты, первьй де литель частоты, счетчик, элемент задержки, запоминающее устройство, второй делитель частоты, схему -сравнения и схему ИЛИ

Работа известного устройства основана на том, что в первом периоде входных (умножаемых) импульсов производится измерение значения 1, с помощью счетчика, заполняемого импульf

сами с частотой

подаваемых

К

от первого делителя частоты. К моменту прихода второго входного импульса счетчик фиксирует число

с

опорн

(1)

п

бх К

де f

частота опорного генераопорнтора импульсов;

К коэффициент умножения устройства;

период входных (умножае

9 мых) импульсов.

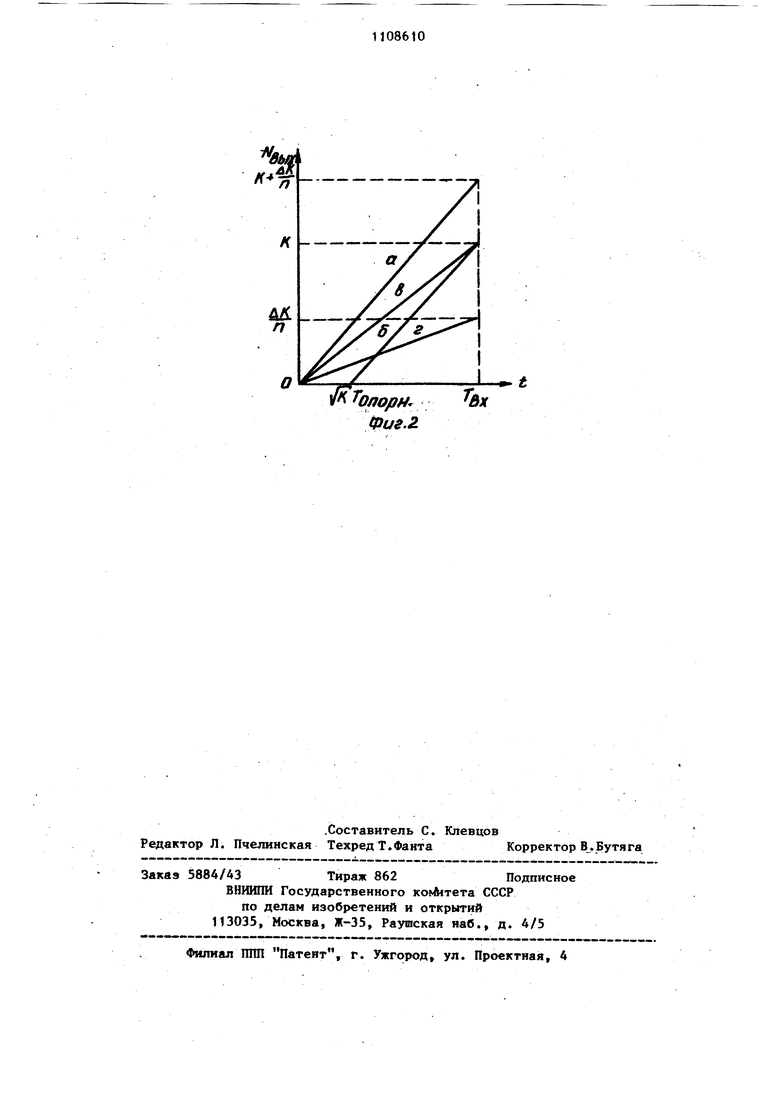

Начиная со второго периода входных импульсов,известное устройство ; формирует выходную последовательность иьтульсов. Это осуществляется при помощи результатов предварительного измерения периода входных импульсов .вторым делителем частоты, производящим деление частоты входных опорных импульсов на число п счетчика. При этом

опорн

(2)

f«K.

п

т.е. известное устройство осуществляет умножение частоты входных импульсов на коэффициент умножения К.

Однако измерение периода Т, производится неточно так как за время

Tgx на вход умножителя приходит не впорн Тр импульсов, как это соответствует выражению (1), а

(3)

вх опор«Т,+лК«п,К+дК

импульсов (где лК - остаток в первом делителе частоты, сдответствую1ций числу опорных импульсов, прощедших на вход этого делителя в промежуток времени между п-ым выходным импульсом этого делителя и моментом прихода очередного (второго) входного импульса) .

Поэтому выражение (2) имеет вид:

f.,

(4)

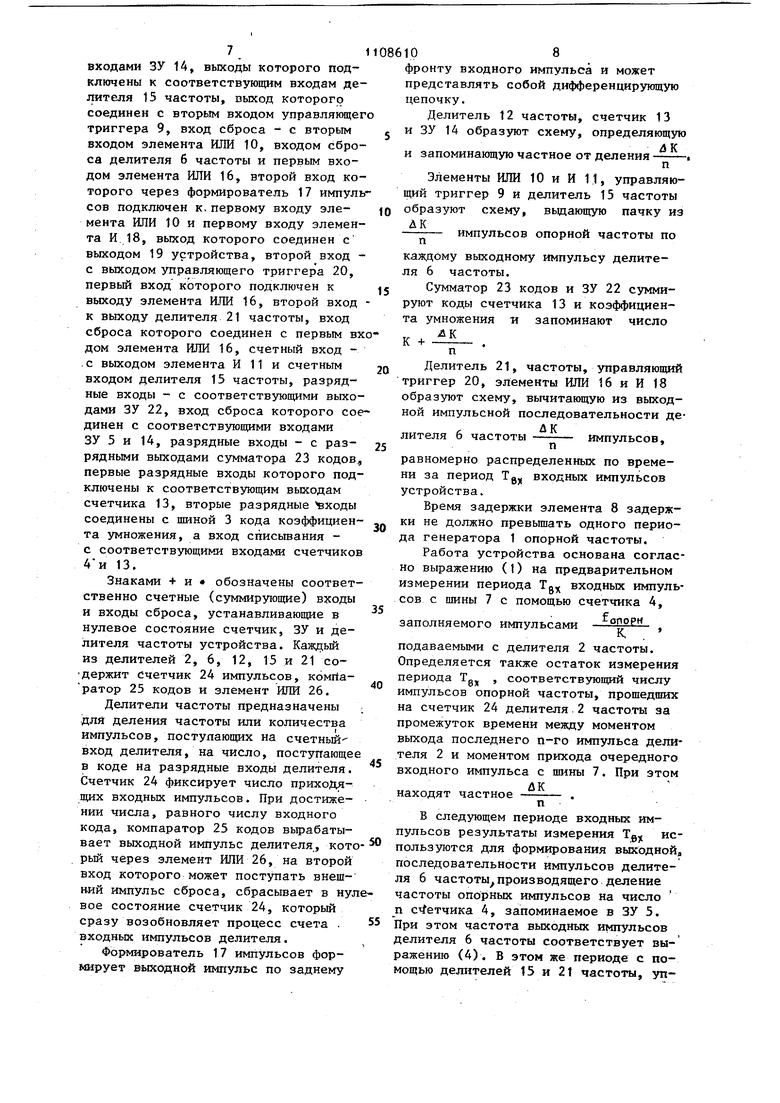

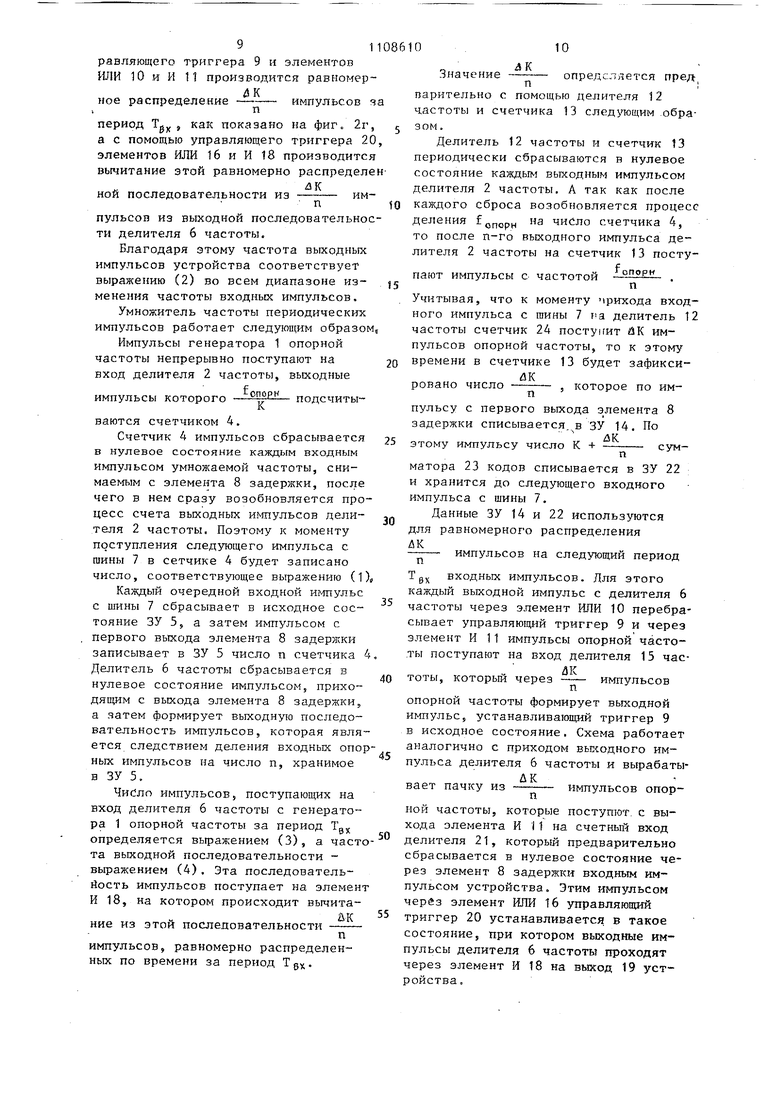

вых т.е. при йК7:П известное устройство имеет соответствующую погрешность умножения. Известно также устройство, содержа щее генератор опорной частоты первьй делитель частоты, счетчик, запоминающее устройство, элемент задержки, второй делитель частоты, схему сравнения и схему ИЛИ, реверсивный счетчик, управляющий триггер,, схемы ИЛИ и И, а также ждуощй мультивибратор 2 В указанном устройстве, принцип работы которого в основном аналогичен описанному, остаток л К первого периода входных импульсов вычитается внача ле второго периода .входных импульсов из последовательности импульсов, поступающих на вход второго делителя частоты. Таким образом, согласно выражению (3) на вход второго делителя за период Т„, поступает К-п импульсов опорной частоты, а на выходе устройст ва за это время соответственно формируется К импульсов. Недостатком устройства является ограничение диапазона изменения умножаемой (входной) частоты сверху. Это объясняется тем, что задержка выходньк импульсов на рвемя ДК-Тррорн вызывает неравномерность распределения выходных импульсов за период Tg умножаемой частоты. Эта неравномерность увеличивается с увеличением частоты входных импульсов, что приводит к соответствующей погрешности измереНИН и ограничивает применение известного устройства в цифровых фазометрах частотомерах и других измерительных устройствах. Верхняя граничная частоты выходных импульсов определяется из усло6к так К(К-1) Наиболее близок к ггредлагаемому умножитель частоть, содержащий генера тор опорной частоты, выход которого подключен к счетному входу первого делителя частоты, разрядные входы которого соединены с шиной кода коэффициента умножения, выход - со счетным входом первого счетчика импульсов, разрядные выходу которого подключены к соответствующим входам первого запоминающего устройства, выходы которого подключены к соответствующим входам второго делителя частоты, вход сброса - к входной шине устройства и входу элемента задержки первый вход которого соединен с входом списывания первого счетчика импульсов, второй вход - с входом сброса первого счетчика импульсов и первого и второго делителей частоты, а первый вход первого управляющего триг гера подключен к выходу первого элемента И.ПИ, а выход - к первому входу первого элемента . Введение третьего и четвертого делителя частоты и второго зaпo fинaю щего устройства позволяет расширить диапазон изменения умножаемых частот до верхней граничной частоты, равв то время вх шоо {-. к-1 как, в устройстве 2}, верхняя граничная частота опоелеляется выражением вида f ах тс. К(К - 1) образом, данное устройство позволяет увеличить верхнюю граничную частоту Ук-Т раз. Однако и для него характерна задержка выходных импульсов на время коррекции, которая вызывает неравномерность распределения выходных импульсов за период умножаемой частоты,увеличивающуюся с увеличением частоты умножаемых импульсов и ограничивающую верхнюю граничную умножаемую частоту. Цель изобретения - расширение функциональных возможностей путем расширения диапазона изменения частоты входных импульсов. Поставленная цель достигается тем что в умножитель частоты периодических импульсов, содержа1ций генератор опорной частоты, выход которого подключен к счетному входу первого делителя частоты, разрядные входы которого соединены с шиной кода коэффициента умножения, выход - со счетным входом первого счетчика импульсов, разрядные выходы которого подключе- ны к соответствующим входам первого запоминающего устройства, выходы которого подключены к соответствующим входам второго делителя частоты, вход сброса - к входной 1пине устройства и входу элемента задержки, первьй выход которого соединен с входом списывания первого счетчика импульсов, второй выход - с входом сброса первого счетчика импульсов и первого и вто511рого делителей частоты, а первый вход первого управляющего триггера подклю4e1i к выходу первого элемента ИЛИ, выход - к первому входу первого элемента И, введены третий, четвертый и пятый делители частоты, второе и третье запоминающие устройства, сумма тор кодов, второй управляющий триггер формирователь импульсов и вторые элементы И и ИЛИ. причем сброса третьего делителя частоты соединен с выходом первого делителя частоты и входом сброса второго счетчика импульсов, разрядные входы - с соответствующими разрядными выходами первого счетчика импульсов, счетный вход с вторым входом первого элемента И, выходом генератора опорной частоты и счетйым входом второго делителя частоты, выход подключен к счетному входу второго счетчика импульсов, выходы которого соединены с разрядными входами второго запоминающего устройства, разрядные выходы которого подключены к соответствующим входам четвертого делителя частоты, выход которого соединен с вторым входом первого управляющего триггера у вход сброса - с первым входом первого элемента ИЛИ, входом . второ го делителя частоты и первьм входом второго элемента ИЛИ, второй вход ко торого через формирователь импульсов подключен к второму входу первого эле мента ИЛИ и первому входу второго эле мента И, выход которого соединен с выходом устройства, второй вход - с выходом второго управляющего триггера, первый вход которого подключен к выходу второго элемента ШШ, второй вход - к выходу пятого делителя частоты, вход сброса которого соединен с первым входом второго элемента ИЛИ счетный вход - с выходом первого элемента И и счетным входом четвертого делителя частоты, разрядные входы с соответствующими выходами третьего запоминающего устройства, вход сброса которого соединен с соответствующими входами сброса первого и второго запоминающих устройств, разрядные входы - с разрядными выходами сумматора кодов, первые разрядные входы которого подключены к соответствующим выходом второго счетчика импульсов вторые разрядные входы - к кодовой шине коэффициента умножения,а вход списывания - к соответствующим входам первого и второго счетчиков импульсов. 06 Каждый из делителей частоты содержит элемент ИПИ, счетчик импульсов, счетный вход которого является входом делителя частоты, и компаратор кодов, первая и вторая группы входов которого соединены соответственно с разрядными выходами счетчика импульсов и разрядными входами делителя частоты, выход - с выходом делителя час тоты и первым входом элемента ИЛИ, второй вход которого соединен с входом Сброс делителя частоты, а выход - с входом. Сброс счетчика импульсов . На фиг. 1 приведена структурная схема устройства; на фиг. 2а приваде но распределение импульсов выходной последовательности второго делителя частоты, соответствующее вьфажению (4); на фиг. 26 - распределение импульсов выходной последовательности прототипа; на фиг. 2 в - распределение импульсов выходной последовательности предлагаемого устройства; на фиг. 2г - распределение импульсов остатка ДК за период 1, . Умножитель частоты периодических импульсов содержит генератор 1 опорной частоты, выход которого подключен к счетному входу делителя 2 частоты, разрядные входы которого соединены с шиной 3 кода коэффициента умножения, выход - со счетным входом счетчика 4 импульсов, разрядные выходы которого подключены к соответст вую цим входам запоминающего устройст ва (ЗУ) 5, выходы,которого соединены с разрядными входами делителя 6 часто ты, вход сброса - с входной шиной 7 устройства и входом элемента 8 задержки, первый выход которого соединен с входом списывания счетчика 4 импульсов, второй выход - с входами сброса счетчика 4 импульсов и делителей 2 и 6 частоты. Первый вход управляющего триггера 9,подключен к « выходу элемента ИЛИ 10, выход - к первому входу элемента И 1,1, второй вход которого соединен со счетным входом делителя 6 частоты, выходом генератора 1 опорной частоты и счетным входом делителя 12 частоты, вход сброса которого подключен к выходу делителя 2 частоты и к входу сброса счетчика 13 импульсов, разрядные входы - к соответствующим разрядным выходам счетчика 4 импульсов, выход к счетному входу счетчика 13, выходы которого соединены с разрядными входами ЗУ 14, выходы которого подключены к соответствующим входам де литешя 15 частоты, пыход которого соединен с вторым входом управляюще триггера 9, вход сброса - с вторым входом элемента ИЛИ 10, входом сбро са делителя б частоты и первым входом элемента ИЛИ 16, второй вход ко торого через формирователь 17 импул сов подключен к. первому входу элемента ИЛИ 10 и первому входу элемен та И.18, выход которого соединен с выходом 19 устройства, второй вход с выходом управляющего триггера 20, первый вход которого подключен к выходу элемента ИЛИ 16, второй вход к выходу делителя 21 частоты, вход сброса которого соединен с первым в дом элемента ИЛИ 16, счетный вход .с выходом элемента И 11 и счетным входом делителя 15 частоты, разрядные входы - с соответствующими выхо дами ЗУ 22, вход сброса которого со динен с соответствующими входами ЗУ 5 и 14, разрядные входы - с разрядными выходами сумматора 23 кодов первые разрядные входы которого под ключены к соответствующим выходам счетчика 13, вторые разрядные ходы соединены с шиной 3 кода коэффициен та умножения, а вход списьгоания с соответствующими входами счетчико 13. Знаками + и обозначены соответ ственно счетные (суммирующие) входы и входы сброса, устанавливающие в нулевое состояние счетчик, ЗУ и делителя частоты устройства. Каждьй из делителей 2, 6, 12, 15 и 21 содержит Счетчик 24 импульсов, KOMrtaратор 25 кодов и элемент ИЛИ 26. Делители частоты предназначены для деления частоты или количества импульсов, поступающих на счетныйвход делителя, на число, поступающе в коде на разрядные входы делителя. Счетчик 24 фиксирует число приходя щих входных импульсов. При достижении числа, равного числу входного кода, компаратор 25 кодов вырабатывает выходной импульс делителя, кот рый через элемент ИЛИ 26, на второй вход которого может поступать внешний импульс сброса, сбрасывает в ну вое состояние счетчик 24, который сразу возобновляет процесс счета . входных импульсов делителя. Формирователь 17 импульсов формирует выходной импульс по заднему фронту входного импульса и может представлять собой дифференцирующую цепочку. Делитель 12 частоты, счетчик 13 и ЗУ 14 образуют схему, определяющую и запоминающую частное от деления Элементы ИЛИ 10 и И 11, управляющий триггер 9 и делитель 15 частоты образуют схему, вьщающую пачку из импульсов опорной частоты по каждому выходному импульсу делителя 6 частоты. Сумматор 23 кодов и ЗУ 22 суммируют коды счетчика 13 и коэффициента умножения я запоминают число К + j -г - - -- 4 Делитель 21, частоты, управляющий триггер 20, элементы ИЛИ 16 и И 18 образуют схему, вычитающую из выходной импульсной последовательности делителя 6 частоты импульсов. равномерно распределенных по времени за период Tg,, входных импульсов устройства Время задержки элемента 8 эадержки не должно превьшать одного периода генератора 1 опорной частоты. Работа устройства основана согласно выражению (1) на предварительном измерении периода Tg, входных импульсов с щины 7 с помощью счетчика 4, заполняемого импульсами , подаваемыми с делителя 2 частоты. Определяется также остаток измерения периода Т соответствующий числу импульсов опорной частоты, прощедших на счетчик 24 делителя.2 частоты за промежуток времени между моментом выхода последнего п-го импульса делителя 2 и моментом прихода очередного входного импульса с шины 7. При этом ДК находят частное в следующем периоде входных импульсов результаты измерения Tg используются для формирования выходной последовательности импульсов делителя 6 частоты производящего деление частоты опорных импульсов на число п с етчика 4, запоминаемое в ЗУ 5. При этом частота выходных импульсов делителя 6 частоты соответствует выражению (4). В этом же периоде с помощью делителей 15 и 21 частоты, уп9равляющего триггера 9 и элементов ИЛИ 10 и И 11 производится равиомер й К ное распределение - импульсов Tg 5 как показано на фиг. 2г период ig 5 а с помощью управляющего триггера 2 элементов ИЛИ 16 и И 18 производитс вычитание этой равномерно распредел ной последовательности из им п пульсов из выходной последовательно ти делителя 6 частоты. Благодаря этому частота выходных импульсов устройства соответствует выражению (2) во всем диапазоне изменения частоты входных импульсов. Умножитель частоты периодических импульсов работает следующим образо Импульсы генератора 1 опорной частоты непрерывно поступают на вход делителя 2 частоты, выходные подсчитыимпульсы которого ваются счетчиком 4. Счетчик 4 импульсов сбрасывается в нулевое состояние каждым входным импульсом умножаемой частоты, снимаемым с элемента 8 задержки, после чего в нем сразу возобновляется про цесс счета выходных импульсов делителя 2 частоты. Поэтому к моменту поступления следующего импульса с гаины 7 в сетчике 4 будет записано число, соответствующее вьфажению (I Каждый очередной входной импульс с шины 7 сбрасывает в исходное состояние ЗУ 5, а затем импульсом с первого выхода элемента 8 задержки записывает в ЗУ 5 число п счетчика Делитель 6 частоты сбрасывается в нулевое состояние импульсом, приходящим с выхода элемента 8 задержки, а яатем формирует выходную последовательность импульсов, которая явля ется следствием деления входных опо ных импульсов на число п, хранимое в ЗУ 5. Число импульсов, поступающих на вход делителя 6 частоты с генератора 1 опорной частоты за период Тд определяется вьфажением (3), а част та выходной последовательности выражением (4), Эта последовательйость импульсов поступает на элемен И 18, на котором происходит вычитание из этой последовательности импульсов, равномерно распределенных по времени за период Т Значение определяется предварительно с помощью делителя 12 частоты и счетчика 13 следующим -образом. Делитель 12 частоты и счетчик 13 периодически сбрасываются в нулевое состояние каждым выходным импульсом делителя 2 частоты, Л так как после каждого сброса возобновляется процесс деления fonopH число счетчика 4, то после п-го выходного импульса делителя 2 частоты на счетчик 13 поступают импульсы с- частотой . , Учитывая, что к моменту прихода входного импульса с шины 7 та делитель 12 частоты счетчик 24 посту гит йК импульсов опорной частоты, то к этому времени в счетчике 13 будет зафиксийКровано число , которое по импульсу с первого выхода э лемента 8 задержки списывается, в ЗУ 14. По этому импульсу число К + сумматора 23 кодов списывается в ЗУ 22 и хранится до следующего входного импульса с шины 7. Данные ЗУ 14 и 22 используются для равномерного распределения импульсов на следующий период Тц входных импульсов. Для этого каждый выходной импульс с делителя 6 частоты через элемент ИЛИ 10 перебрасывает управляющий триггер 9 и через элемент И 11 импульсы опорной частоты поступают на вход делителя 15 частоты, который через импульсов опорной частоты формирует выходной импульс, устанавливающий триггер 9 в исходное состояние. Схема работает аналогично с приходом вькодного импульса делителя 6 частоты и вырабатывает пачку из импульсов опорной частоты, которые постушот. с выхода элемента И 11 на счетньй вход делителя 21, который предварительно сбрасывается в нулевое состояние через элемент 8 задержки входным импульсом устройства. Этим импульсом через элемент ШШ 16 управляющий триггер 20 устанавливается в такое состояние, при котором выходные импульсь делителя 6 частоты проходят через элемент И 18 на выход 19 устройства. 11 По мере увеличения числа выходных импульсов делителя 6 частоты чио ло, фиксируемое счетчиком 2А делителя 21 частоты, увеличивается и, наконец, достигает значения К+ iSTO осуществляется через п 1 выходных импульсов делителя 6 частоты). При этом делитель 21 частоты формирует выходной импульс, перебрасывая триггер 20 и закрывая элемент И 18. Поэтому следующий выходной импульс делителя 6 частоты на входную шину устройства не проходит. Задний фронт этого импульса разрешает прохояздение выходных импульсов делителя 6 частоты на выход 19 устроист ва. За период Т, делитель 6 частоты (фиг. 2а) формирует К + импуль сов, по которым за это время на вход 1.108610 делителя 21 частоты поступает(К+--) импульсов. Поэтому за время Tg делитель 21 частоты вычитает из выходной последовательности делителя ДК ,, ДК 6 частотыимпульсов, равномерно распределенных по времени за период Tgjj (фиг. 2г), т.е. за период Tg устройствовырабатывает К выходных равномерно распределенных во времени импульсов (фиг. 2в), т.е. частота выходных импульсов соответствует выражению (2). Таким образом, устройство осуществляет умножение частоты выходных импульсов на коэффициент умножения. Верхняя граничная частота диапазона изменения умножаемых частот предлагаемого устройства в тГк-Т раз превьшает верхнюю граничную частоту прототипа .

l /(П

п

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПАТЕНТВО-ТЕКШ12БИБЛИОТЕКАВ. А. Иванов | 0 |

|

SU337947A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1983-03-09—Подача