(54) ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулятор частоты электроагрегата | 1985 |

|

SU1288891A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала | 1983 |

|

SU1131034A2 |

| ИЗМЕРИТЕЛЬ УРОВНЯ | 1992 |

|

RU2029248C1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для измерения среднего периода | 1985 |

|

SU1322221A1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Устройство управления иллюминацией | 1981 |

|

SU1001949A1 |

| Цифровое устройство для обработки информации частотных датчиков | 1984 |

|

SU1239622A1 |

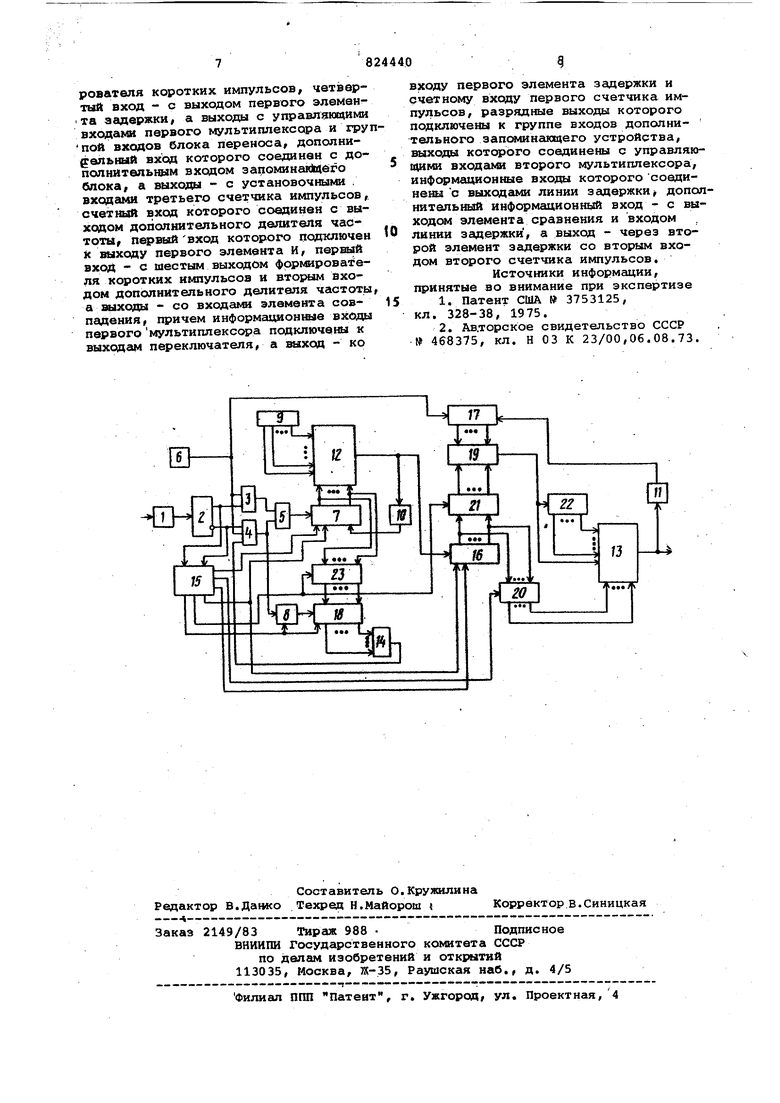

Изобретение относится к вычислительной и измерительной технике и может, быть использовано в цифровых измерителях частоты и фазы, а также в качестве согласующего блока в автоматических системах управления испытаниями тепловых двигателей, в час тности Двигателей внутреннего сгорания. Известно устройство для умножения частоты следования импульсов, содержащее формирователь входной частоты, выход которого через дифференцирующую схему подключен k .третьему счетчику, выход которого соединен с первым счетчиком, на вход которого через первый делитель поступает частота опорного генератора, при этом выходы первого счетчика соединены с вх дами схемы запоминания, выходы ко орой соединены со схемой совпадения, а выход опорного генератора через второй делитель подключен ко вхрду второго счетчика импульсов, выходы которого соединены со входами схвмл совпадения, выход которой подключен к шине сброса второго счетчика импульсов (д. Недостатком известного устройства является невысокс1я точность, тщ как не учитывается остаток в первом делителе частоты, который сужает диапазон работы умножителя. Наиболее близким по технической сущности к предлагаемому является умножитель частоты следования импульсов, содержащий счетчики импульсов, делитель частоты, опорный генератор, запоминающий блок, сравниванхций блок, элемент ИЛИ, линию задержки, преобразователь код-напряжение, дополнительный запоминакжций блок, источник колебаний умножаемой частоты, формирователь коротких импульсов, выход которого подключен к запоминающему блоку, к дополнительному запоминакадему блоку и через линию задержки к элементу Ш1ИД к первсилу счетчику и к делителю частоты, а выход опсфного генератора, соединен со вторым счетчиком импульсов и с делителем частоты, один выход которого соединен с первым счетчиком импульсов, а второй выход с дополнительным запоминг1нх4им блоком выход которого подключен к преобразователю код-напряжение, выход которого соединенс опорным генератором при этом выходы первого счетчика импульсов подключены к запоминакхцему блоку, выходы которого поданы на одНИ входы сравниваюцего блока, на вто рые входы которого поданы выходы вто рого счетчика импульсов 2. Недостатком данного устройства является низкая точность и ограниче ные функциональные возможности в свйзи с тем, что коэффициент умножения является постоянной величиной. Цель изобретения - повышение точности при одновременном расширении функциональных возможностей. Указанная цель достигается тем, что в цифровой умножитель частоты следования импульсов, содержащий делитель частоты, первый счетчик импульсов, разрядные выходы которого подключены к соответствующим входам запоминающего блока, выходы которого подключены к первой группе входов элемента сравнения, вторая группа входов которого подключена к разрядным выходам второго счетчика импульсов, первый вход которого соединен с выходом опорного генератора, формирователь коротких импульсов, первый и второй выходы которого соединены соответственно с дополнительными входами запоминагадего блока и дополнительного запоминающего блока элемент ИЛИ, линию задержки и формирователь импульсов, введены элементы И, дополнительный делитель частоты, элемент совпадения, элементы задержки, блок переноса, мультиплексоры, переключатель, третий счетчик импул сов и триггер, вход которого соединен с выходом формирователя импульсов, а прямой и инверсный выходы соответственно с первым к вторым входами формирователя коротких импульсов и с первыми входами первого и второго элементов И, вторые входы которых соединены с выходом опорного генератора, третий вход первого элемента И - с выходом элемента совпадения, а выходы первого и второго элементов И - с входами элемента ИЛИ, выход которого соединен -с первым входом делителя частоты, второй вход которого соединен с третьим выходом формирователя коротких импульсов, третий вход - с четвертым выходом формирователя коротких импульсов и первым.входом первого счетчика импульсов, второй вход которого подключен к пятому выходу формирователя коротких импульсов, четвертый вход - с выходом первого элемента Задержки, а выходы с управ ляющими входами первого мультиплексора и группой входов блока переноса , дополнительный вход которого соединен с,дополнительным входом запоминающего блока, а выходы - с устгшовочными входами третьего счет .чика импульсов, счетный вход которого соединен с выходом дополнитель ного делителя частоты, первый вход котсчрого подключен к выходу элемента И, первый вход - с шестым выходом формирователя коротких импульсов и вторым входом дополнительного делителя частоты, а выходы со входами элемента совпадения, причем информационные входы первого мультиплексора подключены к выходам переключателя, а выход - ко входу первого элемента задержки и счетному входу первого счетчика импульсов, разрядные которого подключены к группе входовдополнительного запоминагацего устройства, выходы которого соединены с управлянадими входами второго мультиплексора, информационные входы которого соединены с выходами, линии задержки, дополнительный информационный вход - с выходом элемента сравнения и входом линии задержки, а выход - через второй элемент задержки со вторым входом второго счетчика импульсов. На чертеже представлена структурная схема устройства. Устройство содержит формирователь 1 импульсов, триггер 2, элементы И 3 и 4, элемент ИЛИ 5, генератор 6 опорный, делители 7 и 8 частоты, переключатель 9, элементы 10 и 11 задержки, мультиплексоры 12 и 13, элемент 14 совпадения, формирователь 15 коротких импульсов, счетчики 16-18 импульсов, элемент 19 сравнения, запоминающие блоки 20 и 21, линия 22 задержки секционная, блок 23 переноса. Устройство работает следукяцим образом. Умножаемая частота поступает на формирователь 1, где преобразуется в импульсы, поступающие на счетный вход триггера 2. Триггер 2 формирует; строб, равный периоду входной частоты. Этот строб заполняется импульсами генератора б, которые через элемент 3 и элемент 5 поступают в делитель 7. Делитель 7, мультиплексор 12, переключатель 9 и элемент 10 представляют собой делитель с переменным коэффициентом деления. Коэффициент задается оператед ом через переключатель 9. Переклаочателем 9 выбирается один из информационш 1Х мультиплексора 12 и,Когда код, поступающий с делителя 7 на управлякшще входы мультиплексора 12, подключит этот вход на выкод мультиплексора 12, то через элемент 10 происходит установка в О делителя 7, затем процесс повторяется. Выбирая переключателем 9 другой информационный входа мультиплексора 12, мы меняем коэффициент пересчета. Импульсы с выхода мультиплексора 12 поступают в счетчик 16. Число поступивших импульсов равно где N - число импульсов, записанных в счетчик 16 в течени одного периода входной ча тоты ; F - частота опорного генерато ра 6 ; U Fg) - частота входного сигнала; К - коэффициент деления делит ля, равный коэффициенту ум ножения входной частоты. После окончания периода входной частоты число N. переписывается в блок 21, а счетчик 16 устанавливает ся в О. В течение следующего периода импульсы генератора поступают в счетчик 17, и при достижении числа, запи санного в блоке 21, блок 19 выдает сигнал равенства. Если частота генератора 6 в течение периода входной частоты поделилась делителем с переменным коэффициентом в целое число раз, т.е. в делителе 7 остатка нет, то блок 20 находится в О состоянии. При этом управляющие входы мультиплексора 13 подключают к его выходу информационный вход без задержки линией 22 заде жки. Сигнал равенства проходит через мультиплексор 13, второй элемент задержки 11 и устанавливает в О счет чик 17. Всего за период входной частоты число сигналов равенства будет следующим Na i7-V Таким образом, число.входных импульсов будет равно умноженной входной частоте 2. где Fgj,,y - частота выходных импульсов. . . Если в делителе 7 остался остаток которчый может быть равен числу от 1 до то после окончания периода входной частоты он через блок 23 записывается в счетчик 18, и делитель 7 устанавливается в О. Импульсы генератора б через элемент 4 поступа ют в делитель8 и через элемент 5 в делитель 7, Выходные импульсы делите ля 8 вычитают число, записанное в счетчике 18. Когда число в счетчике 18 станет равным О,-элемент 14 зак роет элемент 4. Благодаря этой операции мы вычисляем дробную часть чис ла N . Импульсы, вышедшие с делителя с переменным коэффициентом, поступают в счетчик 16 и после окончания периода входной частоты это число, равное дробной части числа Н, записывается в блок 20. В зависимости от числа, находящегося в блоке 20, упра ляющие входы мультиплексора 13 подключают на выход мультиплексора информационный вход с задержкой, пропорциональной этому числу. Период выходных импульсов увеяичивается на величину этой задержки, Таким образом, производится корректировка периода выходной частоты с учетом остатка, находящегося в делителе 7. Общая величина временизадержки выбирается равной периоду опорного генератора. Коэффициент деления делителя 8 равен числу ,секций линии 21 задержки. Ёсе сигналы управления вырабатсываются формирователем 15. Таким образом, предлагаемое устройство позволяет получить переменный коэффициент умножения за счет использования делителя с переменным коэффициентом деления, повысить точность умножения путем цифрового вычисления корректирующей величины и повысить быстродействие отработки изменения входной частоты. Формула изобретения Цифровой умножитель частоты следования импульсов, содержащий делитель частоты, первый счетчик импульсов, разрядные выходы которого псдключены к соответствующим входам запомин ющего блока, выходы которого подключены к первой группе входов элемента cjpaBнения, вторая группа входов которого подключена, к разрядным выходам второго счетчика импульсов, первый вход которого соединен с выходом опорного генератора, формирователь коротких импульсов, первый и второй выходы которого соединены соответственно с дополнительными входами запоминающего блока и дополнительного запоминаклцего блока, элемент ИЛИ, линию задержки и формирователь импульсов, отличающийся тем, что, с целью повышения точности при одновременном расширении функциональных возможностей, в него введены элементы И, дополнительный делитель частоты, элемент совпадения, элементы задержки, блок переноса, мультиплексоры, переключатель, третий счетчик .импульсов и тркггер, вход которого соединен с выходом формирователя импульсов, а прямой и инверсный выходы соответственно с первым и вторым входами формирователя коротких импульсов и с первыми входами первого и второго элементов И, вторые входы которых соединены с выходом опорного генератор ,третий вход первого элемента И - с выходом элемента совпадения, а вы-.:сди( первого и второго элементов И - с входами элемента ИЛИ, выход которого соединен с первым входом делителя частоты, вход которого соединен с- третьим выходом формирователя коротких импульсов, третий вход - с четвертым выходом формирователя ксфотких импульсов и первым входом первого счетчика импульсов, второй вход которого подключен к пятому выходу формирователя коротких импульсов, четвертый вход - с выходом первого элемен.та задержки, а выходы с управляющими входами первого мультиплексора и гру пой входов блока переноса, дополни вльмый вход которого соединен с Дополнительным входом зацоминакйЦбго блока, а вьисоды - с установочными входами третьего счетчика импульсов, счетный вход которого соединен с выходом дополнительного делителя частоты, первый вход которого подютючен к выходу первого элемента и, первый вход - с шестым выходом формирователя коротких импульсов и вторым входом дополнительного делителя частоты а выходы - со входакм элемента совпадения, причем информационщде входы первогомультиплексора подключены к выходам переключателяI а выход - ко входу первого элемента задержки и счетному входу первого счетчика импульсов, разрядные выходы которого подключены к группе входов дополнительного эапсячинающего устройства, выходы которого соединены с управляющими входами второго мультиплексора, информационные входы которого соединены °с выходами линии задержки, дополнительный информационный вход - с выходов элемента сравнения и входом линии задержки , а выход - через второй элемент згщержки со вторым входом второго счетчика импульсов. Источники информации, принятые во внимание при экспертизе 1.Патент США 3753125, кл. 328-38, 1975. 2.Ав.торское свидетельство СССР № 468375, кл. Н 03 К 23/00,06.08.73.

Авторы

Даты

1981-04-23—Публикация

1979-04-28—Подача