I

Изобретение относится к области вычислител ной техники и может Зьггь использовано в устройствах аналого-цифровых преобразователей.

Известны цифро-аналоговые преобразователи источники эталонных токов которых яойрОены по параметрической схеме, содержащие регистр чисел, первичнуй источник напряжения, источники эталонных токов, ключи и матрицу резисторов R 2R ПЬ

. Эти устройства обладают низким коэффициентом стабилизации выходного иапряжения.

Известен также цифро-аналоговый преобразователь, содержащий регистр, выходь Которого соединены с управляющими входами ключей, .первые входы последних соединены с узлами матрицы R 2R, а входы - с выходами источников эталонных токов, входы которых подключены к первичному источнику напряжения, а управляюище входы - к выходу компенсационного усилителя, первый вход которого соединен с источником эталонного напряжения 12.

Недостатком известного преобразователя является невысокая точность преобразования, обус ловленная отсутствием коррекции погрешности

из-за изменения параметров ключей и матрицы регистров при изменении условий работы.

Цель настоящего изобретения - Повьппение точности преобразования.

Поставленная цель достигается тем, что в щгфро-аналоговый преобразователь, содержащий регистр, выходы которого соединены с управляющими входами ключей, первые выходы последних соединены е узлами матрицы , а входы - с выходами источников эталонных токов, входы которых подключены к первичному источнику Напряжения, а управляющие входы - к выходу компенсационного усилнтеля, первый вход которого соединен с источником эталонного напряжения, введена дополнительная-матрица , узлы которой соединены со вторыми выходами ключей, а выход подключен ко второму входу компенсационного усилителя, третий вход которого соединен с выходом матрицы R-2R.

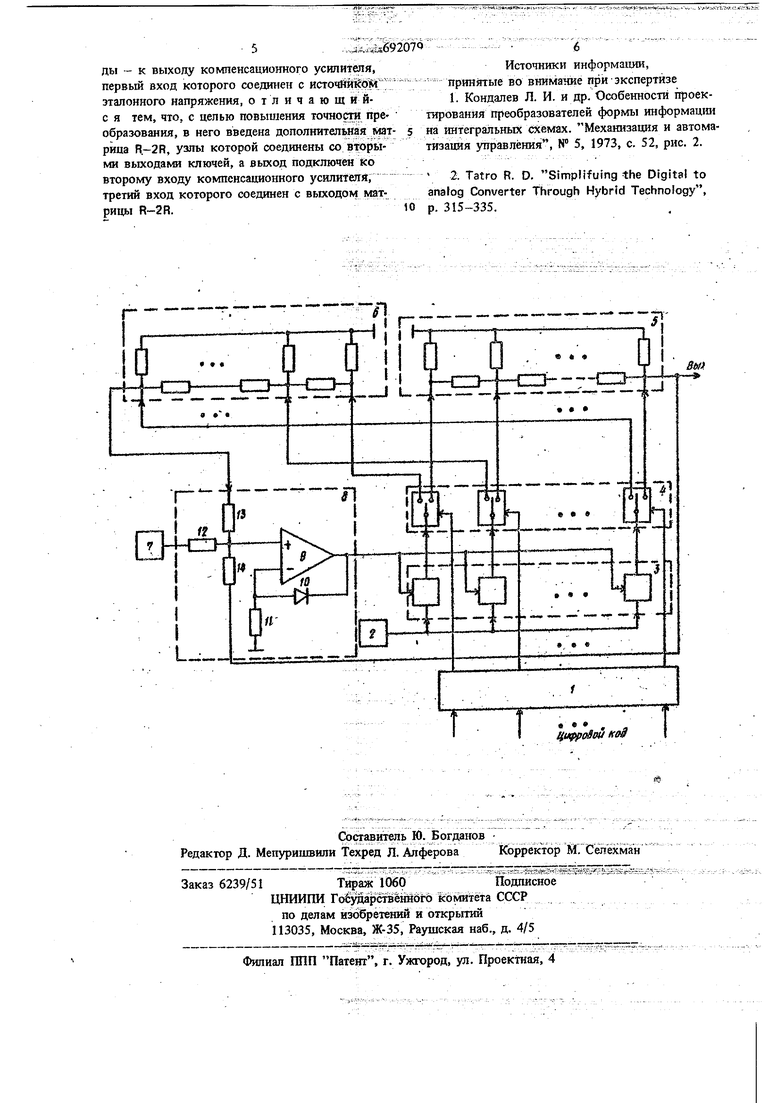

Сущность изобретения поясняется чертежом, где изображена функциональная электрическая схема устройства. 36 Оно содержит регистр чисел 1, первичный источник напряжения 2, источники эталонных токов 3, ключи 4, матрицу резисторов R-2R 5, дополнительную матрицу резисторов R-2R 6, источник эталонного напряжения 7 и компенсационный усилитель 8, состоящий из операционного усилителя 9, ограничительного диода 10, балансного резистора 11 и трех операционных резисторов 12, 13 и 14. Выходы регистра чисел 1 поразрядно соеди 1ены с управляющими входалш ключей 4, первые выходы которых поразрядао соединены с узлами матрицы резисторов R-2R 5, вторые выходы ключей 4 поразрядно соединены с узлами дополнительной матрицы резисторов R-2R 6, входы ключей 4 поразрядно соединены с выходами источников эт;алонных токов 3. а входы источников эталоннб.1х токов 3 подключены к первичному источ1шку напряжения 2. Вь1ход дополнительной матрицы резисторов R-2R 6 подключен к второму входу компенсационного усилителя 8, первый вход которого Подключен к источнику эталомного напряжения 7, а третий вход компенсационного усилителя 8 соединён с выходом матрицы резисторов R-2R Выход кбмпенсагщонного усилителя 8 соединен с управлятащими входами источников эталонных токов 3. Матрица резисторов R-2R б представляет собой матрицу резисторов, идентичную матрице резисторов R-2R 5. Компенсационный усилитель 8, представляет собой устройство, величина выходного сигнала которого определяемся разностью напряжений на инвертирующем неинвертирующем вхо дах операционного усилителя 9. Величина напряжении на инвертирующем входе операционного усилителя 9 задается балансным резистором 11 и остается постоянной в процессе работы цифро-аналогового преобразователя. Величина напряженшРна нейнвертирующем входе операционного усилителя 9, в любой момент работы ци(| о-аналогового преобразователя, опредеАяется напряжением источгопса эталонного напряжения 7, которое не изменяется в процессе работу цифро-аналогового преобразователя, и суммой напряжений на вькодах матрицы резист ров R-2R 5 и дополнительной матрицы резисто ров R-2R 6. Сумма этих напряжений действует на неинвертирующий вход операционного усили теля 9 через операционные резисторы 13 и 14. Ограничение уровня выходного сигнала компен сационного усилителя 8 при его значителыгом возрастании осуществляется ограничительным диодом 10, чем предотвращается самовозбужде ние операционного усилителя 9. Когда в регистре чисел 1 записьтается циф ровой код 01...1 навыходе старщего разряда регистра чисел 1 устанавливается сигнал логического нуля, на выходах последующих разрядов - сигнал логической единицы. Сигналом логического нуля ключ 4, управляющий вход которого соединен с выходом старшего разряда регистра чисел 1, устанавливается в положении 2, т.е. вход ключа 4 соединяется со вторым выходом ключа 4 и, тем самым, выход соответствующего источника эталонного тока 3 подключается к узлу дополнительной матрицы резисторов R-2R 6. Сигналом логической единицы с соответствующих выходов регистра чисел 1 все остальные ключи 4 устанавливаются в положение 1, т.е. входы ключей 4 соединяются с первыми выходами ключей 4 и, тем самым, выходы соответствующих источников эталонных токов 3 подключаются к узлам матрицы резисторов R-2R 5. На выходе матриць резисторов R-2R 5 (ВЫХ) устанавливается напряжение, эквивалентное коду 01..-1, т.е. коду, записанному в регистре чисел 1, а на выходе дополнительной матрицы резисторов R-2R 6 устанавливается напряжение, эквивалентное коду 10...О, т.е. коду, обратному по отнощению к коду, записанному в регистре чисел 1. При изменении цифрового кода 01..-1 в ре- гистре чисел 1, например, на код 10...0 сигналы на выходах регистра чисел 1 соответственно изменяются. На выходе матрицы резисторов R-2R 5 устанавливается напряжение, эквивалентное цифровому коду 10,..О, т.е. коду записанному в регистре чисел 1, а на выходе дополнительной матрицы резисторов R-2R 6 устанавливается напряжение, эквивалентное коду 01...1, т.е. коду обратному, по отнощению к коду, записанному в регистре чисел 1. Коррекция погрецшости преобразования цифрового кода в напряжение из-за изменения параметров источников эталонных токов 3, ключей 4 и ма±рицы резисторов R-2R 5 осуществляются автоматически, путем соррекции величины вы ходных токов источников, эталонных, токов 3 по величине суммарного напряжения на выходах матриць резисторов R-2R 5 и дополнительной матрицы резисторов R-2R б в любой момент работы цифро-аналогового преобразователя. Формула изобретения Цифро-аналоговый преобразователь, содержащий регистр, выходы которого соединены с управляющими входами ключей, первые выходы послехших соединены с узлами матрицы R-2R, а входы: - с выходами источников этало1шых токов, входы которых подключены к первичному источнику напряжения, а управляющие входы - к выходу компенсационного усилителя, первый вход которого соединен с источником эталонного напряжения, отличающийс я тем, что, с целью повышения точности преобразования, в него введена дополнительная матрица R.-2R, узлы которой соединены со вторыми выходами ключей, а выход подключен ко второму входу компенсационного усилителя, третий вход которого соединен с выходом матрицы R-2R.

Источники информа1ши, принятые во вниматше при экспертизе

1. Кондалев Л. И. и др. Особенности проектирования преобразователей формы информации на интегральных схемах. Механизация и автоматизация управления, № 5, 1973, с. 52, рис. 2.

- 2. Tatro R. D. Simplifuing tKe Digital to analog Converter through Hybrid Technology, p. 315-335.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-аналоговый преобразователь | 2017 |

|

RU2648579C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2240649C2 |

| Цифро-аналоговый перемножитель | 1975 |

|

SU598233A1 |

| Цифроаналоговый преобразователь | 1983 |

|

SU1192143A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1095389A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство цифроаналогового преобразования | 1987 |

|

SU1524180A1 |

| Устройство для преобразования сопротивления в код | 1989 |

|

SU1751849A1 |

| Устройство для синусно-косинусного цифро-аналогового преобразования | 1983 |

|

SU1129632A1 |

| Умножающий цифро-аналоговый преобразователь | 1985 |

|

SU1312738A1 |

.--„.-:

II iue«oSouKod

Авторы

Даты

1979-10-15—Публикация

1977-02-14—Подача