(54) АДАПТИВНЫЙ ВЫЧИСШ1ТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный цифровой фильтр | 1988 |

|

SU1566470A1 |

| СПОСОБ И УСТРОЙСТВО ГИБРИДНОЙ КОММУТАЦИИ РАСПРЕДЕЛЕННОЙ МНОГОУРОВНЕВОЙ ТЕЛЕКОММУНИКАЦИОННОЙ СИСТЕМЫ, БЛОК КОММУТАЦИИ И ГЕНЕРАТОР ИСКУССТВЕННОГО ТРАФИКА | 2014 |

|

RU2542906C1 |

| Демодулятор сигналов амплитудной манипуляции | 2022 |

|

RU2781271C1 |

| Приемник цифровых высокоскоростных фазоманипулированных сигналов | 1987 |

|

SU1490723A1 |

| Устройство для оценки деятельности операторов систем управления | 1978 |

|

SU752458A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОПОДОБНОЙ СЕТИ | 1992 |

|

RU2094843C1 |

| Адаптивный амплитудный анализатор | 1982 |

|

SU1078435A1 |

| РАНГОВЫЙ АДАПТИВНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1996 |

|

RU2100822C1 |

| Устройство для сейсмической разведки | 1988 |

|

SU1548759A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

I

Изобретение относится к области автоматики и вычислительной техники, а именно к построению самообучающихся вычислительных маши

Известны адаптивные вь числители, содержащие блоки входных ситуаций, блоки весовых коэффициентов, множительные устройства, сумматоры, пороговые устройства, ключи и блоки поиска минимума 1 .

Недостаток таких адаптивных вычислителей состоит в том, что для их обучения выполнению требуемой математической операции необходимо знать значения взвешенных сумм входных сигналов, а также то, что его входными и выходными величинами могут являться только двоичные сигналы.

Наиболее близким по технической сущности к данному изобретению является адаптивный вычислитель 2, содержащий кодирующее устройство, блок весовых коэффициентов, сумматор, пороговое устройство, компаратор. Входы блока весовых коэффшшентов и компаратора через кодирующее устройство подключены к цепям входных сигналов. Выходы блока весовых коэффициентов подключены к сумматору,

выход .которого соединен со входом порогового устройства. .Выход порогового устройства подключен ко входу компаратора, выход которого соединен с блоком весовых коэффициентов.

Недостаток этого устройства состоит в том, что адаптивный вычислитель имеет ограниченные функщюнальные возможности, так как на его выходе может быть получен только двоичный сигнал.

Целью изобретения является расширение класса решаемых задач, т.е. обеспечение получения на выходе устройства сигналов, соответствующих непрерывным значениям вычислит€льнь1Х функций.

Это достигается тем, что в адаптивный вычислитель, содержащий кодирующее устройство, выходы которого соещшены со входами компаратора и блока памяти весовых коэффициентов, выхош 1 которого соединены со входами сумматора, вькод которого подключен ко входу порогового элемента, выход которого объединен с выходом компаратора, а входы кодирующего устройства являются входами адаптивного вычислителя, введен интегратор, вход которого соединен с выходом порогового элемента, а выход интегратора является выходом адаптивного вычислителя и соединеи со входом кодирующего устройства.

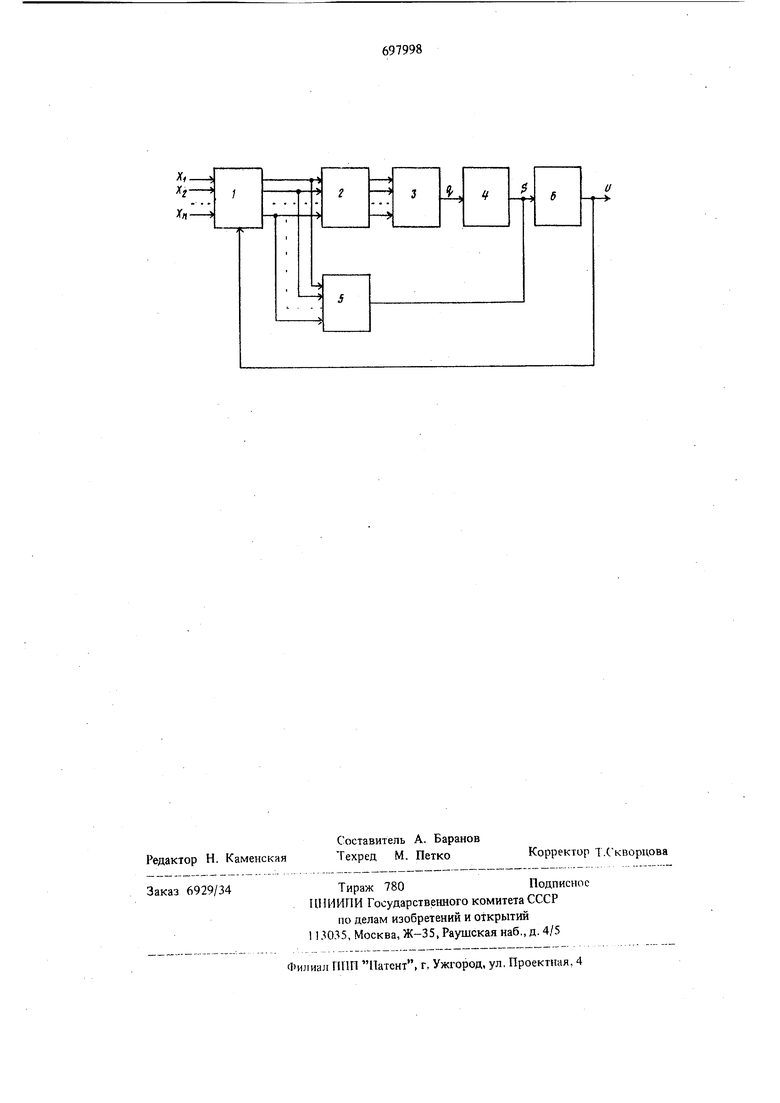

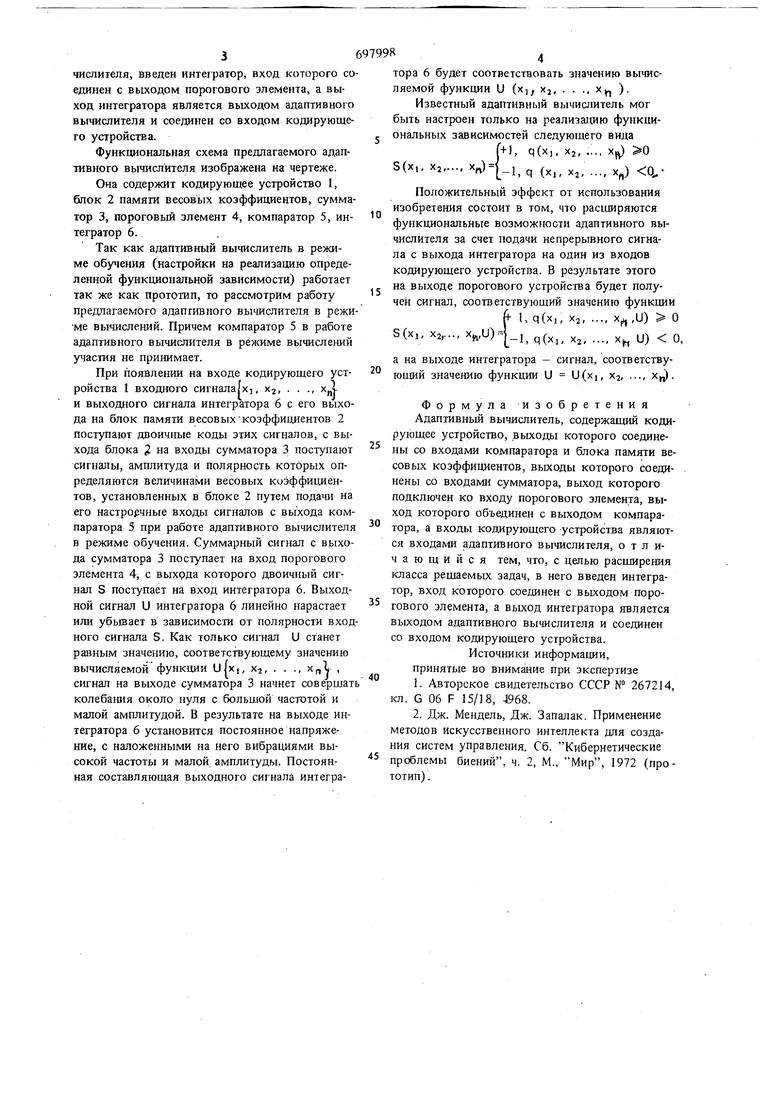

Функциональная схема нредлагаемого адаптивного вьршслителя изображена на чертеже.

Она содержит кодирующее устройство 1, блок 2 памяти весовых коэффициентов, сумматор 3, пороговый элемент 4, комнаратор 5, интегратор 6.

Так как адаптивный вычислитель в режиме обучения (настройки на реализацию определенной функциональной зависимости) работает так же как прототип, то рассмотрим работу предлагаемого адаптивного вычислителя в режиме вычислений. Причем компаратор 5 в работе адаптивного вычислителя в ремсиме вычислений участия не принимает.

При появлении на входе кодирующего устройства 1 входного сигнала|х, Хз, . . ., х„1 и выходного сигнала интегратора 6 с его выхода на блок памяти весовыхкоэффициентов 2 поступают двоичные коды этих сигналов, с выхода блока на входы сумматора 3 поступают сигналы, амплитуда и полярность которых определяются величинами весовых коэффициентов, установленных в блоке 2 путем подачи на его настроечные входы сигналов с выхода компаратора 5 при работе адаптивного вычислителя в режиме обучения. Суммарный сигнал с выхода сумматора 3 поступает на вход порогового элемента 4; с выхрда которого двоичный сигнал S поступает на вход интегратора 6. Выходной сигнал и интегратора 6 линейно нарастает или убьюает в зависимости от полярности входного сигнала S. Как только сигнал U станет равным значению, соответствующему значению вычисляемой функции ufxi, х, . . ., Xp,V , сигнал на выходе сумматора 3 начнет совершат колеба1шя около нуля с большой частотой и малой амплитудой. В результате на выходе интегратора 6 установится постоянное напряжение, с наложенными на него вибрациями высокой частоты и малой амплитуды. Постоянная составляющая выходного сигнала интегратора 6 будет соответствовать значению вычисляемой функции и ( Xj )

Известный адаптивный вычислитель мог быть настроен только на реализацию функциональных зависимостей следующего вида

Г+, q(x,. хг, .:., Х() 0

( , q (X,, xj, ..,, х) а.

Положительный эффект от использования изобретения состоит в том, что расширяются функциональные возможности адаптивного вычислителя за счет подачи непрерывного сигнала с выхода интегратора на один из входов кодирующего устройства. В результате этого на выходе порогового устройства будет получен сигнал, соответствующий значению функции

t,q(x,, Х2х,и) О

S(xi, Х2,.., x,U) q( LI) О

а на выходе интегратора - сигнал, соответствующий значению функции U U(xi, Х2, ..., х.

Формула изобретения Адаптивный вычислитель, содержащий кодирующее устройство, выходы которого соединены со входами компаратора и блока памяти весовых коэффициентов, выходы которого соединены со входами сумматора, выход которого подключен ко входу порогового элемента, выход которого объединен с выходом компаратора, а входы кодирующего устройства являются входами адаптивного вычислителя, отличающийся тем, что, с целью расншреьшя класса рещаемых задач, в него введен интегратор, вход которого соединен с выходом порогового элемента, а выход интегратора является выходом адаптивного вычислителя и соединен со входом кодирующего устройства. Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-11-15—Публикация

1978-06-09—Подача