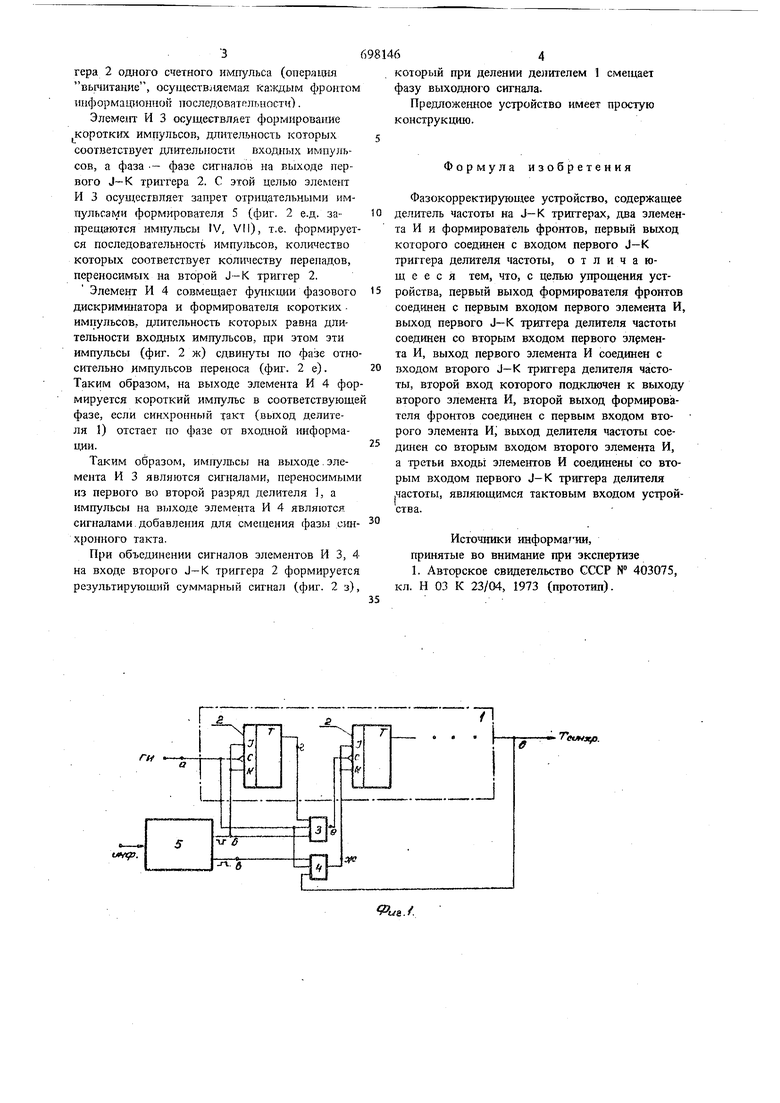

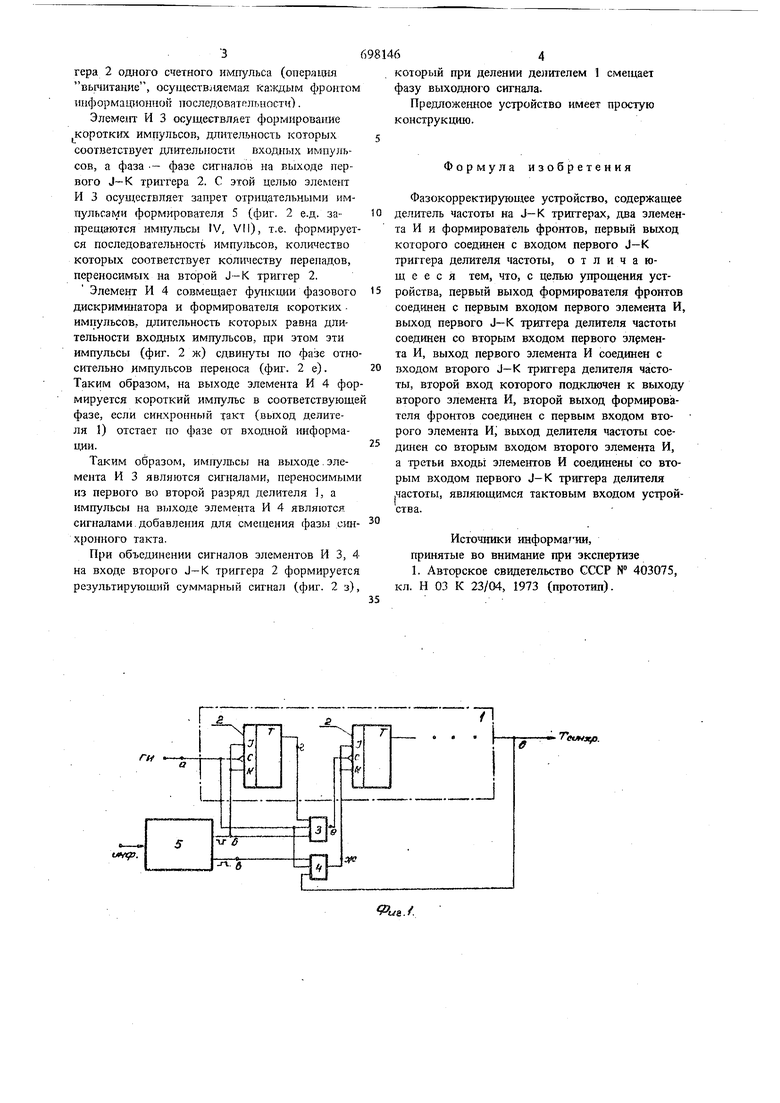

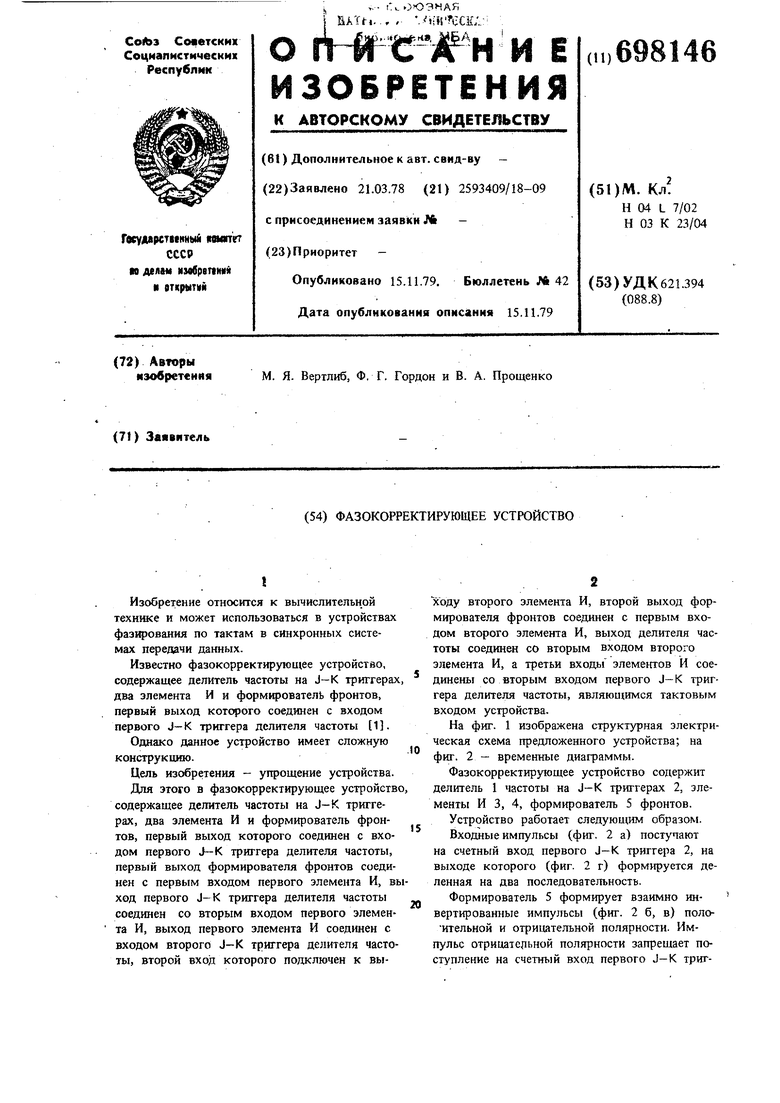

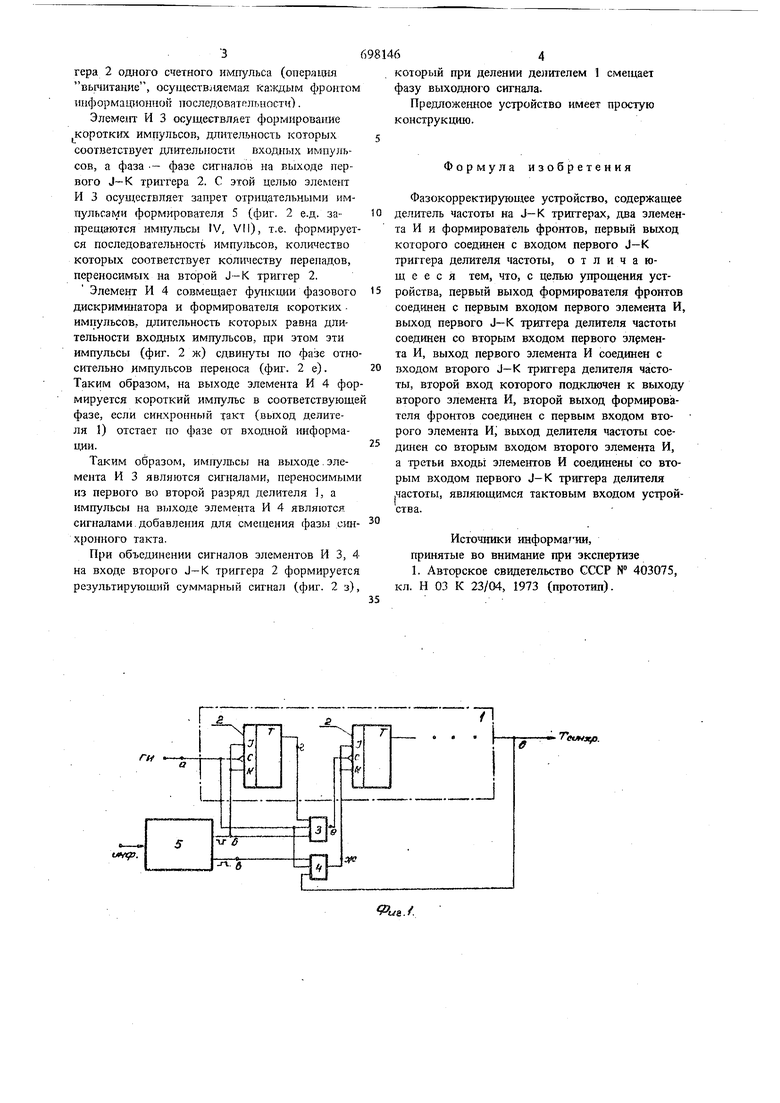

Изобретение относится к вычислитепьн.ой технике и может использоваться в устройствах фаз1фования по тактам в синхронных системах передачи данных. Известно фазокорректируюцее устройство, содержащее делитель частоты на J-К триггерах два злемента И и формирователь фронтов, первый выход которого соединен с входом первого J-K триггера делителя частоты 1. Однако данное устройство имеет сложную конструкцию. Цель изобретения - упрощение устройства. Для этого в фазокорректирующее устройств содержащее делитель частоты на J-K триггерах, два элемента И и формирователь фронтов, первый выход которого соединен с входом первого J-K триггера делителя частоты, первый выход формирователя фронтов соединен с первым входом первого элемента И, вы ход первого J-K триггера делителя частоты соединен со вторым входом первого элемента И, выход первого элемента И соед1шен с входом второго J-K триггера делителя часто ты, второй вход которого подключен к выходу второго злемента И, второй выход формирователя фронтов соединен с первым входом второго злемента И, выход делителя частоты соединен со вторым входом второго элемента И, а третьи входы элементов И соединены со вторым входом первого J- К триггера делителя частоты, являющимся тактовым входом устройства. На фиг. 1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 - временные диаграммы. Фазокорректирующее устройство содержит делитель 1 частоты на J-К триггерах 2, элементы И 3, 4, формирователь 5 фронтов. Устройство работает следующим образом. Входные импульсы (фиг. 2 а) поступают на счетный вход первого J-K триггера 2, на выходе которого (фиг. 2 г) формируется деленная на два последовательность. Формирователь 5 формирует взаимно инвертированные импульсы (фиг. 2 б, в) полоительной и отрицательной полярности. Импульс отрицательной полярности запрещает поступление на счетный вход первого J-K тригrepa 2 одного счетного импульса (операщш вьг штание, осуществляемая каждым фронтом ннформа1 :нонной последователыюсш). Элемелт И 3 осуществляет формирование коротких импульсов, длительность которых соответствует длт:ель}юсти входных импульсов, а фаза - фазе сигналов на выходе первого триггера 2. С этой целью элемент И 3 осуществляет запрет отрицательными импульсами формигрователя 5 (фиг. 2 е.д. запреща:ются им тульсы IV, VII), т.е. формирует ся последовательность импульсов, количество которых соответствует количеству перепадов, переносимых на второй J-K триггер 2. Элемент И 4 совмещает функции фазового дискриминатора и формирователя коротких импульсов, длительность которых равна длительности входных импульсов, при этом эти импульсы (фиг. 2 ж) сдвинуты по фазе отно сительно импульсов переноса (фиг. 2 е). Таким образом, на выходе элемента И 4 фор мируется короткий импульс в соответствующ фазе, если синхроЕтный -{-акт (выход делителя 1) отстает по фазе от входной информации. Таким образом, импульсы на выходе. элемента И 3 являются сигналами, переносимым из первого во второй разряд делителя 1, а импульсы на выходе элемента И 4 являются сигналами добавления для смепления фазы син хрошюго такта. При объединении сигналов элементов И 3, 4 на входе второго J-К триггера 2 формируется результирующий суммарный сигнал (фиг. 2 з) который при делении делителем 1 смещает фазу выходного сигнала. Предложенное устройство имеет простую конструкцию. Формула изобретения Фазокорректирующее устройство, содержащее делитель частоты на J-К триггерах, два элемента И и формирователь фронтов, первый выход которого соединен с входом первого J-K триггера делителя частоты, отличающееся тем, что, с целью упрощения устройства, первый выход формирователя фронтов соединен с первым входом первого элемента И, выход первого J-К триггера делителя частоты соединен со вторым входом первого элрмента И, выход первого элемента И соединен с входом второго J-К триггера делителя частоты, второй вход которого подключен к выходу второго элемента И, второй выход формирователя фронтов соединен с первым входом второго элемента И; вькод делителя частоты соединен со вторым входом BTOpoio элемента И, а фетьи входь элементов И соединены со вторым входом первого J-K триггера делителя .частоты, являющимся тактовым входом устройства. Источники информагии, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 403075, кл. Н 03 К 23/04, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазокорректирующее устройство с подстройкой частоты | 1980 |

|

SU882010A1 |

| Устройство для приема относительного биимпульсного сигнала | 1988 |

|

SU1614117A1 |

| Устройство импульсно-фазовой автоподстройки частоты | 1989 |

|

SU1737721A1 |

| Цифровой демодулятор сигналов с относительной фазовой модуляцией | 1981 |

|

SU985970A1 |

| Устройство для измерения времени синхронизации | 1980 |

|

SU930727A1 |

| Цифровой измеритель длительности периода | 1980 |

|

SU920556A1 |

| Устройство для контроля исправности цепей фазовращателя | 1983 |

|

SU1213441A1 |

| Устройство контроля амплитуды переменного напряжения | 1986 |

|

SU1354122A1 |

| Способ определения усредненного значения сдвига фаз и устройство для его осуществления | 1987 |

|

SU1499266A1 |

| Устройство синхронизации сигналов тактовой последовательности | 1984 |

|

SU1193788A1 |

.

etfHXf.

Авторы

Даты

1979-11-15—Публикация

1978-03-21—Подача