(5) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВРЕМЕНИ

«

Изобретение относился к технике электросвязи и может использоваться для проверки работы тактовой синхронизации дискретных систем связи, устройств контроля дискретных каналов и т.д.

Известно устройство для измерения времени синхронизации, содержащее формирователь тактовых импульсов, первый выход которого соединен с первым входом счетчика времени и со входом датчика кода, блок регистрации, первый вход которого является входом синхроимпульсов, а второй и третий входы соединены соответственно со вторым и третьим выходами формирователя тактовых импульсов, индикатор отстаивания фазы, индикатор опережения фазы, триггер и элемент задержки fl.

Однако известное устройство имеет длительное время измерения.

Цель изобретения - сокращение времени измерения. СИНХРОНИЗАЦИИ

Посталенная цель достигается . тем, что в устройство для измерения времени синхронизации, содержащее форг«)рователь тактовых импульсов, первмй выход которого соединен с первым входом счетчика времени и со входом датчика кода, блок регистрации, первый вход -которого является входом синхроимпульсов, а

,д второй и третий входы соединены соответственно со вторым и третьим выходами формирователя тактовых им; пульсов, индикатор отставания фазы, индикатор опережения фазы, триггер

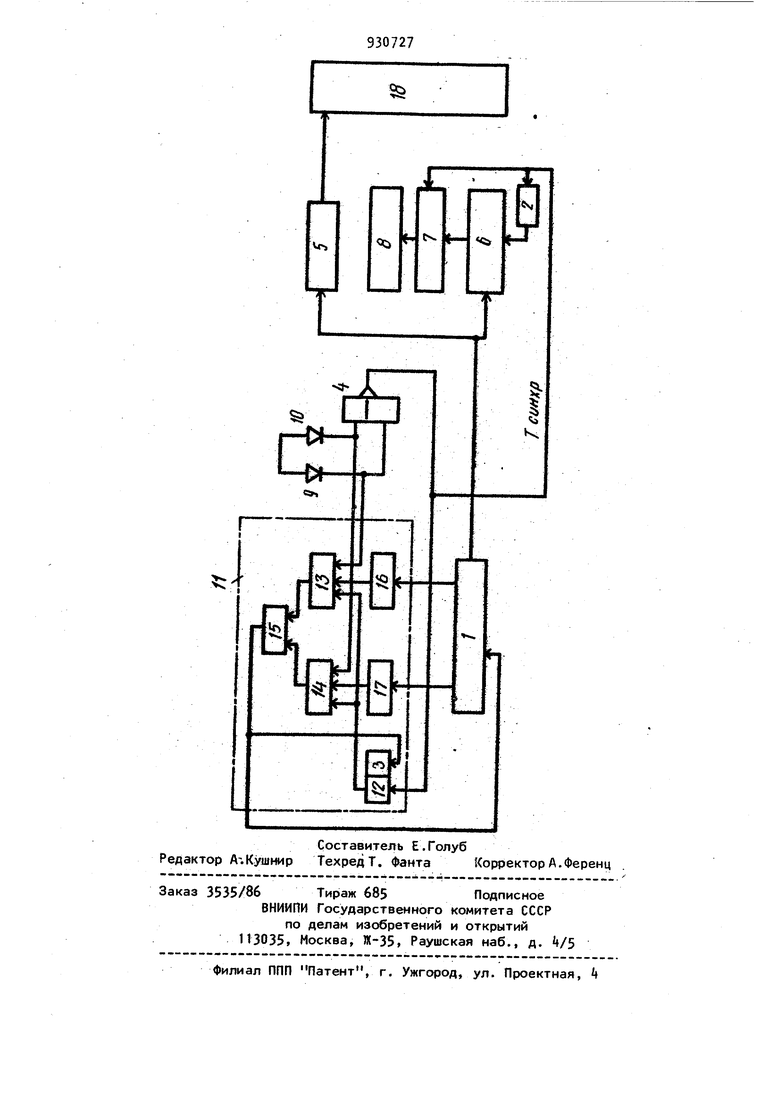

,j и злемент задержки, введены комму- , татор фазм, блок считывания и блок памяти, при этом выход блока регистрации соединен с первым входом комму татора фазы, со счетным входом тригJQ гера, с первым входом блока считывания и со входом элемента задержки, выход которого соединен со вторым входом счетчика времени, выход которого соединен со вторым входом блока считывания, выход которого сое динен со входом блока памяти, а первый и второй выходы триггера соединены соответственно с объединенными вторым входом коммутатора фазы и входом индикатора отставания фазы и с объединенными входом индикатора опережения фазы и третьим входом коммутатора фазы, четвертый и пятый входы и выход которого срединены соответственно с четвертым и пятым выходами и входом фор «1рователя тактовых импульсов. Причем коммутатор фазы выполнен в виде дополнительного триггера, выход которого соединен с первыми входами первого и второго элементов И, вторые входы и выходы которых соединены соответственно с анхоАамй первого и второго дешифраторов и с первым и вторым ходами элемента ИЛИ выход Kotoporo соединен со вторым входом дополнительного триггера, первый вход которого, третьи входы первого и второго элементов И,входы первого и втррого дешиф|эаторов и выход ИЛИ являются соответственно переем, аторым третьим, чет вертым и питым 8ХОДШ4И и выхбдом коммутатора фаз. На Чертеже дана ч труктурналэлект ричесйая схема Предлагаемого yet ройства. УстройсгИб для идйерения врейенй синхраииэаций содержит фор «ирова тель 1 такшвых импульсов, ta newBHT 2 задержки, блок 3 регистрацни, триггер 4, датчик 5 кода, счетчик 6 времени, блок 7 считывания, блок 8 памяти, индикатор 9 отставания фазы, индикатор to опережения фазы, коммутатор 11 фазы состоящий из дополнительного триггера 12, первого .13 и второго И элементов И, элемента ИЛИ 15 и первого 16 и второго 17 дешифраторов, кроме того на чертеже, показан измеряемый объект 18. Устройство работает следующим образом. Формирователь 1 тактовых импульсов формирует тактовые импульсы. В блоке 3 регистрации формируется импульс в середине синхронного такта, совпадение этого импульса с зоной регистрируется и оценивается как наличие синхронизма. Коммутатор 11 фазы содержит первый 16 и второй 17 дешифраторы, которые формируют импульсы, отстающие от границы такта на +{0,5Т-Д и -(0,5- Л), где Т - время вхождения в синхронизм; U - погрешность схемы. Элементы И коммутируемые триггером , пропускают поочередно с дешифраторов импульсы на элемент ИЛИ 15, при этом дополнительный триггер 12 разрешает -прохождение на элемент ИЛИ 15 только первого после регистрации си нхронизма импульса с соответствующего дешифратора. Из датчика 5 кода информация, совпадающая с тактовыми импульсами формирователя 1 тактовых импульсов, поступает на информационный вход измеряемого объекта 18, в схеме синхронизации которого начинается подстройка фазы синхронного такта. При совпадении зоньь сформированной в блоке 3, импульса середины синхронного такта, сформированного также в блоке 3 на его выходе формируется импульс, регистрирующий наличие бинхронизма. Этот импульс перебрасывает триггер Ц и взводит дополнительный триггер 12, который дает разрешающий потенциал на элементы И коммутатора 11, однако открыт будет один из них в зависимости от состояния триггера . Пусть открыт второй элемент И И. Тогда ближайший импульс второго дешифратора 17 через второй элемент И 14 и элемент ИЛИ 15 сбрасывает формирователь 1 тактовых импульсов, смещая при этом фазу Передающего такта на (0,5T-J) в сторону нап|5имер, опережения. ОдноЦременно задним фронтом импульса с шххэда э лемеита ИШ 15 сбрасывается дополните л ЬШЙ триггер 12, а импульс еи«хронизма из блока регистрации переносит через блок 7 изме 5€нную величину из счетчика 6 Btfeмени в блок в памяти и через элемент 2 задержки сбросит счетчик 6 времени. Поспе подтягивания фазы в измеряемом объекте 18 синхронный такт в блоке 3 регистрации вновь совпадает со сформированной зоной и на выхЗДе блока 3 вновь сформируется импульс. Триггер k переводится в другое состояние, при котором открывается первый элемент И 13 и закрывается второй элемент И 14. Одновременно сбрасывает дополнительный триггер 12, который открывает первый элемент И 13 по другому входу. Ближайии импульс отставания открывает первый элемент И 13 по другому входу. БлижаЙ11ИЙ импульс отставания на 0,5Т-& , формируемый первым дешифратором 16 через первый элемент И 13 и элемент ИЛИ 15 сбрасывает формирователь тактовых импульсов, а задний фронт этого импульса переводит дополнительный триггер 12 в исходное состояние запрещая прохождение через первый элемент И 13 последующих импульсов первого дешифратора 16. Одновременно импульсом с выхода блока 3 содер жимое счетчика 6 времени через блок переносится в блок 8 памяти, и через элемент задержки сбрасывается счетчик 6 времени. Теперь информация в датчике 5 кода вновь будет см щена по фазе на fO,5T-&) в сторону отставания и т.д. Следует отметить, что устройство измеряет максимальное значение времени синхронизации (так как смещение информации осуществляется на максимальную величину - на половину такта) и позволяет быстро проверить правильность работы схемы синхрониз ции при подтягивании фазы как в сто рону отставания,, так и в сторону опережения. Это окобенно важно при проверке аппаратуры контроля дискре ных каналов, в которой для получени большой точности определения матема тического ожидания местоположения синхронного такта используется малый шаг коррекции, большой коэффициент интеграции реверсивного счетчика, в результате чего время вхождения в синхронизм достаточно велико. Если время синхронизации в прове ряемой аппаратуре очень малое, то для разрежения быстроменяющихся показаний можно импульс переноса на вход блока 7 подключить через делитель (выборочная проверка). Таким образом, введение новых блоков значительно сокрацает время измерений. Формула изобретения Устройство для измерения времени синхронизации, содержащее формирова тель тактовых импульсов, первый выход которого соединен с первым вхоДОМ счетчика времени и со входом датчика кода, блок регистрации, первый вход которого является входом синхроимпульсов, а второй и третий входы соединены соответственно со вторым и третьим выходами формирователя тактовых импульсов, индикатор отставания фазы, индикатор опережения фазы, триггер и элемент задержки, отличающееся тем, что, с целью сокрацения времени измерения, введены коммутатор фазы, блок считывания и блок памяти, при этом выход блока регистрации соединен с первый входом коммутатора фазы, со счетным входом триггера, с первым входом блока считывания и со входом элемента задержки, выход которого соединен со вторым входом счетчика времени, выход которого соединен со вторым входом блока считывания, выход которого соединен со входом блока памяти, а первый и второй исходы триггера соединены соответственно с объедииенными вторь1м входом коммутатора фазы и входом индикатора отставания фазы и с объединенными входом индикатора опережения фазы и третьим входом коммутатора фазы, четвертый и пятый входы и выход которого соединены соответственно с четвертым и пятым выходами и входом формирователя тактовых импульсов. 2. Устройство по п. 1, о т п ичающеееся тем, что коммутатор фазы выполнен в виде дополнительного триггера, выход которого соединен с первыми входами первого и второго элементов Н, вторые входы и выходы которых соединены соответственно с выходами .первого и второго дешифраторов и с первым и вторым входами элемента ИЛИ, выход которого соединен со вторым входом дополни- i тельного триггера, первый вход которого, третьи входы первого и второго элементов И, .входы первого и второго дешифраторов и выход элемента ИЛИ являются соответственно первым, вторым, третьим, четвертым и пятым входами и выходом коммутатора фазы. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № , кл. Н 04 L 11/08, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПСИХОЛОГИЧЕСКИХ ИССЛЕДОВАНИЙ | 1992 |

|

RU2080091C1 |

| Адаптивный регенератор | 1986 |

|

SU1363490A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Анализатор распределения искажений сигнала | 1980 |

|

SU930726A1 |

| Устройство для сбора,обработки и отражения информации | 1972 |

|

SU451997A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ | 1991 |

|

RU2024968C1 |

| Устройство для измерения краевыхиСКАжЕНий | 1979 |

|

SU809627A1 |

Авторы

Даты

1982-05-23—Публикация

1980-07-02—Подача