динен с первыми входами к.тюча и через счетчик - триггера, выход триггера соединен с вторым входом ключа и первым выходом формирователя имиульсов, выход ключа соединен с вторым входом триггера и вторым выходом формирователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема избыточной информации | 1983 |

|

SU1101873A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152020A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема избыточной информации | 1988 |

|

SU1557578A2 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1107145A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

| Адаптивное устройство для приема избыточной информации | 1981 |

|

SU1001145A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для приема избыточной информации | 1982 |

|

SU1032470A1 |

1. АДАПТИВНОЕ УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗБЫТОЧНОЙ ИНФОРМАЦИИ, содержащее приемник, вход которого соединен с входом устройства, выход приемника соединенс первыми входами вычитателя, первого порогового селектора и первого блока памяти, выход первого порогового селектора подключен к входу первого блока регистров, первому входу декодера и второму входу вычитателя, выход вычитателя соединен с входом второго блока памяти, выходы которого соединены соответственно с первыми входами первых ключей и одновременно с выходами первого сумматора, выход первого су.мматора подключен к входу второго порогового селектора, выходы первых ключей соед 5иены соответственно с первыми входа.ми усилителей, первые выходы которых подключены соответственно к первым входа.м третьего порогового селектора, выход которого через генератор подключен к вторым входа.м усилителей, вторые выходы усилителей соединены соответственно с первыми входами вторых сумматоров, вторые входы которых подключены соответственно к выходам первого блока регистров, выходы вторых сумматоров соединень соответственно с первыми входами четвертого порогового селектора, выходы которого соединены соответственно с вторыми входами декодера, выход декодера соединен с первым входо.м второго блока регистров, первый выход которого подключен к выходу устройства, выход первого блока памяти соединен с первыми входа.м1 корреляторов, вторые входы которых подключены соответственно к вторым выхода.м второго блока регистров, выходы корреляторов соединены соответственно с первыми входам ; блока определения максимального сигнала, выходы которого соединены соответственно с вторыми входами второго блока регистров, отличающееся тем, что, с целью повышения достоверности обработки информации, в него введены задержки, второй и третий ключи, формирователь « импульсов, регистр, пятый пороговый селек(Л тор, умножитель и третий сумматор, выход первого порогового селектора соединен через линию задержки с первым входом второго ключа, выход которого соединен с вторыми входами первых ключей и блока определения максимального сигнала, выход первого блока па.мяти соединен с первым входо.м третьего сумматора, выход которого через последовательно соединенные умножитель и пятый пороговый селектор подключен к второму входу второго ключа, выход с декодера соединен с первым входом третьеto го ключа, выход которого подключен к первому входу регистра, первый выход регистра соединен с вторым входом третьего сумСП Ю матора, вторые выходы регистра соединены соответственно с входами формирователя импульсов, первый выход которого соединен с вторым входом третьего ключа, второй выход соединен с вторыми входами регистра и первого блока памяти. 2. Устройство по п. 1, отличающееся тем, что формирователь импульсов содержит элемент И, счетчик, ключ и триггер, входы атемента И подключены к входам формирователя и.мпульсов, выход элемента И сое

Изобретение относится к электросвязи, а именно к устройствам для приема избыточных сигналов в целом, и может найти применение в системах передачи дискретной информации, использующих избыточные коды большой мощности. Известны устройства для оптимальной обработки составных сигналов с избыточностью, формируемых на основе помехоустойчивых кодов. Эти устройства содержат перемножители, интеграторы и решающие блоки. Устройства реализуют способ приема в целом составных сигналов с избыточностью и обеспечивают высокую помехоустойчивость приема 1 и 3. Однако из-за сложности схемной реализации при обработке составных сигналов с избыточностью, формируемых на основе избыточных кодов с количеством информационных символов, больше тридцати, известные устройства практически нереализуемы. Известно устройство .T.IH неогггимальной обработки составных сигналов с избыточностью, реа.1изую1цее способ посимвольного приема сигналов и содержащее пороговый селектор, блок сравнения, решающий блок 2 . Недостатком такого устройства яв;1яется низкая помехоустойчивость приема избыточных сигналов. Наиболее близким к изобретению по технической сущности является адаптивное устройство для приема избыточной информации, содержац;ее приемник, вход которого соединен с входом устройства, выход приемника соединен с первы.ми входами вычитателя, первого порогового селектора и первого блока памяти, выход первого порогового селектора подключен к входу первого блока регистров, первому входу декодера и второму входу вычитателя, выход вычитателя соединен с входом второго блока памяти, выходы которого соединены соответственно с первыми входами первых ключей и одновременно с входами первого сум.матора, выход первого сумматора подключен к входу второго порогового селектора, выходы первых ключей соединены соответственно с первыми входами усилителей, первые выходы которых подключены соответственно к первым -входам третье о порогового се,пектора, выход которого через генератор подключен к вторым входам усилителен, вторые выходы уси,1итслей соединены соответственно с первыми вх(дами вторых сумматоров, вторые вход1 1 которьгх подключены соответственно к выхода.м первого б,1ока регистров, выходы вторых cyMMaiopoB соединены соответственно с перв1 1 1и входами четвертого пороговогч) се,тектора, выходы которого соединены соотве-1ственно с вторыми входа.ми декодера, выход декодера соединен с первым входом второго блока регистров, первый выход KOiOpoiO подк,1ючен к выходу уст|)ойства, выход первого блока памяти соединен с первыми входами корреляторов, BTOpijie вхядь которых подк.1ючены соответственно к ито)1з1м выходам второго блока peiMicTpo), вых()Д1)1 корреляторов соединены соответственно с пе|)зым11 входами блока опрсдс.леиия максимального сигнала, к(гго)ого соединен з1 соответственно с вто|) вхо. Bioporo б,тока регистров, выход nepiic.iri) iiopiifOBoro селектора соединен с вто)ы.м1; 1зходами первых ключей и блока опреде.чения максимального сигнала. Устройство характеризуется высокой онеративност1 10 обработки инфор.мации в систем,ах передачи данных, автоматизированных системах у1 рав;1ения, системах телеуправ.ления i-i те.песигнализации, системах передачи телеметрической информации и других системах передачи дискретной информации, использхющих составные сигналы с избыточностью, формируемые на оенове длин ных и сверхдлинных помехоустойчивых кодов 4. Недостатк(ш известного устройства яв.тяется низкая достоверность обработки информации, в случае, когда модуль градиента функции поавдоподобия превышает заданное значение, что вызвано относительной жесткостью реализованного в нем алгоритма принятия репкмтия. Независи.мо от того, на каком расстоянии от входного составного сигна.па с избыточностью находится сигнал, соответствующий преобразованию первой двоичной кодовой комбинации в разре1ненную, в случае, когда модуль градиента преБыи1ает заданное значение, алгоритм функционирования известного устройства фиксирован. Однако возможпл ситуации, при которых и в с,чучае превышения модулем градиента заданного значения разреп1ения

двоичная кодовая комбинация, соответствующая первой двоичной кодовой комбинации не является истинной.

Используемый в известном устройстве критерий максимального правдоподобия предполагает принятые решения в пользу той разрешенной комбинации, до которой расстояние от входного избыточного сигнала (или его оценки) наименьшее. При фиксированном канале (например, гауссов - канал можно задать отношение.м сигнал - шум), типе эле.ментарны.х канальных сигналов и известных параметрах помехоустойчивого кода можно указать расстояния Оз между избыточным сигналом и выходной разрешенной кодовой комбинацией, превышение которого свидетельствует (с определенной вероятностью) об ошибочности решения. Соответственно можно вычислить при выше оговоренных ограничениях величину оэффициента корреляции Kj. Если коэфициент корреляции К между разрешенной кодовой комбинацией и избыточным сигналом К Кз то решение в пользу этой раз решеннойкомби-нации является ошибочным.

В известном устройстве при превышении модулем градиента заданной величины решение всегда принимается в пользу разрешенной комбинации, соответствующей входной (первой) двоичной комбинации декодера. При этом не учитывается отмеченное соотношение расстояний (коэффициентов корреляции). Если, например, коэффициент корреляции меньше заданного, решение по этой омбинации ошибочное, а это уменьшает остоверность обработки информации.

Цель изобретения - повышение достоверости обработки инфор.мации за счет учета при принятии решения инфор.мации о величине коэффициента корреляции между первой разрешенной кодовой комбинацией и избыточным сигналом в случае превышения модулем градиента функции правдоподобия заданной величины.

Указанная цель достигается тем, что в адаптивное устройство для обработки избыточной информации, содержащее приемник, вход которого соединен с входом устройства, выход приемника соединен с первыми входами вычитателя, первого пороговоо селектора и первого блока памяти, выод первого порогового селектора подклюен к входу первого блока регистров, первому входу декодера и второму входу вычитателя, выход вычитателя соединен с входом второго блока па.мяти, выходы которого соединены соответственно с первыми входами первых ключей и одновременно с входами первого су.мматора, выход первого сумматора подключен к входу второго порогового селектора, выходы первых ключей соединены соответственно с первыми входами усилителей, первые выходы которых подключены соответственно к первым входам третьего порогового селектора, выход

которого через генератор подключен к вторым входам усилителей, вторые выходы усилителей соединены совтветственно с первыми входами вторых сумматоров, вторые входы которых подключены соответственно к выходам первого блока регистров, выходы вторых сумматоров соединены соответственно с 1ервыми входамп четвертого порогового селектора, выходы которого соединены соответственно с вторыми входами декодера, выход декодера соединен с первым входом второго блока регистров, первый выход которого подключен к выходу устройства, выход первого блока памяти соединен с первыми входами корреляторов, вторые входы которых подключены соответственно к вторым выходам второго блока -регистров, выходы корреляторов соединены соответственно с первыми входами блока определения максимального сп1нала, выходы которого соединены соответственно с вторыми входами второго блока регисгров, введены линия задержки, второй и третий ключи, формирователь импульсов, регистр, пятый пороговый селектор, умножитель и третий сумматор, выход первого порогового селектора соединен через линию задержки с иервым входо.м второго ключа, выход которого соединен с вторыми входами первых ключей 11 блока определения максимального сигнала, выход первого блока памяти соединен с первым входо.м третьего сумматора, выход которого через последовательно соединенные умножитель и пятый норо|-овый селектор подключен к второму входу вторО1о ключа, выход деко.чера соединен с первым входом третьего к.1К)ча, ыход которого подключен к нерному нлоду регистра, первый выход регистр; соединен с вторым вх() третьего сумматора, вторые Biiixo. pciHcтра соединены соответственно с входами формирователя импульсов, нервый выход которого соединен с вторым входом третьего ключа, второй соединен с вторыми входами регистра и первого блока памяти. Причем формироватсмь нмих. содержит элемент И, счетчик, ключ и триггер, входы э.юмепта 11 нодключспы к входам формирователя 1 мпу:1ьс()в, выход э.темепта И соединен с первыми входами ключа н через счетчик - триггера, выход тригггера соединен с вторым входо.м ключа н первым выходо.м формирователя и.мпульсов, вьгход ключа соединен с вторым входом триггера и вторым выходом формирователя импульсов.

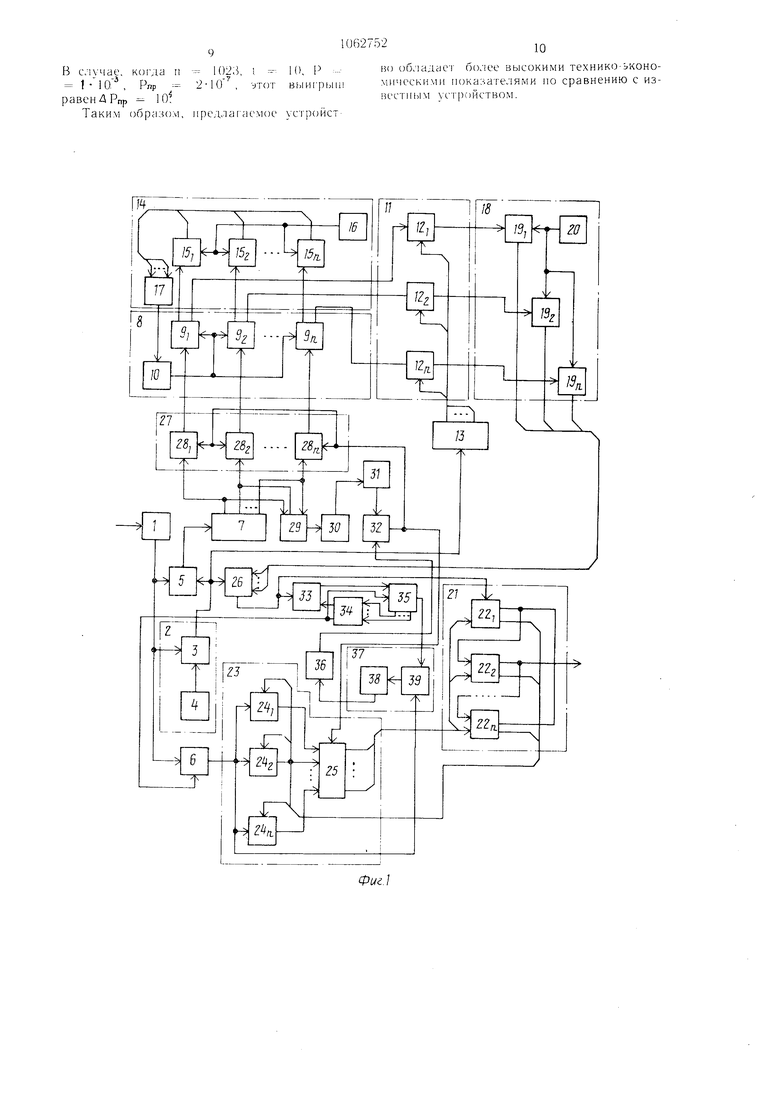

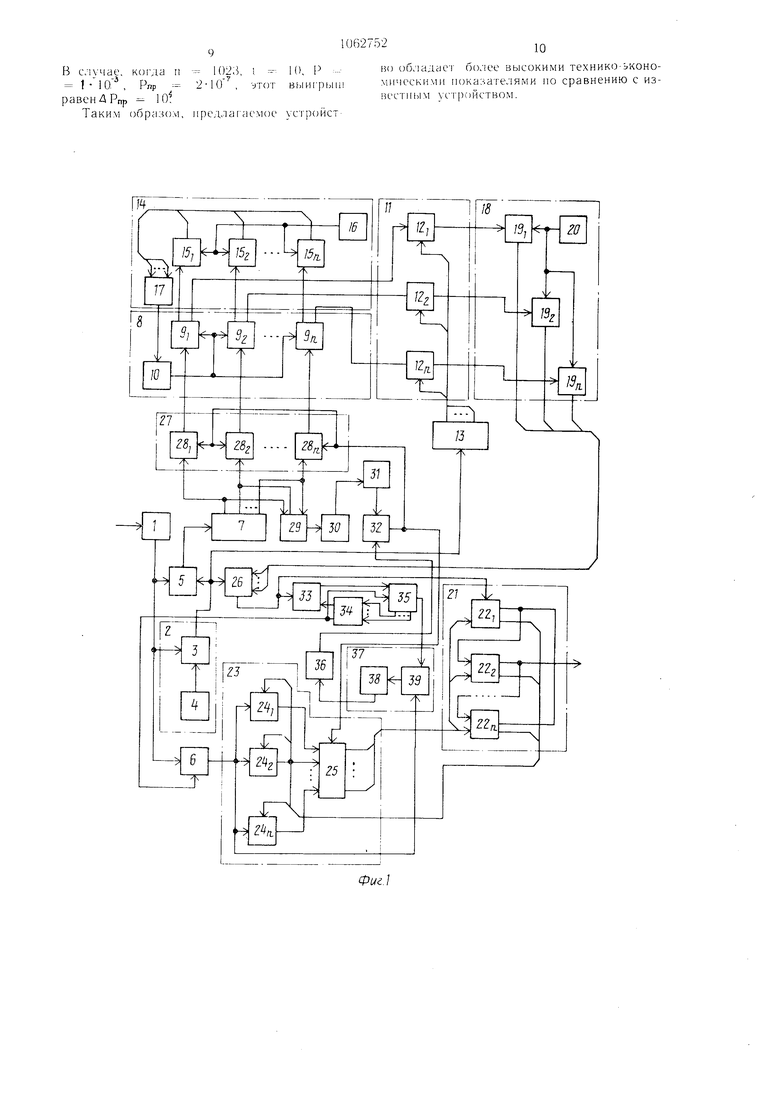

На фиг. 1 изображена структурная схе.ма адаптивного устро11ства для обработки избыточной информации; на фиг. 2 - функциональная схема фop н poнaтeля имнульсов; на с|зпг. 3 функциональная схема второго блока pciiiCTpoB.

А.тантивное ycTpoiicTBo для обработки избыточной информации содержит приемник 1 (аналоговый демоду.чятор), пороговый селектор 2, э.че.мСП 3 сравнения, источник 4 порогового напряжения, В1з читате;1ь 5, блоки 6 и 7, (|)е)11ой памяти, б.юк 8 усилителей. усил1ггел11 9, генератор К) линейно измепяклцегоен иаиряжеиия, блок 11 сумматоров, суммаi4 j)i)i 12, блок 13 регистров, пороговый селектор 14. э.к-меит 15 cpaBiieния, источник И) порогового нанряження, н{)р01ч)В1)1Й блок 17, пороговый селектор 18, элеме ггы 19 сравнения, источник 20 поро|О 5ого на11()яжения. блок 21 ре истров. ре1Т-1етры 22. блек 23 норО|-ово Ч) нанряжения, блок 21 регнстро.в, решстры 22, блок 23 унрав.чения выдачей информации, корре.тято)ы 24, б.юк 25 онреде.чения максимального , декодер 26, блок 27 ключей, ключи 28. сумматор 29, норогов1)1Й селектор 30, .чиния 31 :1адержки, ключи 32 и 22 формировате;1ь .:1ьсов 34, регист) 35 сдвига, пороговый (чмектор ii(). блок 37 опенки качества решения, умножиПЛ 38, еумматор 39, -лтемент 40 И, двоичный счетчик 41, ключ 42, 43, регистры 44. При превьпиенин вьгходным сигиа.том сумматора 29 noporoiioro значения. В1 1рабатываемогс) в ио|10 овом селекторе 30, на выходе носледнего ноявляетея уиравляющий си1Л1а.1, но которому с номои).ыо б.пока 26: определения максимального сигнала из блока 21 на вьгход устройства считывается первая )азре1иенная кодовая комбинация. В предлагаемом устройсп е пе)вая )азрен1енная комбинаг.ия из б.юка 21 счит1)1вается то.чько в с.чучас (при тех же оиисаииых ограничениях), когда выходной сигпа.л б.лока 37 бо.чьше и.ш равен заданиому значению. При JTOM решение принимается уже не но oдн(JЙ (как в известном ует1К)йстве) двоичиой Ko;ioBoii комбинаииг;. а по п комбинациям, что и обесиечинает повыи1ение достоверности ириш маемой иифо)маиии (при этом нрмнятие решения осудгествляетея с iioMonibio процедуры градиентного дексхчироваиия в целом). Очевидно, что, как в известном ч-тройстве, алгорит.м фуикциоиирования иредлагаемсхч) устройства имеет тем больше достоинств, чем длиннее коды. исиользуем1з1е д.тя формирова 1ия составн1 г сигна;1ов с избыточностью. Адаптивное уст1)ойетво pa6cjTaeT еледуюгцим образом. На вход апа.тогового демодул}Г1о К 1 поступает сложный пзбыточшз1Й си1Т1а.т. Па выходе аналогового деккмодулятора 1 появляется (например, иос.кдовательио во времени) совок т1носгь аналогов1)1х сигналов, соответствующих элементам входи.о1Ч) .та. Каждьп аналогов1)1Й подается на вход порогового ee.ieKTopa 2, а именно на вход элемента 3 сравнения, на другой вход которого поступает пороговое нанряжение от источника 4 порогового иаиряжения (величина этого нанряження устанавливается как и в известном устройстве вручную). Величина юрогового напряжения определяется отношением сигна,шум в кана,те езязи, 11арамет)ами избьггочного кода и способом об аботки элементарных сигналов в аналоговом демодуляторе 1. В элементе сравнения 3 осуществ;1яетея сравнение входных сигна.тсВ. Есл.и величина вxoдн(JГo ана;1огового си1Л1 ла меньше ве,тичииы иорогового Haiipn/i uHHH, на выходе элеме1гга с;)авнения нояи.пнется сигна.т «О, в иротив|1ом с.1учае - сигна,; «1, определяемый H(j величине отношения сигнал шум, параметрам избыточного кода и способу приема. Г1;)1 ример, амплитуда его напряжения может бьггь равна Н. Она еоответетвует неискаженному единичному сигна,1у ( этом считается, что на длите;1ьносТ1-( Т ц-С o|нoиJeниe еигнал - И1ум не и.змеп5:е с.я. |-де С д.тите.тьноеть э:1ементарного кана, Ы1О1Ч; сиглшла). Таким образо.м, afia,ioгoвый си1 iia.i преобразуется в ДЕ ОИЧИЫЙ. В вычи iare;ie 5 из ве.шчипы а1галогового cHiTia.ia вычиггают ве.чичииу двоичного сигнала. В резу; ьтате этого в декодере 26 пос.ледовате.1ьно записываегсн двопшая ко;1()вая ко.мбииа11пя. соответствук;Пи1Я поси.мв(;,11Л1ому jeiiieiMK) по 1 ходном ана.юговому CHifia.iy. Декодер после выполнения соответствукицпх опе|)адий в региетр 22 заиисывае (и(.Нлс-;и)вате.) двоичную раз)еи1енну1о КОДОВУЮ комбинацию, являющуюся ближайшей к двоичной иосимвольной. В б.кж 13 |1сгие ров также заниеьн ается и Х 1а1;ится эта ;1,1«И чг;ая кодовая комбинаП.ИЯ. В б,1оке 7 6y(.j)epiioii иа.мяти занисыва1ГГСЯ coiiOKx пиость ана.юговых icHHiViX с выхехча вычич ате11з o.ijKu / эг1 ciiina.iij паралле.чьно подаюгся на 1П{|)о|)мацио1 Ные входы закрыTbix в исходном сосгояни.и ключей 28 и на входы многовхочово о сум.матора 29, в кого)ом вычис.)т абсо.чютньгх велииа.ю блока 7 (выходные и в/1 я кл ся потении ал ьны д, ге.Ч.ности. | ходнои сигнал селектора liiiiie величины иорогового наиряжен ;я.. з;;лр:;:вак)ший ключи б.мока 27 се.чектора 30 не отключачии этого сигнала в соот.;еи1 времени из блока 23 i;i(4 рав.1якиций сигнал, выход устройства хранящуюся в liCM рпзреше-ИУю кодовую комбинацию (и.И ее информацио1Ц1ую часть). Ес,ли входиой сигнал селектора 30 окажется меньше величи:чы порогового напряжения, еигна.т за.лрета с выхода селектора 30 отключается. При эгом он снимается и с входом блоков 23 и 27, вследствии чего алгоритм работы блока 23 приводится к тому же виду, что и в известном устройстве. Ключи 28 блока 27 открываются и из блока 7 сигналы также подаются на усилители 9. Однако выходной сигнал порогового селектора 30 подается на управляющие входы блока-27 ключей и блока 23 управления вы дачей информации через линию 31 задержки и открытый в исходном состоянии ключ 32. Поэтому в дополнение к описанному (т.е. к случаю, когда ключ 32 открыт) расс.мотрим ситуацию, когда ключ 32 закрывается. Первая разрешенная двоичная кодовая комбинация с выхода декодера 26 через открытый в исходном состоянии ключ 33 последовательно записывается также в двоичный регистр 35 сдвига. После заполнения всех ячеек памяти регистра 35 на выходе элемента 40 И формируется сигнал, который подается на счетный вход двоичного счетчика 41 и на информационный вход ключа 42 (открытого в исходном состоянии). Проходя открытый ключ, этот сигнал изменяет состояние триггера 43.(его исходное состояние единичное) на нулевое и подается на считывающий сигнал в блоки 6, 35. Выходной сигнал триггера 43 закрывает ключи 42 и 33. Триггер 43 приводится в исходное состояние (а следовательно, и ключи 42 и 33 импульсом переполнения счетчика 41 (он появляется после обработки декодером п-й двоичной комбинации). По сигналу считывания, вырабатываемому в формирователе импульсов 34, синхронно из регистра 35 и 6 на входы умножителя 39 считываются соответственно первая разрешающая двоичная кодовая комбинация и аналоговый составной сигнал с избыточностью. Результаты пере.множения накадливаются в сумматоре 39. По окончании обработки входных составных сигналов на выходе блока 37 фор.мируется сигнал, который сравнивается в селекторе 36 с пороговым сигналом. Если выходной сигнал блока 37 меньше порогового, на выходе селектора 36 формируется управляющий сигнал, закрывающий ключ 32. В противном случае ключ 32 остается в исходном (открытом) состоянии. После того, как из блока 7 сигналы параллельно поданы на усилите ти 9 запускаются генератор 10 линейно-изменяющегося напряжения и коэффициент усиления усилетелей 9 увеличивается (начальный коэффициент усиления равен 1). Выходные сигналы усилителей 9 подаются на элементы 15 сравнения, к другим входа.м которых подключен источник 16 порогового напряжения. Как только в каком-нибудь элементе 15 сравнения выходной сигнал усилителя превысит величину порогового напряжения, еразу же срабатывает пороговый блок 17 и генератор 10 линейно изменяющегося напряжения выключается. Усиленные сигналы с выходов усилителей 9 подаются на входы соответствующих одноразрядных сумматоров 12, где суммируются с величинами сигналов, поступающих на другие входы сумматоров 12 с ячеек памяти блока 13 регистров. Далее результирующие сигналы преобразуются в дво ичные сигналы посредством элементов 19 сравнения и источника 20 порогового напряжения, после чего параллельно поступают в декодер 26. Сформированная декодером 26 разрещающая двоичная кодовая комбинация, ближайщая к полученной, записывается в регистр 22, сдвигая первую комбинацию в регистр 222. После этого опять запускается генератор 10 линейно из.меняющегося напряжения, осуществляются - выще описанные операции и в регистр 22 записывается следующая разрещенная двоичная комбинация, а ранее записанные комбинации переписываются в регистры 222 и 22, и т.д., пока все п регистров не будут заполнены. Далее блок определения 25 максимального сигнала считывает из регистров 22 комбинации (с регенерацией) в корреляторы 24, на другие входы которых подается комбинация аналоговых величин из блока 6 буферной памяти. Величины выходных сигналов корреляторов 24 соответствуют коэффициентам корреляции соответствующих комбинаций. Эти сигналы поступают в блок 25 определения .максимального сигнала, в котором определяется максимальный из них, и соответствующая .максимальному сигналу двоичная кодовая комбинация из блока 21 считывается на выход устройства. Далее все элементы памяти очищаются и устройство готового к обработке следующего сигнала. Предлагаемое устройство обладает более высокими технико-экономическими показателями по сравнению с известным устройством. Техническое преимущество изобретения по сравнению с базовым объектом заключается в том,, что в предлагаемом устройстве рещение по первой разрещенной кодовой комбинации принимается только в случае, когда степень подобия этой комбинации входному сигналу с избыточностью не меньше заданной. Положительный эффект изобретения, по сравнению с базовым объекто.м, заключается в повышении достоверности обработки информации за счет более точного принятия ПО первой разрешенной двоичной кодовой комбинации. Ориентировочный выигрыш по достоверности принятия решения .можно оценить как .1:СРЧ1-Р)- ёюр 1 .i cl

в случае, когда п- 1()2;5, 1 , Р - ., Рпр -- --2 10 , ;1ТОТВЫИ|-рЫ11

равенДРпр --10

Таким образом,iipe/waracMoeустройст10

во обладает более высокими технико-экономическими ||(жа.ателями ио сравнению с извести I,IM устройством.

5

П

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Финк Л | |||

| И | |||

| Теория передачи дискретных сообщений | |||

| М., «Советское радио, 1970, с | |||

| АВТОМАТИЧЕСКИЙ РЕГУЛЯТОР ДЛЯ ВОДЯНЫХ ТУРБИН | 1923 |

|

SU635A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ..Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М., Советское радио, 1968, с | |||

| Приспособление для уменьшения дымовой тяги паровоза | 1920 |

|

SU270A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Г., Коробов Ю | |||

| Ф | |||

| Теория передачи сигналов | |||

| М., «Связь, 1972 | |||

| с | |||

| Регулятор для ветряного двигателя в ветроэлектрических установках | 1921 |

|

SU136A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1983-12-23—Публикация

1982-08-17—Подача