(54) АДАПТИВНЫЙ ПОРОГОВЫЙ МОДУЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное пороговое логическое устройство | 1977 |

|

SU739524A1 |

| Коммутирующее устройство | 1986 |

|

SU1510075A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

| Устройство синхронизации М-последовательности по задержке | 1986 |

|

SU1398106A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1322315A1 |

| Тренажер операторов систем управления | 1988 |

|

SU1520573A1 |

| Имитатор дискретного канала связи | 1984 |

|

SU1223246A2 |

I

Изобретение относится к области вычислительной техники и предназначено для использования в качестве центрального элемента в обучаемых классификаторах, в частности в классификаторах неисправностей различных техиических объектов.

Известен пороговый модуль, содержащий регистр, сумматор, схему настройки и генератор 1 . Недостатком его является низкое быстродействие.

Наиболее близкое техническое решение к изобретению - адаптивный пороговый модуль, содержащий схему сравнения, сумматор, регистр счетчик, элемент запрета, информационные входы которого соединены с выходами счетчика, а запрещаюишй вход через первый элемент задержки соединен с входом счетчика.

Каждый разряд модрт(я содержит первый элемент И, счетчик, элемент запрета, информационные входы которого соединены с выходом счетчика, настроечный вход которого соединен с соответствующим выходом регистра, а счетный вход через элемент задержки соединен с запрещающим входом элемента запрета и с выХОДОМ первого элемента И, первый вход которого является разрядным входом устройства. Выходы всех элементов запрета устройства соединены с входами сумматора, выход которого является выходом устройства и соединен с первым входом схемы сравнения, второй вход которой является входом устройства и соединен с входом регистра 12}. Устройство содержит кроме того, генератор. Недостатком его является низкое быстродействие.

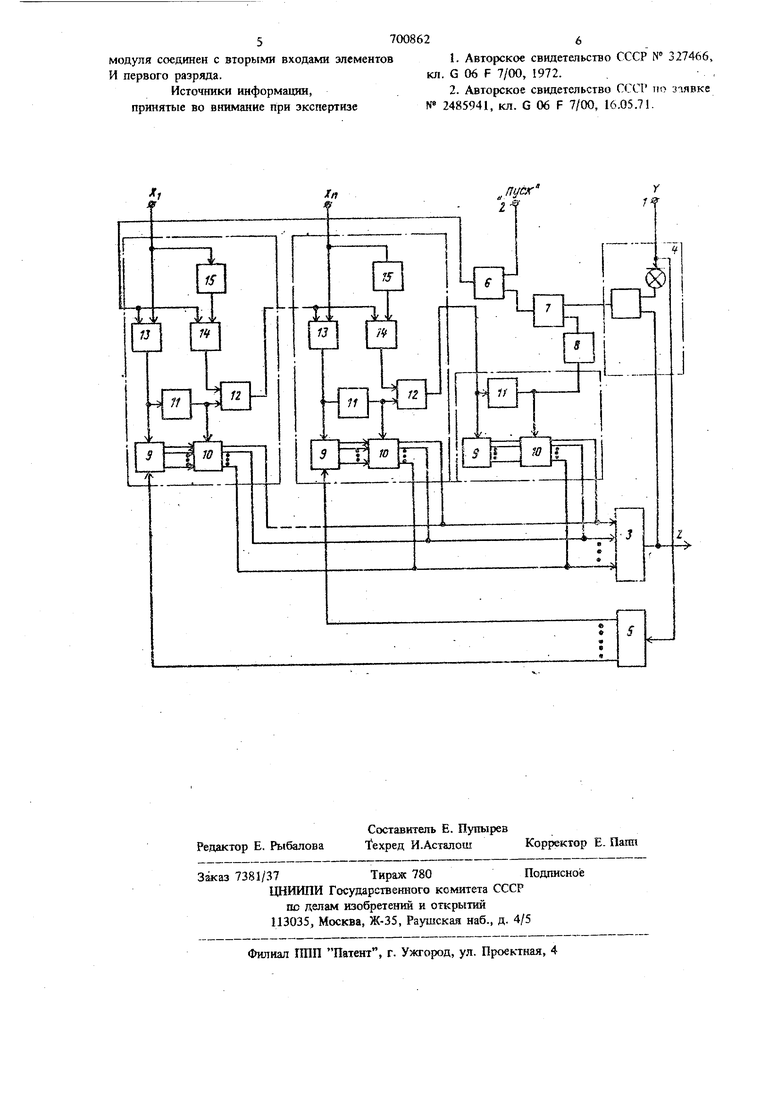

Целью изобретения является повыщение быстродействия. Цель достигается тем, что модуль содержит элемент И, элемент ИЛИ, второй элемент задержки и, кроме того, в каждом разряде второй элемент И, элемент ИЛИ, элемент НЕ, причем первый вход элемента ИЛИ каждого разряда соединен с выходом элемента задержки, второй вход - с выходом второго элемента И, первьш вход которого через элемент НЕ соединен с разрядным входом модуля. Выход элемента ИЛИ каждого разряда, кроме последнего, соединен с вторыми входами элементов И следующего разряда. Выход эле, мента ИЛИ последнего разряда соединен с вто37рым входом первого элемента задержки, выход которого через второй элемент задержки со- единен с первым входом элемента И, второй вход которого соединен с выходом схемы сравнения, а выход подключен к первому входу элемента ИЛИ, второй вход которого является вторым входом модуля. Выход элемента ИЛИ модуля соединен с вторыми входами злементов и первого разряда. На чертеже показана схема предлагаемого модуля. На схеме приняты следующие обозначения: 1 - первый вход модуля, 2 - второй вход мс дуля, 3 - сумматор, 4 - схема сравнения, 5 - .регистр, 6 - элемент ИЛИ, 7 - элемент И, 8 элемент задержки, 9 - счетчик, 10 - элемент запрета, 11 - элемент задержка, 12 - элемент ИЛИ, 13 и 14 - элементы И, 5 - элемент НЕ Адаптивный пороговый модуль работает следующим образом. При появлении на разрядных входах Xj, Х2 ..., Х комбинации логических едж-шц и кулей на вход 2 подается импульс, который через эле мент 6 ИЛИ поступает на входы элементов И 1 и 14. Если на входе Xj присутствует логическая еданица, импульс проходит через элеммгг И 13, счетный вход счетчика 9 и через элемент задерж ки 11 на вход элемента запрета Ш и один из входов элемента 12. При этом запксанное в счетчике 9 весовое значение в виде параллель ного двоичного кода взо/ддтгся в сумматор 3. Если на входе Xj присутствует логическкр нуль, пусковой импульс проходит через зпамент И 14 и без задержки поступает ка второй вход элемента ИЛИ 12, и значение весь} з сумматор не вводится. С выхода элемента ИЛИ 12 импульс поступает на входы элементов И 13 и 14 следзтощего разряда. Tlyni прохождения импульса, по второму и последуюш {м разрада;аналогич и зависят от значения перерленной на входах этих разрядов. С выхо.ца посу.еднего разр5ща импульс . на с«етг.ый в;;-.оя счетчика и через элемент задержки 11, OiKpi-vвая элемент запрета 10, вводт- в суммйтор 3 значенир порога. На этом цикл опроса разрядов закадг ягется. Если ситная Z на выходе :з мматсра 3 тличается от требуемого сигнала-ка зхсдг 1. схема сравнения 4 имеет на окоем выходе логя ческую единицу, и импульс с элемента задержки И через элемент задержки 3 Itflim обратной связи, элемент И 7, э.п лгг;нт ИЛИ б поступит вновь на вход первого разряда. Цикл настройки повторяется. Процйсс н:астройки заканчивается при совщщеник сйтн;-ша Z на входе сумматора с требуемым сигналом. При этом схема сравнения 4 сигналом лоп;ческого нуля запрещает прохождение импульса через злемент И 7. Элементы задержки в разрядах необходимы для того, чтобы перезапись в сумматор кодов из счетчиков происходила после окончания переходных процессов при счете и суммировании. Техническая эффективность предлагаемого порогового модуля зависит от количества разрядов. С увеличением их числа экономия времеш возрастает, что скажется на быстродействии устройства, в состав которых центральным узлом входит предлагаемый пороговый модуль. Формула изобретения Адаптивный пороговый модуль, содержащий сумматор, схему сравнения, регистр, счетф:{(с, элемент запрета, информационные входы которого соединены с выходами счетчика, а запреащющш вход через первь5Й элемент задержки сое;щнен с входом счетчика, разряд модуля содержит первый элемент И, счетчик, элемент запрета, инфсрманиош&ш входы которого соеддкены с выходами счетшка, настроечный вход которого с соответстзую1Ц) выходом регистра, счетный вход счетчика через элемент задержки соединен с запрещающим входом элемента запрета н с выходом первого элемента И, первый вход которого является разрядным входом модуля, выходы всех элементоа которого соедикекы с входами сурлматора, выход которого является выходом модуля и соединен с пгрвь м входом схемы сравныям, второй вход которой является входом модуля и соед1шен с входом регистра, отличающийся тем, что, с целью повышения бьЕстродеГютвия. модуль содержит элемент И, эл емент ИЛИ, второй элемент задержки и, кроv;e того, D кэяздом разряде второй злемент И, элемент ИЛИ, элемент НЕ, причем первый вход элемента ИЛИ каждого разрят(.а соединен с выясдом элемента задержки, второй вход - с выходом второго элел5ента И, первЕ.ш вход которого через элемент НЕ соединен с разрядным входом модуля, элемента 1-ШИ кйждсго разрядд, кроме последнего, соединен с вторыми входами элементов И следующего разряда, выход элемента йЛИ последнего разряда соединен с вторым входом первого элемента задержки, выход которого через второй э.пемент задержки соединен с первым входом элемента И, второй вход которого соединен, с выхо.гдом схемы сравKQiiKH, а выход подключен к первом входу элемента ИЛИ, второй вход которого является BTopbiM входом модуля, выход элемента ИЛИ

57008626

модуля соединен с вторыми входами элементов1. Авторское свидетельство СССР № 327466,

И первого разряда.кл. G 06 F 7/00, 1972.

Источники информащш,2. Авторское свидетельство СССР тю заявке

принятые во внимание при экспертизеF 2485941, кл. G 06 F 7/00, 16.05.71.

Авторы

Даты

1979-11-30—Публикация

1978-01-03—Подача