113

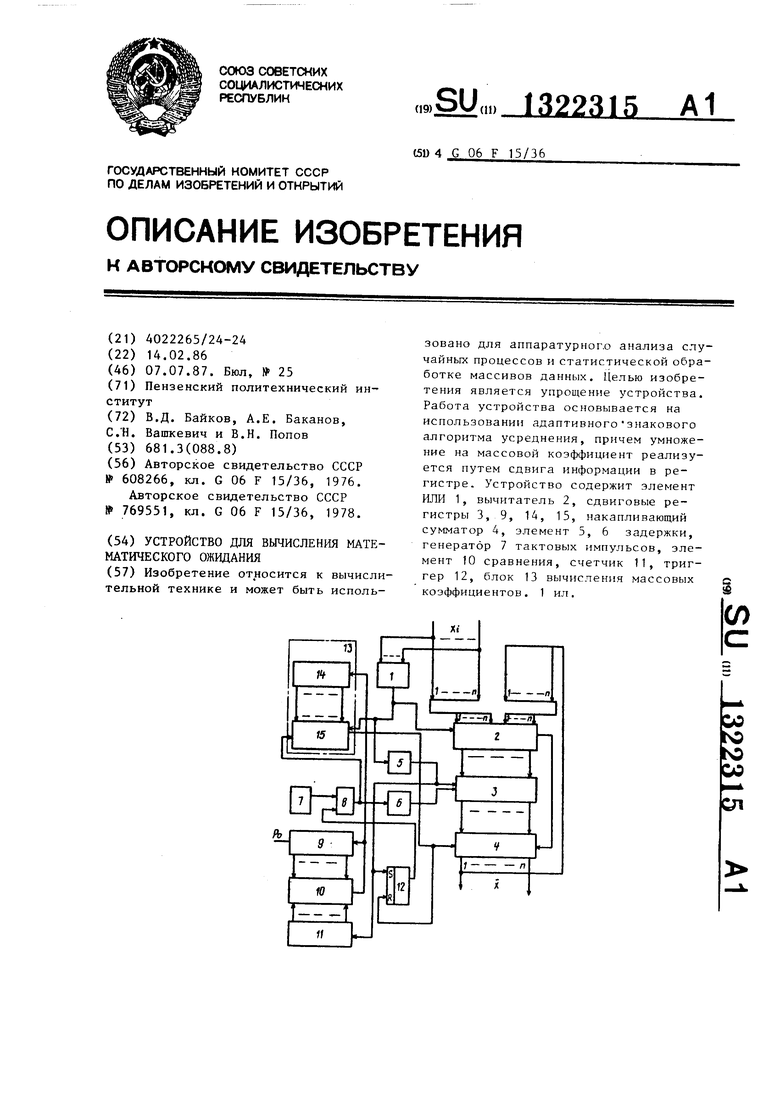

Изобретение относится к вычислительной технике и может быть использовано для аппаратурного анализа случайных процессов и статистической обработки массивов данных.

Цель изобретения - упрощение устройства.

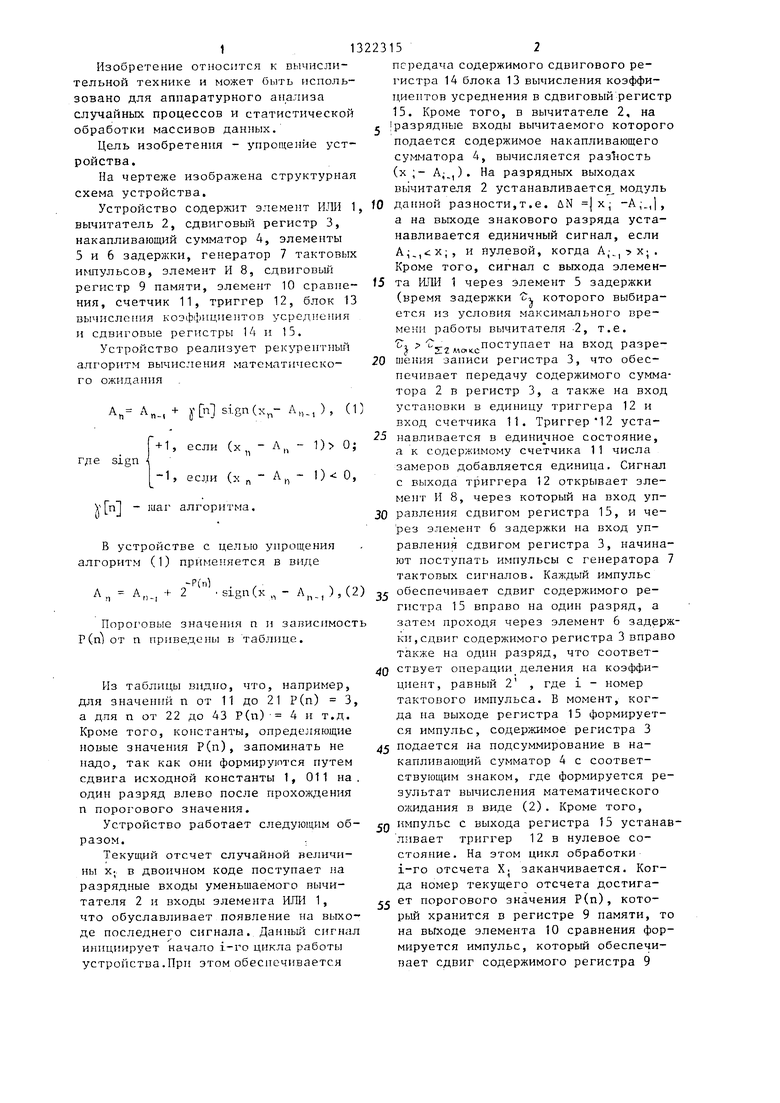

На чертеже изображена структурная схема устройства.

Устройство содержит элемент ИЛИ 1, вычитатель 2, сдвиговый регистр 3, накапливающий сумматор 4, элементы 5 и 6 задержки, генератор 7 тактовых импульсов, элемент И 8, сдвиговый регистр 9 памяти, элемент 10 сравне- НИЛ, счетчик 11, триггер 12, блок 13 вычисления коэффициентов усреднения и сдвиговые регистры 14 и 15.

Устройство реализует рекурентньш алгоритм вычисления математическо- го ожида1П1я

А А„, + sign( А„, ), (1)

где sign

+ 1, если (х,, - А,, - 1) 0;

если (х

(х„- А,- ,

Т- шаг алгоритма,

в устройстве с целью упрощения алгоритм (1) применяется в виде

А, А„, + .sign(x,- А,),(2) 35

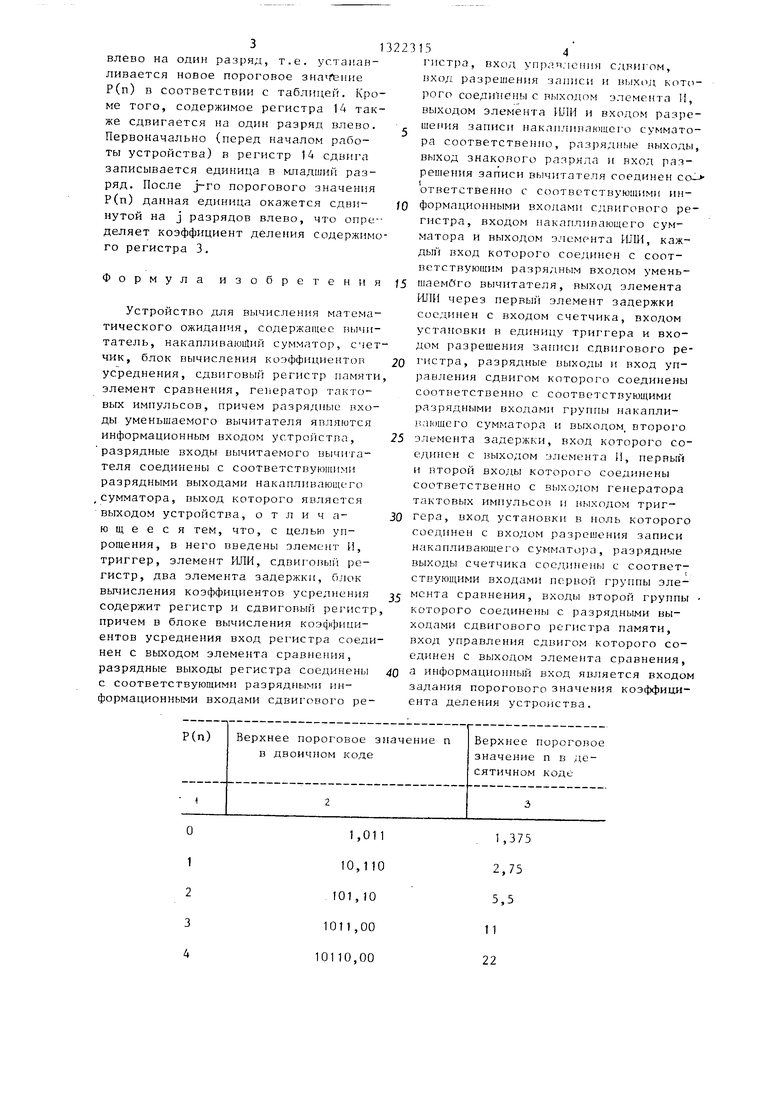

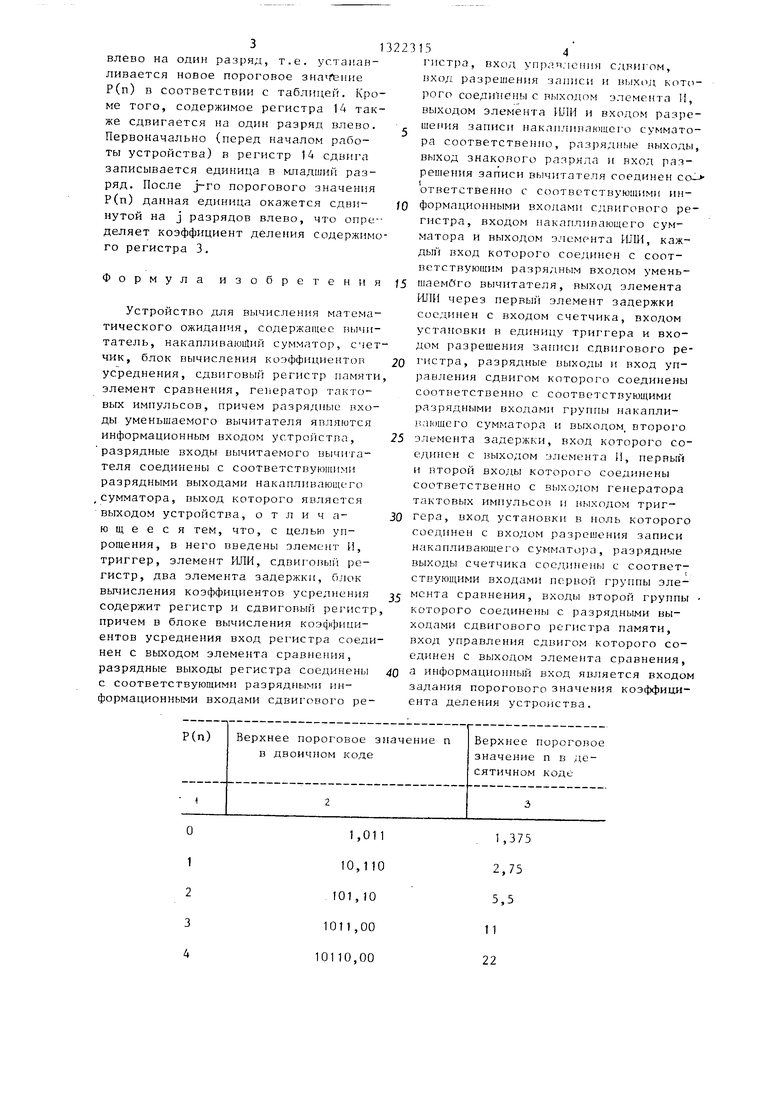

Пороговые значения п и зависимость Р(п) от п приведены в таблице.

Из таблицы видно, что, например, для значений п от 11 до 21 Р(п) 3, а для п от 22 до 43 Р(п) 4 п т.д. Кроме того, константы, определяющие новые значения Р(п), запоминать не надо, так как они формируется путем сдвига исходной константы 1, 011 на один разряд влево после прохождения п порогового значения.

Устройство работает следующим об- разом..

Teкyul й отсчет случайной величины X;, в двоичном коде поступает на разрядные входы уменьшаемого вычи- тателя 2 и входы элемента ИЛИ 1, что обуславливает появление на выходе последнего сигнала. Данный сигнал инициирует начало i-ro цикла работы устройства.При этом обеспечивается

5

О

5

0

5

0

п

,

152

передача содержимого сдвигового регистра 14 блока 13 вычисления коэффициентов усреднения в сдвиговый регистр 15. Кроме того, в вычитателе 2, на разрядные входы вычитаемого которого подается содержимое накапливающего сумматора 4, вычисляется разТюсть (х ;- А;,). На разрядных выходах вычитателя 2 устанавливается модуль данной разности,т.е. uN | х; -А;.,, а на выходе знакового разряда устанавливается единичный сигнал, если Ai,iX;, и нулевой, когда А;, х; . Кроме того, сигнал с выхода элемента ИЛИ 1 через элемент 5 задержки (время задержки ол которого выбирается из условия максимального времени работы вычитателя -2, т.е. сТ, С поступает на вход разрешения записи регистра 3, что обеспечивает передачу содержимого сумматора 2 в регистр 3, а также на вход установки в единицу триггера 12 и вход счетчика 11. Триггер Ч 2 устанавливается в единичное состояние, а к содержимому счетчика 11 числа замеров добавляется единица. Сигнал с выхода триггера 12 открывает зле- Meirr И 8, через который на вход управления сдвигом регистра 15, и через элемент 6 задержки на вход управления сдвигом регистра 3, начинают поступать импульсы с генератора 7 тактовых сигналов. Каждый импульс обеспечивает сдвиг содержимого регистра 15 вправо на один разряд, а затем проходя через элемент 6 задержки, сдвиг содержимого регистра 3 вправо также на один разряд, что соответствует операции деления на коэффициент, равный 2 , где i - номер тактового импульса. В момент, когда на выходе регистра 15 формируется импульс, содержимое регистра 3 подается на подсуммирование в накапливающий сумматор 4 с соответствующим знаком, где формируется результат вычисления математического ожидания в виде (2). Кроме того, импульс с выхода регистра 15 устанавливает триггер 12 в нулевое состояние. На этом цикл обработки i-ro отсчета Xj заканчивается. Когда номер текущего отсчета достигает порогового значения Р(п), который хранится в регистре 9 памяти, то на выходе элемента 10 сравнения формируется импульс, который обеспечивает сдвиг содержимого регистра 9

313

влево на один разряд, т.е. устанавливается новое пороговое значение Р(п) в соответствии с таблицей. Кроме того, содержимое регистра 14 также сдвигается на один разряд влево. Первоначально (перед началом работы ycTpofiCTBa) в регистр 14 сдвига записывается единица в младший разряд. После j-ro порогового значения Р(п) данная единица окажется сдви- нутой на j разрядов влево, что опре-- деляет коэффициент деления содержимого регистра 3.

Формула изобретения

Устройство для вычисления математического ожидания, содержащее 1и,1чи- татель, накапливающий сумматор, счетчик, блок вычисления коэффициентов

усреднения, сдвиговый регистр памяти элемент сравнения, генератор тактовых импульсов, причем разрядные входы уменьшаемого вычитателя являются информационным входом ycTpoficTBa, разрядные входы вычитаемого вычитателя соединены с соответствующими разрядными выходами накапливающего сумматора, выход которого является выходом устройства, о т л и ч а- ю щ е е с я тем, что, с целью упрощения, Б него введены элемент Н, триггер, элемент ИДИ, сдвиг овый регистр, два элемента задержки, блок вычисления коэффициентов усреднения содержит регистр и сдвиговый регистр причем в блоке вычисления коэффипи- ентов усреднения вход регистра соединен с выходом элемента сравнения, разрядные выходы регистра соединены с соответствующими разрядными информационными входами сдвигового ре

1,011 10,110 101, 10 1011,00 10110,00

, о

5

0

5 0 j 0

154

гистра, вход управления сдвигом, вход разрешения записи и В1)1ход которого соединены с выходом элемента И, выходом элемента НИИ и входТ,ом разре- щения записи накап.аивающег о сумматора соответственно, разрядные выходы, выход знакового разряда и вход разрешения записи вычитателя соединен со 1

ответственно с соответствующими информационными входами сдвигового регистра, входом накапливающего сумматора и выходом элемента ИТШ, каждый вход которого соединен с соответствующим разрядным входом уменьшаемого вычитателя, выход элемента ИЛИ через первый элемент задержки соединен с входом счетчика, входом установки в единицу триггера и входом разрешения загшсн сдвигового регистра, разрядные выходы и вход управления сдвигом которого соединены соответственно с соответствующими разрядными входами группы накапли- пающего сумматора и выходом, второго элемента залтержки, вход которого соединен с выходом элемента И, первый и второй входы которого соединены соответственно с в|11ходом генератора тактовых импульсов и выходом триггера, вход установки в ноль которого соединен с входом разрешения записи накапливающего сумматора, разрядные выходы счетчика соединены с соответствующими входами первой группы элемента сравнения, входы второй группы которого соединены с разрядными выходами сдвигового регистра памяти, вход управления сдвигом которого соединен с выходом элемента сравнения, а информационный вход является входом задания порогового значения коэффициента деления устройства.

1,375

2,73

5,5

11

22

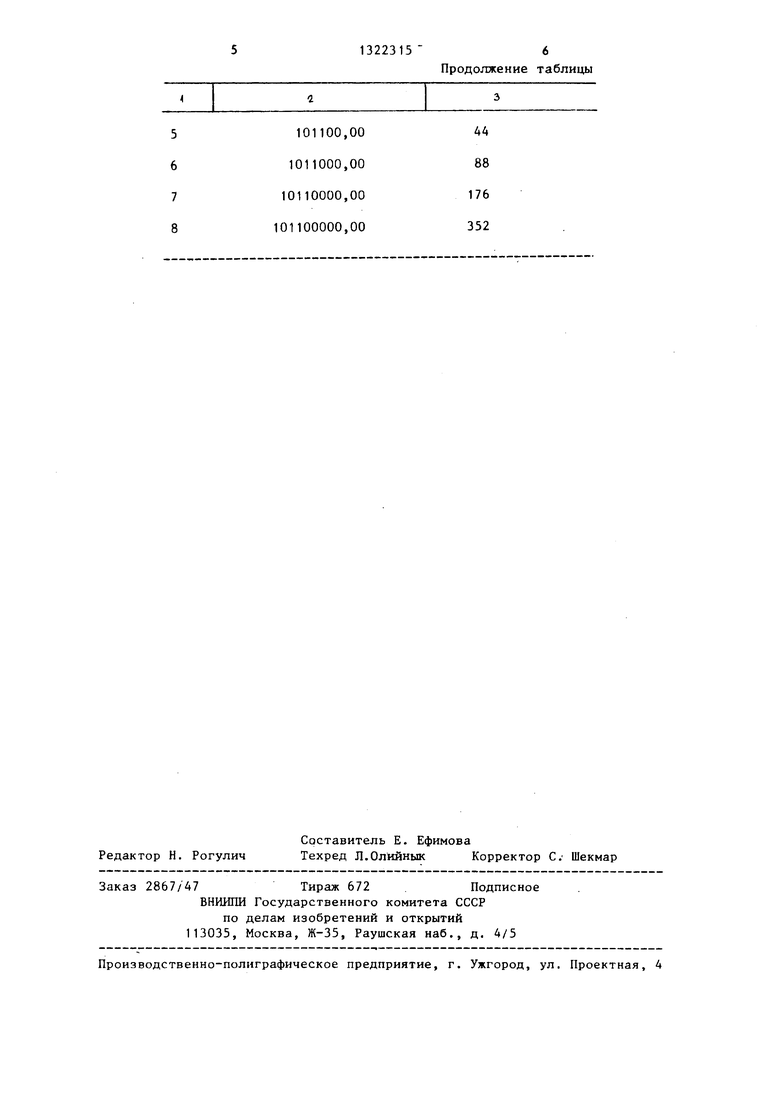

101100,00

1011000,00

10110000,00

101100000,00

Редактор Н, Рогулич

Составитель Е. Ефимова

Техред Л.Олийнык Корректор С. Шекмар

Заказ 2867/47Тираж 672 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Продолжение таблицы

44

88

176

352

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для определения среднего арифметического значения | 1986 |

|

SU1310840A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

Изобретение относится к вычислительной технике и может быть использовано для аппаратурного анализа случайных процессов и статистической обработке массивов данных. Целью изобретения является упрощение устройства. Работа устройства основывается на использовании адаптивного знакового алгоритма усреднения, причем умножение на массовой коэффициент реализуется путем сдвига информации в регистре. Устройство содержит элемент ИЛИ 1, вычитатель 2, сдвиговые регистры 3, 9, 14, 15, накапливающий сумматор 4, элемент 5, 6 задержки, генератор 7 тактовых импульсов, элемент 10 сравнения, счетчик 11, триггер 12, блок 13 вычисления массовых коэффициентов. 1 ил. (Л

| Многопороговый логический элемент четности | 1976 |

|

SU608266A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивное устройство для вычисления среднего | 1978 |

|

SU769551A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-14—Подача