Stfjffff

ел

ит генератор 1 тактовых импульсов, элементы И 2,3, 21 и 22, генератор 4 М-последовательности, пороговый обна ружитель 5 сигналов, перемножитель 6, блок 7 предварительного корреляцион нрго анализа, состоящий из Р согласованных фильтров (СФ)8, Р пороговых блоков 9 и формирователя 10 импульсов , дешифратор 1 1, блок 12 ввода кодовых векторов, блок 13 управления, формирователи 14 и 15 импульсов,элемент ИЛИ 16, блок 17 запрета, блок 18 задержки, Rs-триггеры 19 и 20, счет чики 2 и 24, блок 25 интеграторов и решающий блок. Последовательность из

О и 1 с выхода порогового обнару - Жителя 5 подвергается корреляционной обработке в СФ 8. Каждый СФ 8 согласован с определенным сегментом из

М-последовательности, которым осуществляется манипуляция принимаемого сигнала. Величина отклика каждого СФ 8 сравнивается с соотв.порогом. По результатам сравнения дешифратор принимает решение о величине времен ной задержки относительно установлен - ного начала принимаемой М-последовательности, По зтому значению блок 12 формирует вектор, в соответствии с которым генератор 4 начршает формировать М-последовательность с заданной фазой. Сформированная М-последовательность перемножается в перемножителе 6 с принимаемой последовательностью. Результат перемножения обрабатывается для выявления ошибок и определения момента установления хронизации. 2 з,п, ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Адаптивное устройство компенсации эхосигнала | 1988 |

|

SU1577076A1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОТКЛОНЕНИЙ ПАРАМЕТРОВ ПРИ ДОПУСКОВОМ КОНТРОЛЕ | 2016 |

|

RU2617982C1 |

| Устройство для выделения маркера кадровой синхронизации | 1987 |

|

SU1518903A2 |

| Устройство для допускового контроля амплитудно-частотной характеристики четырехполюсников | 1989 |

|

SU1608591A1 |

| ОБНАРУЖИТЕЛЬ ПАУЗ РЕЧИ В СИСТЕМЕ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2103826C1 |

| Устройство синхронизации приемника многочастотных сигналов | 1984 |

|

SU1185627A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2016 |

|

RU2641096C2 |

Изобретение относится к радиотехнике и связи и позволяет уменьшит время вхождения в синхронизм при ра- боте по каналам связи с большой вероятностью ошибок. Устр-во содер

1

Изобретение относится к радиотехнике и связи и может быть использовано в приемниках широкополосных сигналов .

Цель изобретения - уменьшение времени вхождения в синхронизм при рабо Tie по каналам связи с большой вероят- н;остью ошибок,

I На фиг, представлена структурная электрическая схема устройства синх- р|онизации М-последовательности по за-держке; на фиг,2 - структурная злект- рйческая схема дешифратора; на фиг.3- структурная электрическая схема блока управления,

Устройство синхронизации М-последовательности по задержке содержит генератор тактовых импульсов, пер- вьй 2 и второй 3 элементы И, генератор 4 М-последовательности, пороговый обнаружитель 5 сигналов, перемножитель 6, блок 7 предварительного кор реляционного анализа, состоящий из Р согласованных фильтров 8, Р пороговых блоков 9 и формирователя 10 импульсов. Дешифратор П, блок 12 ввода кодовых векторов, блок J3 управления, первый 14 и второй 15 формирова тели импульсов, элемент ИЛИ 16, блок 17 запрета, блок 18 задержки, первый 19 и второй 20 RS-триггеры,

третий 21 и четвертый 22 элементы И, первый 23 и второй 24 счетчики, блок 25 интеграторов и решающий блок 26,

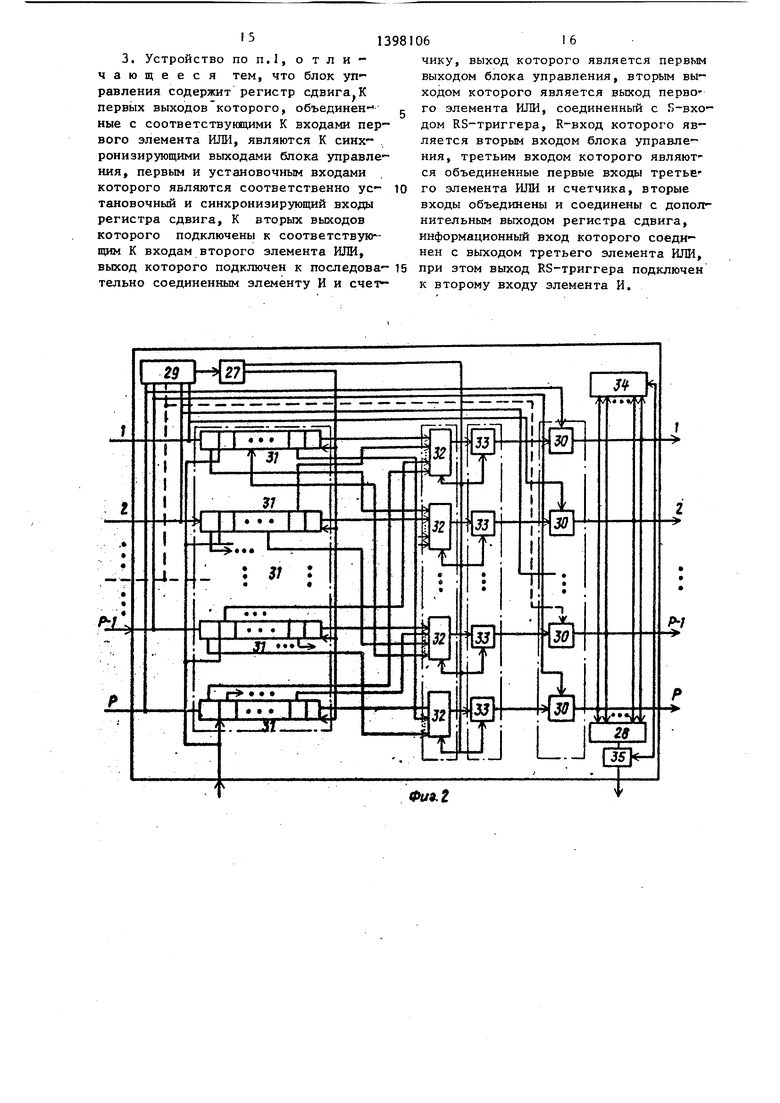

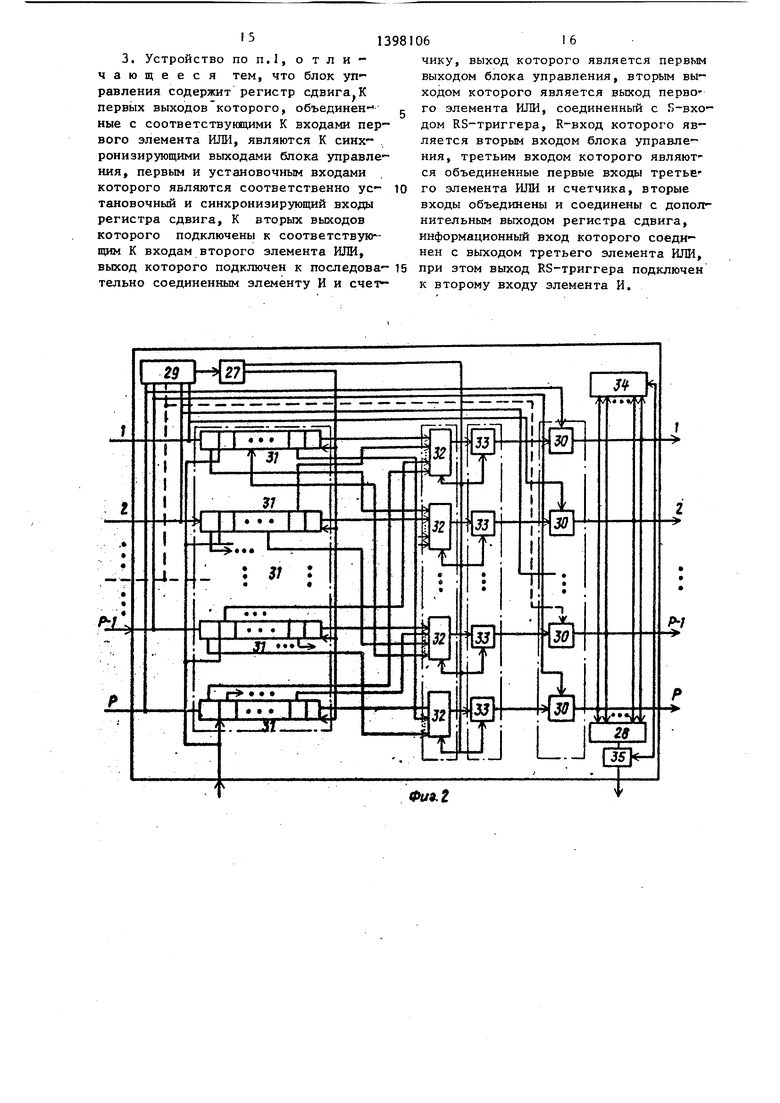

Дешифратор 11 содержит формирователь 27 импульсов, первый 28 и второй 29 элементы ИЛИ, Р элементов И, Р регистров 3 сдвига, Р сумматора32,

Р решающих блоков 33, анализатор 34 состояний выходов и блок 35 запрета.

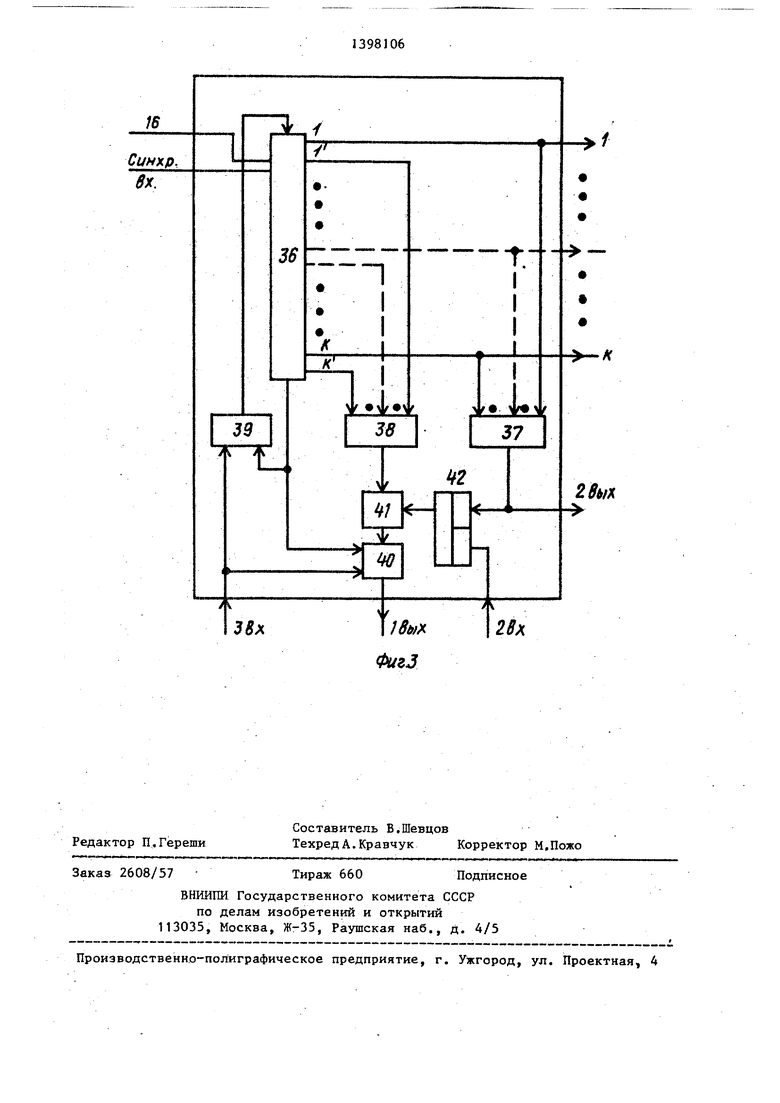

Блок 13 управления содержит регистр 36 сдвига, первый 37,второй 38 и третий 39 элементы ИЛИ, счетчик 40,

элемент И 41 и RS-триггер 42,

Устройство синхронизации М-после- довательностей по задержке работает следующим образом,

В устройстве до поступления сигнала на его вход находятся в исходном состоянии генератор 4, блок 7, дешифратор 11 дешифрации, блок 13 , блок 25 интегратора, в состояние логического нуля установлены первый 9

и второй 20 RS-триггеры, обнулены первый .23 и второй 24 счетчики, с выхода генератора 1 следуе т последовательность тактовых импульсов, частота следования которых соответствует так- товой частоте М-последовательности, которой манипулирован принимаемый из канала связи сигнал.

31

Сигнал из канала связи поступает на второй вход порогового обнаружителя 5, являющийся входом устройства а на первый вход обнаружителя 5с выхода генератора 1 поступают такто вые импульсы, осуществляющие строби- рование порогового обнаружителя 5, Пороговый обнаружитель 5 производит обработку принимаемого сигнала на радиочастоте, в результате которой на его выходе выдается последовательность видеоимпульсов, состоящая из логических нулей и единиц.

Эта последовательность видеоим- пульсов поступает на информационный вход блока 7 и на первый вход перемножителя 6, на втором входе которого сигнал отсутствует до того момента, пока генератор 4 находится в исход- ном состоянии.

С выхода порогового обнаружителя 5 последовательность видеоимпульсов с поступлением каждого тактового импульса поразрядно поступает на инфор- мационные входы Р согласованных фильтров 8, в которых осуществляется корреляционная обработка видеопоследовательности. Каждый из соглаг сованных фильтров 8 согласован с оп- ределенным сегментом из М-последовательности, которым осуществляется манипуляция принимаемого сигнала.

Выбор сегментов на последовательности должен осуществляться с учетом того, чтобы величина нормированной функции взаимной корреляции между сегментами, а также величина боковых выбросов на автокорреляционной функ - ции этих сегментов не превосходили некоторого допустимого уровня. Необходимо учитывать также при выборе длины сегментов требуемое значение вероятности ложного обнаружения сегг мента каждым согласованным фильтром 8

С поступлением каждого тактового импульса с выхода генератора J по. фронту тактового импульса происходит выдача значения принятого разряда с выхода порогового обнаружителя 5, при этом по срезу этого же тактового импульса происходит запись значения принятого разряда в каждый согласованный фильтр 8, при этом по срезу тактового импульса формирова-

тель 10 формирует импульс, по-

дачей которого на вторые входы пороговых блоков 9 осуществляется сравнение величины отклика согласованног

6

фильтра 8 с величиной установленного порога в соответствующем пороговом блоке 9. Если величина отклика согласованного фильтра В меньше величины порога соответствующего порогового блока 9, то в этом случае на выходе данного порогового блока 9 присутствует сигнал логического нуля и сигнал, соответствующий логической единице, в противном случае.

Сигналы, соответствущие уровням логического нуля и единицы, с выходов блока 7 воздействуют на входы дешифратора 11, при этом если хотя бы на одном из выходов блока 7 присутствует сигнал логической единицы, то в этом случае осуществляется запись значений этих сигналов с выходов блока 7 в дешифратор J J.

По поступаюш ад на входы дешифратора J1 сигналам в этом блоке осуществляется анализ этих CHi-HanoB, по- рядок поступления которых отображает результаты обнаружения сегментов согласованными фильтрами 8 и принятие решения по этим обнаружениям соответствующими пороговыми блоками 9. На основании анализа комбинаций сигналов в дешифраторе 11 принимается решение о значении временной задержки относительно установленного начала принимаемой М-последовательности. За установленное условное начало М-последовательности можно по усмотрению принять любой разряд М-последовательности .

Результат принятия решения дешифратором I1 представляется в виде параллельной Р-разрядной комбинации символов логических нулей и одной логической единицы на его выходах и на управляющем выходе дешифратора 11.

Когда значение сигнала логической единицы присутствует больше чем на одном из выходов дешифратора 11, а на его управляющем выходе присутствует сигнал логического нуля, решение о задержке принимаемого сигнала счи- . тается неопределенным и продолжается анализ поступающих сигналов с выхода блока 7,

Если решение дешифратора 11 определено, то возможно Р-различий между собой положений сигнала логической единицы на его выходах, которые отображают значение определенной фазы принимаемого сигнала. Эта Р-разряд- ная комбинация,состоящая из одной логической единицы и логических нулей, : воздействует на входы блока 12,который Преобразует Р-разрядную комбинацию На входах в N-разрядный кодовьй век- top, состоящий из логических нулей И единиц.

1 Таким образом, кодовый вектор на JlJ, выходах блока 12 представляет со- Йой состояние регистра сдв:Ига в ене раторе 4, когда фаза генерируемой М-последовательности соответствует определенной в дешифраторе 11 со сдвгом вперед на один тактовый интер- ал, который необходим для времени Йнализа в устройстве принятого сиг Мала..

Одновременно при принятии решения дешифратором 11 о фазе принимаемого Ьигнала на его управляющем выходе присутствует сигнал, соответствующий уровню логической единицы, который Поступает на вход блока J8 и через рлок 17 воздействует на вход первого рмирователя J4, а также через зле- ИЛИ 16 воздействует на установочные входы генератора 4 и блока 25 устанавл шая их в исходаое состояние и на первый вход блока J3, устанавливая его в исходное состояние.

Через интервал времени, равный времени задержки сигнала в блоке J8, На его выходе появляется сигнал, соответствующий уровню логической единицы. Этим сигналом первьй RS-триг- rjep 19 переводится в состояние ло- г ической едини1 ы, тем самым подает

с1я сигнал логической единицы на вто- р;ой вход третьего элемента И 21 и на- .в|торой запрещающий вход блока 17, чём запрещается прохождение сигнала логической единида через блок 17. :11ри этом на выходе первого формирователя 14 формируется импульс, который воздействует на вход генератора 4 и на третий вход блока 13, тем самым разрешая запись кодового вектора с выхода блока 12 в генератор 4 и запускает блок J3.

С поступлением очередного тактово- то импульса на синхронизирующий вход .генератора 4 с его выхода осуществляется вьщача М-последовательности с заданной фазой, определяемой введенным в генератор 4 кодовым вектором с выходов блока 12. Эта лоследователь- ность поступает на второй вход пёрег- множителя 6,

С начала запуска с К выходов блока 13 последовательности во времени выдаются одиночные импульсы интервал времени меядау которыми определяет .. временной сдвиг между интервалами ин тегрирования интеграторов блока 25, а интервал -времени между двумя следующими друг за другом импульсами с одного и того же выхода блока 13 определяет интервал интегрирования интегратора, которьй подключен к этому его выходу.

Работа блока 13 проходит циклами,

каждый цикл начинается вьщачей сигнала логической единицы в виде одиночного импульса с первого синхронизирующего выхода блока 13, а заканчивает- ся цикл выдачей импульса с его К-го

синхронизирующего вькода.

Величина сдвига между временными интервалами интегрирования устанавливается, исходя из учета длины пачек ошибок, которые встречаются в прини- маемой: М-последовательности, т.е. наиболее вероятной длины панки ошибок.

Каждый ийтегратор блока 25 произ- водит интегрирование сигналов, посту- 30 пающих на его вход с выхода перемножителя 6 за период времени между подачей синхронизирующих импульсов из блока 13.

35

Сигналы в виде одиночных импульсов, амплитуда которых зависит от результата интегрирования интегратором .блока 25, поступает на второй вход решающего блока 26, на первьй вход

40 которого поступают тактовые импульсы от генератора 1, при этом в решающем блоке 26 происходит сравнение ампли- .туды импульса, поступившего на второй вход, с величиной поррга ycj.ar:

45 новленного в нем. При превьш1ении амп.- литудой импульса на втором входе ре- шающего блока 26 величины установленного в нем порога на его выходе формируется одиночный импульс, соответ50 ствующий уровню логической единицы, который поступает через четвертый элемент И 22 на первый счетный вход второго :счетчика 24, при этом в нем происходит запись единицы. Если

55 амплитуда импульса на втором входе решающего блока 26 меньше значения порога, на его выходе присутствует сигнал, соответствующий уровню ло гического нуля.

Для уменьшения влияния пачек ошибок на успешное установление синхронизации, используется второй счетчик 24 импульсов. При этом, устанавливая коэффициент его счета больше единицы, добиваются уменьшения вероятности ложного установления синхронизации при случайном превьппении импульсами с выходов блока 25 порога в решающем блоке 26 при воздействии структурных помех, близких по структуре М-последовательности, которая применяется устройством, т.е. генерируется генератором 4. При работе . по каналам связи, в которых вероятность таких структурных помех мала, коэффициент счета во втором счетчике 24 устанавливается равным единице, при этом для принятия решения на втором этапе проверки достаточно, чтобы импульс с выхода хотя бы одного интегратора блока превысил порог в решающем блоке 26 в течение установленного интервала времени накопления. „

Если в течение интервала времени накопления число импульсов, поступивших на второй вход четвертого элемента И 22, а через него на первый вход второго счетчика 24 импульсов, превысит установленный коэффициент счета, то второй RS-триггер. 20 за счет подачи на его S-вход сигнала логической единицы с выхода второго счеТ чика 24,переходит в состояние логической единиць. При этом с прямого выхода второго RS-тирггера 20 сигнал логической единицы подается на второй вход второго элемента И 3, с первого входа на выход которого, являющийся выходом устройства, начинает поступать последовательность с выхода генератора 4, что означает факт установления синхронизации по ;задержке принимаемой М-последовательности, С инверсного выхода второго триггера 20 снимается сигнал логической единицы, который присутствовал «а втором входе первого элемента И 2 ,и на входе второго формирователя J5,: при этом запрещается прохождение ;товых импульсов На второй вход блог ка 7, Кроме того, при снятии сигнала логической единицы с входа формирова- теля 15 на его выходе формируется одиночньй импульс, который поступает; на первый вход блока 7 и на вход шифратора 11, устанавливая эти блоки :В исходное состояние. При этом сиг- ;

10

15

20

981068

нал с выхода порогового обнарух-ите- ля 5 в блоке 7 не обрабатывается, а поступает дая обработки на первый вход перемножителя 6.

Если число импульсов на первом входе второго счетчика 24 за установленный интервал накопления не достигает установленного в этом счетчике коэффициента счета, с первого выхода блока 3 в конце интервала накопления поступает одиночный ин- пульс сброса на второй вход установки в нулевое состояние второго счетчика 2k к на R-вход второго КЗ-триггера 20, подтверждая его состояние логического нуля, и через второй вход элемента ИЛИ 16 импульс сброса поступает на установочный вход генератора 4, переводя его в исходное состояние, на вход блока 25 интеграторов, сбрасьшая интеграторы, на первый вход блока 13, переводя его в исходное состояние. При этом интервал вре25 мени накопления устанавливается работой блока 13, Кроме того, с началом работы блока 13 с его второго выхода вьщаются одиночные импульсы че- рез третий элемент И 21 на вход первого счетчика 23, который осуществляет счет числа поступивших на его вход импульсов. Коэффициент счета перво- ; го счетчика 23 установлен равным 2К-1, где К - число интеграторов блока 25. С поступлением 2К-1-го импульса с второго выхода блока 13 на вход первого счетчика 23 с его выхода поступает одиночный импульс, со - ответствукщий уровню логической еди40 ницы, на R-вход первого RS-тригге- ра 19, тем самым переводя его в состояние логического нуля, при этом снимается уровень логической единицы с второго запрещающего входа блог

45 ка 17 и с второго входа третьего элемента И 21.

Если синхронизация установлена, в силу того, что блок 7 и дешифратор 11 находятся в исходном состоя30

35

50 НИИ, с управляющего выхода дешифрато- ;ра JJ сигналы отсутствуют. Если же в течение интервала времени накопления факт установления синхронизации не установлен, т.е. с первого выхода

gg блока J3 в конце интервала накопления выдается, импульс сброса, то при переходе первого RS-триггера J9 в состояние логического нуля в устройстве происходит возврат к этапу опр ё9 . деления задержки принимаемой М-после- довательности при помощи дешифратора 11. При принятии дешифратором 11 о задержке принимаемой последовательности, т.е. выдачи сигналов логической единицы с управляющего вькода, работа устройства осущест25 с

Дешифратор 11 работает следующим образом.

В исходном состоянии регистры 31 обнулены,. -Пусть на вход ,Р ;п1оступает единичный импульс, соответ - ствующий уровню логической единицы, который воздействует на вход первого разряда 1-го регистра 31 и через 1:-вход второго элемента ИЛИ 29 воздействует на вход формирователя 27. |При этом с выхода формирователя 27 в;ыдается одиночный импульс, кото- воздействует на тактовые входы р егистров 31, и по срезу этого им- ;п:ульса происходит запись значения на в ходах регистров 31, при этом в пер-. разряд i-ro регистра 3J, на вхо- д которого присутствует сигнал логи- ч|еской единицы, будет записана едини - ца, а в первые разряды остальных ре

гистров 31 - сигнал логического нуля : При последующих поступлениях сигналов логической единицы на входы дешифратора Л в первые.. разряды регистров 31 записьгоаются новые значения сигналов, а ранее записанные зна- чения сигналов в разрядах регист- ploB 31 сдвигаются каждай раз на один разряд в сторону старших разрядов регистров 3, при этом по срезу импульса на втором выходе формировате- ля 27 импульсов и на его первом выходе также формируется одиночньй им- лульс, который воздействует на установочные входы сумматоров 32 и управ

ляющие входы решающих блоков 33, сум- 45 логической единицы на его перматорами 32 производится суммирова- йие значений состояния разрядов регистров 31 сдвига, к которым подключены входы каждого сумматора 32, и результаты суммирования с выхода соответствующего сумматора 32 поступают на первый вход подключенного к нему решающего блока 33, в котором осуществляется сравнение результата суммирования сумматора 32 с величиной | порога, установленного в данном ющем блоке 33.

i При превышении напряжением на вы-; ходе некоторого сумматора 32. величи50

55

вый вход, равен 2K-S, где S - коэффи циент счета второго счетчика 24. Установка коэффициента счета счетчика 40 подачей сигнала логической еди ницы на его первьй вход определяет величину интервала накопления на эта пе проверки правильности определения задержки сигнала дешифратором 11.

С поступлением очередного тактово го импульса на синхронизирующий вход регистра 36 сигнал логической едини- . цы сдвигается из первого, разряда ре гистра во второй и далее, с поступле нием последующих тактовых импульсов

10

5

0

0

с

ны порога в соответствующем решающем блоке 33 на его выходе формируется сигнал логической единицы, который поступает на второй вход соответствующего элемента И 30, при этом если на первом входе i-ro элемента 30 И присутствует сигнал логической единицы, который подается с соответствующего входа дешифратора 11, то сигнал с выхода данного элемента И 30 поступает на соответствующий вход дешифратора 11 и через первый элемент ИЛИ 28 и через блок 35 на управляющий выход дешифратора 11. Если из-за ложного обнаружения одновременно несколькими согласованными фильтрами В сегментом М-последовательности происходит выдача сигналов на выходах более чем одного элемента И 30, то на выходе анализатора 34 присутствует сигнал логической единицы, кото- рьий, поступая на второй э апрещающий вход блока 35, запрещает прохождение 5 сигнала логической единицы на управляющий выход дешифратора 11.

Блок 13 работает следующим образом.

В исходном состоянии регистр 36 находится в обнуленном состоянии. При поступлении на третий вход блока .13 одиночного импульса в первьй разряд сдвига осуществляется запись логической единицы, при этом также уста-; навливается коэффициент счета в счет чике 40 с переменным коэффициентом счета.;

Подача сигнала логической единицы, поступившей на третий вход блока 13, происходит по цепи: первый счетчик 40, первьй вход третьего элемента ИЛИ 39, вход регистра 36.

Коэффициент счета счетчика 40, который устанавливается при подаче сиг-

0

логической единицы на его пер

вый вход, равен 2K-S, где S - коэффициент счета второго счетчика 24. Установка коэффициента счета счетчика 40 подачей сигнала логической единицы на его первьй вход определяет величину интервала накопления на этаг пе проверки правильности определения задержки сигнала дешифратором 11.

С поступлением очередного тактового импульса на синхронизирующий вход регистра 36 сигнал логической едини- цы сдвигается из первого, разряда ре гистра во второй и далее, с поступле - нием последующих тактовых импульсов

тором J J. Если на втором этапе проверки принято решение о правильном определении задержки, то в дальнейшем, чтобы ускорить реакцию уетройст- ва на рассинхронизацию и необходимость возобновить поиск, интервал времени накопления уменьшается за счет изменения коэффициента счета счетчика 40.

Установка блока J3 в исходное состояние происходит в момент, когда на его установочный вход подается единичный импульс, а установка счет- 15 чика 40 в обнуленное состояние осуще - ствляется в момент подачи единичного импульса на его первый либо второй входы, т.е. одновременно, с установкой необходимого коэффициента счета

10

каждый раз производится сдвиг логической единицы на один разряд по регистру 36, при этом последовательно проходя по разрядам регистра 36, на выходы которых с его входов последовательно во времени выдаются одиночные импульсы, соответствугацие уровню логической единицы, временной интервал между выдачей импульсов равен двум тактовым интервалам генератора 1

При подаче импульса с выхода регистра Зб сигнал логической единицы поступает на соответствующий выход блока 13, а также через первый элемент ИЛИ 37 на второй выход блока 13 ;И на S-вход RS-триггера 42, тем мым устанавливая его в состояние ло- тической единицы. Если в следующий

тактовый интервал на второй вход бла 20 счетчиком 40, ка 13 поступает импульс, соответствующий уровню логической единицы, с выхода решающего блока 26, то RS- :триггер 42 по своему R-входу устанавливается в состояние логического ну- 25 ля. Через два тактовых интервала выдаются импульсы логической единицы с вторых выходов регистра 36, которые через второй элемент ИЛИ 38 поступают на первый вход элемента И 41 и в зависимости от сигнала на его вто- .ром входе либо поступают на третий счетный вход счетчика 40, когда на втором входе элемента И 41 присутствует сигнал логической единицы, либо нет, когда на втором входе элемента И 4J присутствует сигнал логического Нуля,

После подачи единичного импульса установки на первый вход счетчика 40 40 тельного корреляционного анализа,де- и установки в нем коэффициента счета шифратор, блок ввода кодовых векто- равного 2К, при подаче на его второй ров, блок управления, первый и второй )вход единичного импульса в, конце формирователи импульсов, элемент ИЛИ , цикла продвижения единицы по регист- блок задержки, блок запрета, последо- ру 36 с дополнительного выхода регйС Р-45 вательно соединенные третий элеменуИ ра 36 счетчик 40 ,на первый по счету первый счетчик и первый RS-триггер, импульс на его втором входе своего последовательно соедине ные решающий состояния не изменяет, k при после- блок, четвертый элемент И, второй УЮШИХ импульсах, поступающих на йто счетчик и второй RS-триггёр , а так- рой вход счетчика 4.0, в счетчике про 50 ж блок интегр;аторов, выход которого Исходит установка его в,нулевое сое- подключен к первому входу решающего Тояние, при этом коэффициент сче.та блока, второй вход которого обьединен устанавливается равным К, где 1К - с синхронизирукнцим входом блока уп- число выходов блока J3, Таким обра- равления и подключен к выходу генера- зом, при запуске блока 13 коэффиисиент 55 тора тактовых импульсов, выход порого- счета счетчика 40 устанавливается 2К вого обнаружителя сигналов подключен чтобы обеспечить на этапе проверки. к первому входу перемножителя и ин Ьравнпьностй принятие решения по за- формационному входу блока предвари- держке принимаемого сигнала дешифра- тельного корреляционного анализа,

Формула и-3 обретения

: 1. Устройство синхронизации М-по- следовательности -по задержке, содержащее генератор тактовых импульсов, первый и второй элементы И, генератор М-последовательности и пороговый обнаружитель сигналов,синхронизирую30 щий вход которого объединен с первым входом первого элемента И, с синхро- низирующш входом генератора М-после1 довательности и подключен к выходу генератора Непоследовательности,

35 отличающееся тем, iTo, с целью уменьшения времени вхождения в синхронизм при работе по канапбм связи с большой вероятностью ошибок, введены перемножитель, блок предвари тором J J. Если на втором этапе проверки принято решение о правильном определении задержки, то в дальнейшем, чтобы ускорить реакцию уетройст- ва на рассинхронизацию и необходимость возобновить поиск, интервал времени накопления уменьшается за счет изменения коэффициента счета счетчика 40.

Установка блока J3 в исходное состояние происходит в момент, когда на его установочный вход подается единичный импульс, а установка счет- чика 40 в обнуленное состояние осуще - ствляется в момент подачи единичного импульса на его первый либо второй входы, т.е. одновременно, с установкой необходимого коэффициента счета

20 счетчиком 40, 25

40 тельного корреляционного анализа,де- шифратор, блок ввода кодовых векто- ров, блок управления, первый и второй формирователи импульсов, элемент ИЛИ блок задержки, блок запрета, последо- 45 вательно соединенные третий элеменуИ первый счетчик и первый RS-триггер, последовательно соедине ные решающий блок, четвертый элемент И, второй счетчик и второй RS-триггёр , а так- 50 ж блок интегр;аторов, выход которого подключен к первому входу решающего блока, второй вход которого обьединен с синхронизирукнцим входом блока уп- равления и подключен к выходу генера- 55 тора тактовых импульсов, выход порого- вого обнаружителя сигналов подключен к первому входу перемножителя и ин формационному входу блока предвари- тельного корреляционного анализа,

Формула и-3 обретения

: 1. Устройство синхронизации М-по- следовательности -по задержке, содержащее генератор тактовых импульсов, первый и второй элементы И, генератор М-последовательности и пороговый обнаружитель сигналов,синхронизирую30 щий вход которого объединен с первым входом первого элемента И, с синхро- низирующш входом генератора М-после1 довательности и подключен к выходу генератора Непоследовательности,

35 отличающееся тем, iTo, с целью уменьшения времени вхождения в синхронизм при работе по канапбм связи с большой вероятностью ошибок, введены перемножитель, блок предвари P выходов которого через дешифратор подключены к соответствующим Р входам блока ввода кодовых йек. оров, N выходов которого подключены к соответствующим N информационным входам генератора М-последовательности, выход которого подключен к первому входу второго элемейта И и второму входу

перемножителя, выход которого подклю- ю вторым входом которого являются объе- чен к информационному входу блока ин- диненные вторые управляющие входы тегратора, К синхронизирующих входов всех Р согласованных фильтров и вход которого соединены с соответствующие- формирователя импульсов, выход кото- ми К синхронизирующими выходами бло- рого соединен с объединенными управ- ка управления, установочный вход бло- 15 ляющими входами Р пороговых блоков, ка интеграторрв объединен с первьм входом блока управления и с установочным входом генератора М-последовательности и соединен с выходом элемента ИЛИ, первой вход которого объе- 20 ты ИЛИ, анализатор состояний выходов, динен с установочными входами второ- формирователь импульсов, блок запре2. Устройство по п.If о тл и- чающееся тем, что,дешифратор содержит первьй и второй элеменго счетчика и второго RS-триггера и подключен к первому выходу блока уп: равления, второй вход которого соеди; нен с выходом решающего блока, второй вход элемента ИЛИ объединен с

входом первого формирователя импульсов и подключен к выходу блока запрета , первьй вход которого через блок задержки объединен с S-входом первого RS-триггера и подключен к управляющему выходу дешифратора, установочный вход которого объединен с первым входом блока предварительного корре- ЛЯ1ЩОННОГО анализа и подключен к вы: ХОДУ второго формирователя импульсов вход которого объединен с вторыми входами первого и четвертого элементов И и подключен к инверсному выкоno модулю/N) соединен с одним из N входов соответствующего i-ro сумматоду второго RS-триггера, прямой выход 40 ра управляющие входы всех Р сумматоров и всех Р рещающих блоков объединены и подключены к первому выходу формирователя импульсов, второй ВЬР- ход которого подключен к объединен- 45 ным синхронизирующим входам всех Р N-разрядных регистров сдвига, объединенные установочные входы которых являются установочным входом дешифратора, управляющим выходом которого

которого соединен с вторым входом :. второго элемента И, выход первого элемента И подключен к второму входу блока предварительного корреляционно - го анализа, а выход первого формирователя импульсов подключен к входу разрешения записи генератора М-последовательности и к третьему входу блока управления, второй выход которого подключен к первому входу третье-до является выход блока запрета, первый

го элемента И, второй вход которого объединен с вторым входом блока запрета и подключен к выходу первого RS-триггера при этом блок предварительного корреляционного анализа содержит формирователь импульсов и Р цепей из последовательно соединенных согласованного фильтра и порогового блока, выходы которых являются Р выи второй входы которого подключены к выходам соответственно второго элемента ИЛИ и анализатора состояний выходов, выход первого элемента ИЛИ 55 соединен с входом формирователя им- ,пульсов, а информационный вход каждого i-ro из Р N-разрядных регистра сдвига объединен с вторым входом соответствующего (i ® Р)-го элемента И;

ходами блока предварительного корреляционного анализа, информационным входом которого являются объединенные информационные входы всех Р согласованных фильтров, объединенные первые управляющие входы которых являются первым входом блока предварительного корреляционного анализа.

вторым входом которого являются объе- диненные вторые управляющие входы всех Р согласованных фильтров и вход формирователя импульсов, выход кото- рого соединен с объединенными управ- ляющими входами Р пороговых блоков, ты ИЛИ, анализатор состояний выходов, формирователь импульсов, блок запре2. Устройство по п.If о тл и- чающееся тем, что,дешифратор содержит первьй и второй элемента, Р N-разрядных регистров сдвига и Р цепей из последовательно соединенных соответствующего сумматора, реша25 ющего блока и элемента И, выходы каждого из которых, подключенные к соответствующим попарно об1 единеннь1М Р входам анализатора состояния дов и второго элемента ИЛИ, являются

30 соответствующими Р выходами дещифра- тора, Р входами которого являются объединенные с соответствующими входами первого элемента ИЛИ информационные входы соответствующих Р N-раз35 рядных регистров сдвига, (+1)-й ВЬР код каждого i-ro из которьк (где j N, i 1,P, (+) - суммирование

. W

no модулю/N) соединен с одним из N входов соответствующего i-ro суммато40 ра управляющие входы всех Р сумматоров и всех Р рещающих блоков объединены и подключены к первому выходу формирователя импульсов, второй ВЬР- ход которого подключен к объединен- 45 ным синхронизирующим входам всех Р N-разрядных регистров сдвига, объединенные установочные входы которых являются установочным входом дешифратора, управляющим выходом которого

и второй входы которого подключены к выходам соответственно второго элемента ИЛИ и анализатора состояний выходов, выход первого элемента ИЛИ 55 соединен с входом формирователя им- ,пульсов, а информационный вход каждого i-ro из Р N-разрядных регистра сдвига объединен с вторым входом соответствующего (i ® Р)-го элемента И;

1

15

чику, выход которого является первым выходом блока управления, вторым выходом которого является выход перво- го элемента ИЛИ, соединенный с К-вхо- дом RS-триггера, R-вход которого является вторым входом блока управления, третьим входом которого являются объединенные первые входы третье го элемента ИЛИ и счетчика, вторые входы объединены и соединены с дополнительным выходом регистра сдвига, информационный вход которого соединен с выходом третьего элемента ИЛИ, при этом выход RS-триггера подключен к второму входу элемента И.

| Устройство синхронизации М-последовательностей | 1982 |

|

SU1125761A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-05-23—Публикация

1986-11-10—Подача