1

Изобретение относится к радиотехнике, может использоваться для цифровой фильтрации бинарных периодических фазоманипулированных (ПФМ) сигналов.

Известен цифровой филыр содержащий последовательно включенные аналого-цифровой преобразователь и сдвигающий регистр, каждый из N выходов которого через одноименный из N весовых блоков соединен с соответствующим из N входов сумматора 1.

Однако известный цифровой фильтр состоит из большого количества блоков. Это связано в основном с большим числом множительных устройств, предназначенных для перемноженил многоразрядных чисел. Число таких множительных устройств равно числу символов на периоде кода и может достигать порядка сотен и более.

Цель изобретения - упрощение устройства путем уменьшения разрядности, весовых блоков.

Для этого в цифровой фильтр, содержащий последовател)НО включенные аналого-цифровой преобразователь и сдвигающий регистр, каждый из N выходов которого через одноименный из N весовых блоков соединен с соответствующим из N входов сумматора, введены последовательно включенные элемент задержки, накапливающий сумматор и -N + 1 .ый весовой блок. При этом первый выход сдвигающего регистра соединен со вторым входом накапливающего сумматора, N-ый выход сдвигающего регистра соединен со входом элемента задержки, а вь1ход; N + 1 - го весового блока соединен с N + 1 -ым входом сумматора.

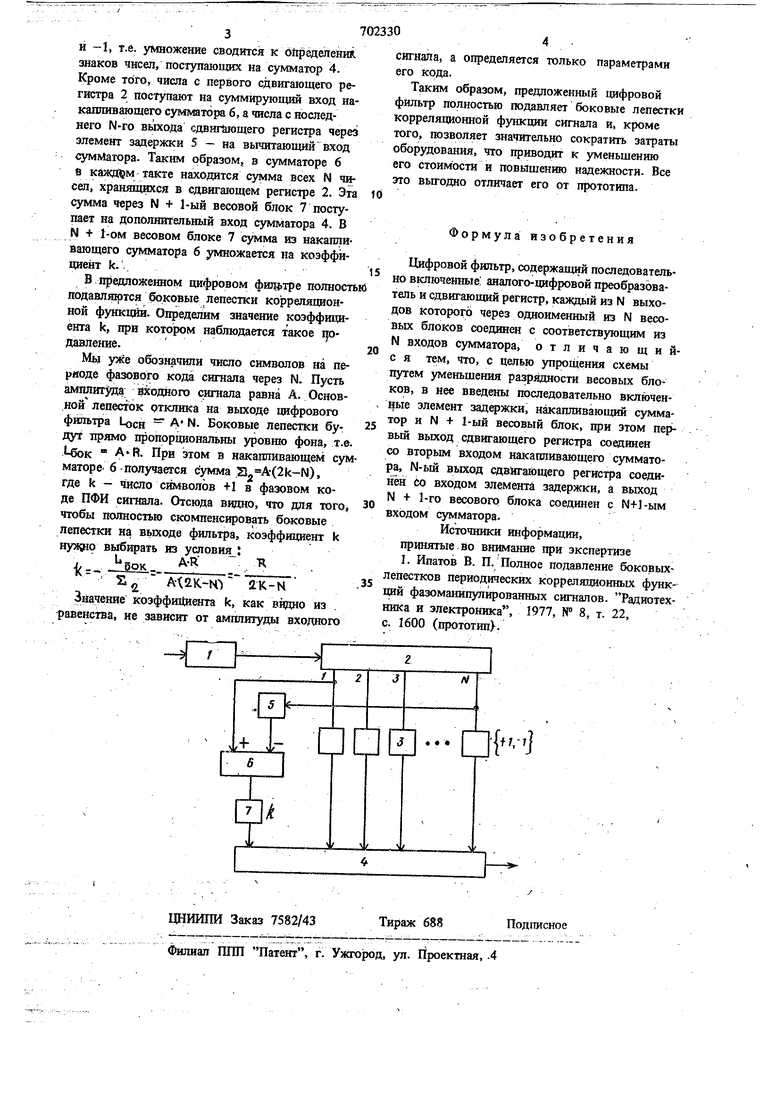

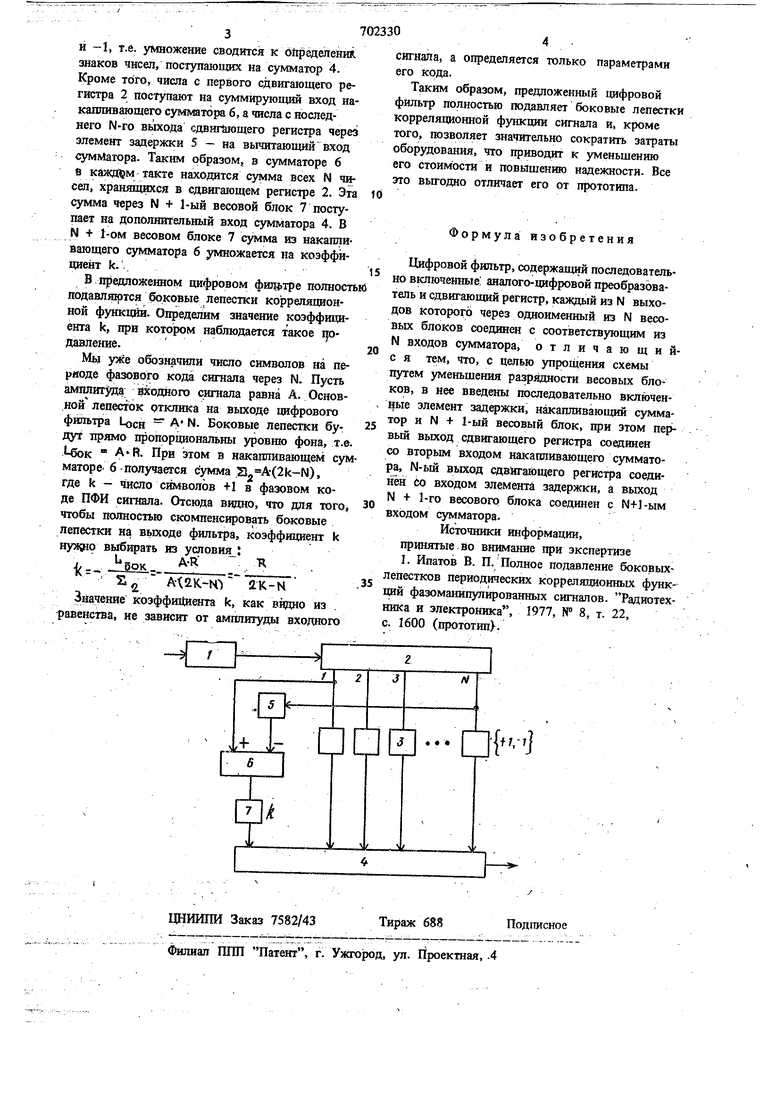

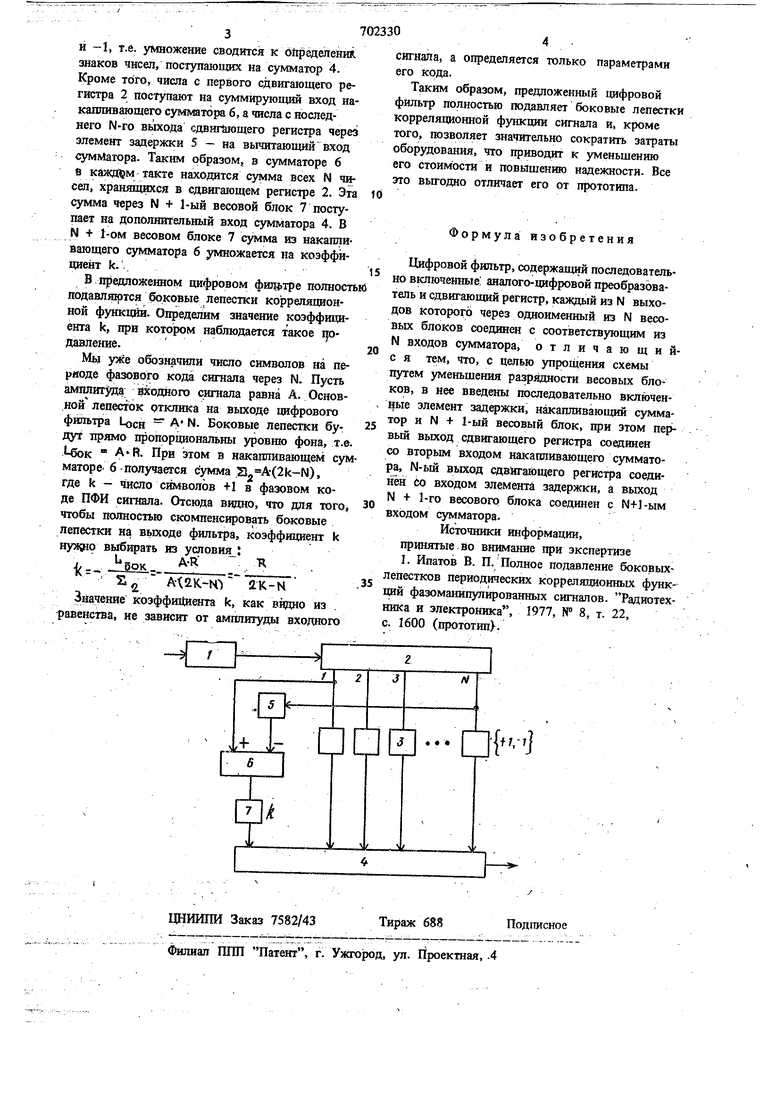

На чертежу приведена структурная электрическая схема предложенного устройства.

Цифровой фильтр содержит аналого-щфровой преобразователь 1, сдвигающий регистр 2, N весовых блоков 3, сумматор 4, элемент задержки 5, накапливающий сумматор 6, N -ь 1 Vbra весовой блок 7.

Устройство работает следующим образом. .

С аналого-цифрового преобразователя 1 N-разрядные числа поступают через сдвигающий регистр 2 и весовые блоки 3 на сумматор 4. В весовых блоках 3 числа умножаются на I и -1, т.е. зМножение сводится к бйределейия. знаков чисел, пост)шающих на сумматор 4. Кроме того, числа с первого сдвигающего регистра 2 поступают на суммирующий вход накапливающего сумматора б, а числа с последнего N-ro выхода сдвигающего регистра через элемент задержки 5 - на вычитающий вход сумматора. Таким образом, в сумматоре 6 S каждом такте находится сумма всех N чисел, хранящихся в сдвигающем регистре 2. Эта сумма через N + 1-ый весовой блок 7 поступает на дополнительный вход сумматора 4. В N + 1-ом весовом блоке 7 сумма из накапливающего сумматора 6 умножается па коэффициент k.. В предложенном цифровом фищ.тре полносты яодавля1ртся боковые лепестки корреляционной функции. Определим значение коэффициента k, при котором наблюдается такое i|oдавление. Mbj yjke обозначили число символов на периоде фазового кода сигнала через N. Пусть ампл«г входного сигнала равна А. Основной лепесток отклика на выходе цифрового фильтра LOCH А N. Боковые лепестки будут прямо пропорциональны зфовшо фона, т.е L6oK А R. При этом в накапливающем сум матореб получается сумма .2,A-(2k-N), где k - число символов +1 в фазовом коде ПФИ сигнала. Отсюда видно, что для того, чтобы полностью скомпенсировать боковые лепестки на вщоде фильтра, коэффищент k выбирать из условия Чок. S А-иК-Ю Значение коэффш(иента k, как видно из . равенства, не зависит от амплитуды входного сигнала, а определяется только параметрами его кода. Таким образом, предложенный цифровой фильтр полностью подавляет боковые лепестки корреляционной функции сигнала и, кроме того, позволяет значительно сократить затраты оборудования, что приводит к уменьшению его стоимости и повыщению надежности. Все это вьп-одно отличает его от прототипа. Формул аизобретения Цифровой фильтр, содержащий последовательно включенные, аналого-цифровой преобразователь и сдвигающий регистр, каждый из N выходов KOTOpoi;6 через одноименный из N весовых блоков соединен с соот ветствующим из N входов сумматора, отличающийс я тем, что, с целью упрощения схемы путем уменьшения разрядности весовых блоков, в нее введены последовательно включенные элемент задержки, накаляивающий сумматор и N + 1-ый весовый блок, при этом первый выход сдвигающего регистра соединен со вторым входом накапливающего сумматора, N-ый выход сдвигающего регистра соединен со входом элемента задержки, а выход N + 1-го весового блока соединен с N+1-ым входом сумматора. Источники информации, принятые во внимание при экспертизе I. Ипатов В. П. Полное подавление боковыхлепестков периодических коррелявдонных функций фазоманипулированных сигналов. Радиотехника и электроника, 1977, № 8, т. 22, с. 1600 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой многоканальный коррелятор периодических фазоманипулированных сигналов | 1978 |

|

SU734716A1 |

| Адаптивный нерекурсивный цифровой фильтр | 1988 |

|

SU1578806A1 |

| НЕКОГЕРЕНТНЫЙ ЦИФРОВОЙ ДЕМОДУЛЯТОР "В ЦЕЛОМ" КОДИРОВАННЫХ СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2014 |

|

RU2556429C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2004 |

|

RU2262190C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| Цифровой спектроанализатор | 1982 |

|

SU1092518A1 |

| Устройство дискретного преобразования Фурье | 2017 |

|

RU2647701C1 |

| Цифровой анализатор | 1981 |

|

SU1057872A1 |

| Способ и устройство обработки ФТ сигнала с дискретной подстройкой фазы в экономичном режиме | 2019 |

|

RU2729042C1 |

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

{.-

«

Авторы

Даты

1979-12-05—Публикация

1978-04-03—Подача