Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Рекурсивный цифровой фильтр | 1989 |

|

SU1658376A1 |

| Цифровой нерекурсивный фильтр | 1988 |

|

SU1566472A1 |

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1352622A1 |

| Цифровой нерекурсивный фильтр | 1987 |

|

SU1483608A1 |

| Цифровой нерекурсивный фильтр нечетного порядка | 1985 |

|

SU1314445A1 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1332519A1 |

| Цифровой нерекурсивный фильтр | 1983 |

|

SU1124430A1 |

| Цифровой нерекурсивный фильтр | 1974 |

|

SU516043A1 |

| Устройство для выполнения дискретных ортогональных преобразований | 1984 |

|

SU1233168A1 |

| Нерекурсивный цифровой фильтр | 1984 |

|

SU1223346A1 |

Изобретение относится к радиотехнике, в частности к цифровой обработке радио-, гидро- и звуколокационных сигналов, и может быть применено для фильтрации в реальном масштабе времени сигналов, представленных в цифровом коде. Цель изобретения - повышение быстродействия. Цель достигается за счет формирования матрицы частичных произведений и последующего ее преобразования совместно с результатами предыдущих вычислений в двухстрочный код на каждом тактовом интервале. Для чего в цифровой нерекурсивный фильтр, содержащий коммутатор 1, регистр 2 сдвига, накапливающий сумматор 3, сумматор 9, блок памяти 4 прирощений коэффициентов и синхрогенератор 10, введен блок элементов И 5, формирующий матрицу частичных произведений, преобразователь 6 кода, обеспечивающий преобразование многострочного кода в двухстрочный, первый и второй блоки 7 и 8 регистров, фиксирующие двухстрочный код результата фильтрации. 7 ил.

О

о ел ел о

ю

Изобретение относится к радиотехнике и может быть использовано для фильтрации Сигналов, представленных цифровыми кодами.

Цель изобретения - повышение быст- родействия.

На фиг. 1 представлена электрическая Структурная схема цифрового нерекурсив- його фильтра; на фиг. 2 - то же, преобразо- ателя кода; на фиг, 3 -тоже, преобразователя кода для частного случая разрядности входных данных и приращений коэффициентов равной Четырем; на фиг. 4 - 6 - диаграммы, поясняющие работу преобразователя кода; на фиг. 7 (а, б, в, г, д., е,ж, з. и) - временные диаграммы, г|юясняющие работу цифрового нерекурсивного фильтра.

Цифровой нерекурсивный фильтр (фиг. 1) содержит коммутатор 1, регистр 2 сдвига, на капливающий сумматор 3, блок 4 памяти г|риращений коэффициентов, блок 5 эле- йентов И, преобразователь 6 кода, первый 0лок 7 регистров, второй блок 8 регистров, Сумматор 9, синхрогенератор 10, выход 10i Коммутации, первый управляющий выход 102, второй управляющий выход Юз, третий установочный выход 104, третий управляющий выход 10s, четвертый управляющий вы- Ход 10б, первый установочный выход 10, управляющий выход 10а и второй ус- Тановочный выход 10э синхрогенератора 10. Преобразователь 6 кода (фиг. 2 и 3) содержит слои 11 сумматоров, блоки 12 сумматоров, трехвходовые одноразрядные сумматоры 13.

Устройство работает следующим обоа- зом.

Выходная дискрета сигнала у(п) на п-м такте оаботы фильтра определяется в соответствии с алгоритмом

y(nh 2 (k)(n-k)(1)

К 0

где а(к) - к-й весовой коэффициент; x(n-k) - (п-к)-я дискрета входного сигнала,

Вычисление у(п) организуется через приращения весовых коэффициентов (приращения коэффициентов), под которыми понимается величина (к+1)-а(к). Это позволяет преобразовать выражение (1) к виду у(п)Дэм-1х п-{М-1} + AaN{x rt-{N-1) {N-1) Aa№-i2x n-(N-1)J + ()

N -1N + - (N-1) ...+ ai V x(n-k)+ a0 У

К 1К

x(n-k). (2)

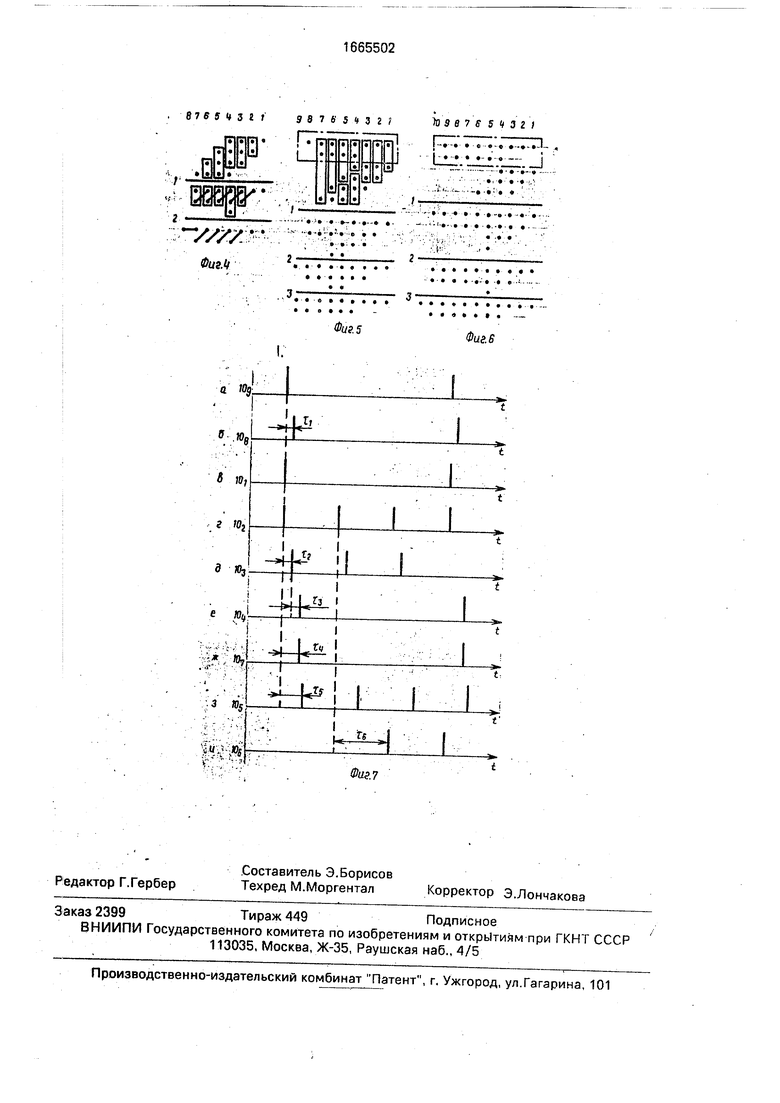

Перед приемом очередной дискреты сигнала предыдущие N дискреты записаны в регистр 2 сдвига. Под действием импульса на втором установочном выходе 10д(фиг. 7,

а) второй блок 8 регистров обнуляется, Спустя время п, равное времени обнуления второго .блока 8 регистров, импульсом на пятом управляющем выходе Юз (фиг. 7, б) разрешается запись во второй блок 8 регистров результата предыдущего цикла фильтрации из первого блока 7 регистров.

Одновременно с обнулением второго блока 8 регистров под действием тактирующего импульса на выходе 10i коммутации (фиг, 7, в) очередная дискрета х(п+1) входного сигнала через коммутатор 1 поступает на регистр 2 сдвига, Эта дискрета записывается в первый элемент памяти регистра 2 сдвига, а предыдущая информация в нем под действием импульса сдвига первого управляющего выхода 102 (фиг. 7, г), совпадающего по времени с импульсом на выходе

101коммутации, передвигается на один элемент памяти вправо. Последнее число при этом теряется, так как первый вход коммутатора 1 при наличии тактирующего импульса на выходе 10i коммутации закрыт.

Это последнее число поступает на вход накапливающего сумматора 3, где складывается с его содержимым и под действием импульса с второго управляющего выхода Юз (фиг, 7, д), задержанного относительно импульса с первого управляющего выхода

102на время Т2, равное времени срабатывания комбинационной части накапливающего сумматора 3, запишется в его память,

Под действием импульса с третьего установочного выхода 10 (фиг. 7, а) задержанного относительно импульса с выхода 10i коммутации на время Г4 -ti +тз, где Гз - время записи информации в память накапливающего сумматора 3, последний обнуляется, а под действием импульса с второго установочного выхода 10, задержанного относительно импульса с выхода Ют коммутации на время г 4 обнуляется первый блок 7 регистров.

Под действием первого импульса с третьего управляющего выхода Ювс выхода блока 4 памяти приращений коэффициентов на второй вход блока 5 элементов И поступает код приращения весового коэффициента, соответствующий последний входной дискрете, но так как время задержки этого импульса относительно импульса на первом управляющем выходе 102 больше г 4, то на первый вход блока 5 элементов И поступает код нуля, что исключает влияние данной ситуации на правильность результата фильтрации. На этом заканчивается процесс подготовки к очер едному циклу фильтрации,

Таким образом, момент обнуления накапливающего сумматора 3 и первого блока 7 регистров является моментом готовности цифрового нерекурсивного фильтра к очередному циклу фильтрации.

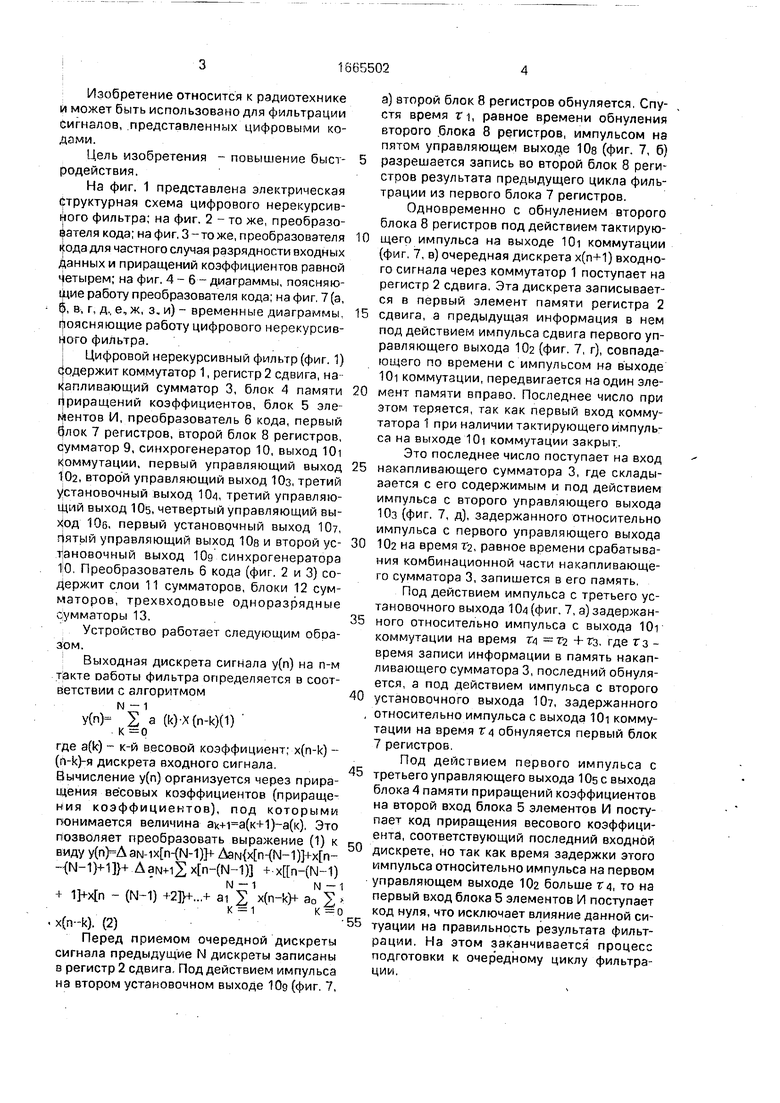

Процесс очередного цикла фильтрации начинается с момента появления на первом управляющем входе 102 первого импульса сдвига, несовпадающего по времени с тактирующим импульсом на выходе 10i комму- тации (фиг. 7 в и г), Под его воздействием х(п+1-М)я дискрета, находящаяся е правом элементе памяти регистра 2 сдвига, поступает в обнуленный накапливающий сумматор 3 и образует первую частичную сумму. Одновременно эта же дискрета через первый вход коммутатора 1, который открыт на время отсутствия тактирующего импульса поступает в освободившийся под воздействием сдвигающего импульса первый левый элемент памяти регистра 2 сдвига. Спустя время TS Г2 4-гз, под действием импульса на третьем управляющем выходе Юз из блока 4 памяти приращений весовых коэффициентов на второй вход блока 5 элемен- тов И поступает код приращения весового коэффициента, соответствующий первой частичной сумме. Таким образом, обеспечивается одновременное поступление на блок 5 элементов И первой частичной суммы с выхода накапливающего сумматора 3 v. соответствующего ей приращения весового коэффициента Дам-1 с выхода блока 4 памяти приращений весовых коэффициентов. 8 результате на выходе блока 5 элементов И сформирован многострочный код (матрица частичных произведений), соответствующий первому слагаемому выражения (2). Вид такого многострочного кода представлен на фиг. 4 для разрядности данных и приращений коэффициентов равной четырем (на фиг, 4-6 сверху цифрами обозначены номера разрядов). При этом блок 4 памяти приращений коэффициентов обеспечивает выдачу кода на второй вход блока 5 элементов И в течение времени

Тбп Тп + tnk + TRUl

где rn - время срабатывания блока 5 элементов И;

г nk время, в течение которого преоб- разовзтель 6 кода преобразует многострочный код в двухстрочный;

TROI - время записи информации в первый блок 7 регистров.

М ногострочный код, соответствующий первому частичному произведению, с выхода блока 5 элементов И поступает на вход преобразователя 6 кода и за два такта его работы преобразуется в двухстрочный код

5

10 15 20 25 30 35 40 5.

0

5

(фиг. 4), На фиг. 4 и далее рамками обозначены числа, поступающие на вход одного трехвходового одноразрядного сумматора 13. Трехвходовые одноразрядные сумматоры 13, работающие в один и тот же момент времени, объединяются в один слой сумматоров 12, Номера тактов работы преобразователя 6 кода обозначены цифрами на фиг. 4-6 слева.

Полученный таким образом двухстрочный код, записывается в первый блок 7 регистров, на вход приема которого воздействует импульс с четвертого управляющего выхода 10б (фиг. 7, и), задержанный относительно сдвигающего импульса (фиг, 7, г) на время

re Г2 +гз +Тп +гп|. на этом заканчивается первый цикл сдвига.

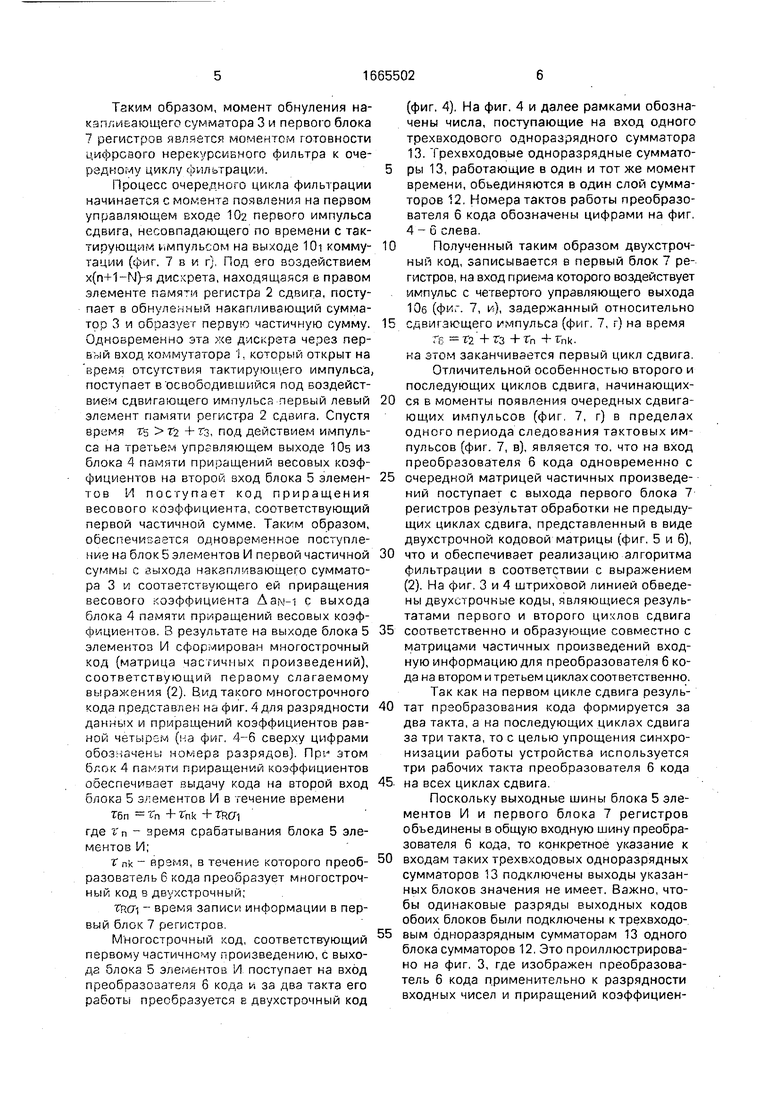

Отличительной особенностью второго и последующих циклов сдвига, начинающихся в моменты появления очередных сдвигающих импульсов (фиг, 7, г) в пределах одного периода следования тактовых импульсов (фиг. 7, в), является то, что на вход преобразователя 6 кода одновременно с очередной матрицей частичных произведений поступает с выхода первого блока 7 регистров результат обработки не предыдущих циклах сдвига, представленный в виде двухстрочной кодовой матрицы (фиг. 5 и 6), что и обеспечивает реализацию алгоритма фильтрации в соответствии с выражением (2). На фиг, 3 и 4 штриховой линией обведены двухстрочные коды, являющиеся результатами первого и второго циклов сдвига соответственно и образующие совместно с матрицами частичных произведений входную информацию для преобразователя 6 кода на втором и третьем циклах соответственно.

Так как на первом цикле сдвига результат преобразования кода формируется за два такта, а на последующих циклах сдвига за три такта, то с целью упрощения синхронизации работы устройства используется три рабочих такта преобразователя 6 кода на всех циклах сдвига.

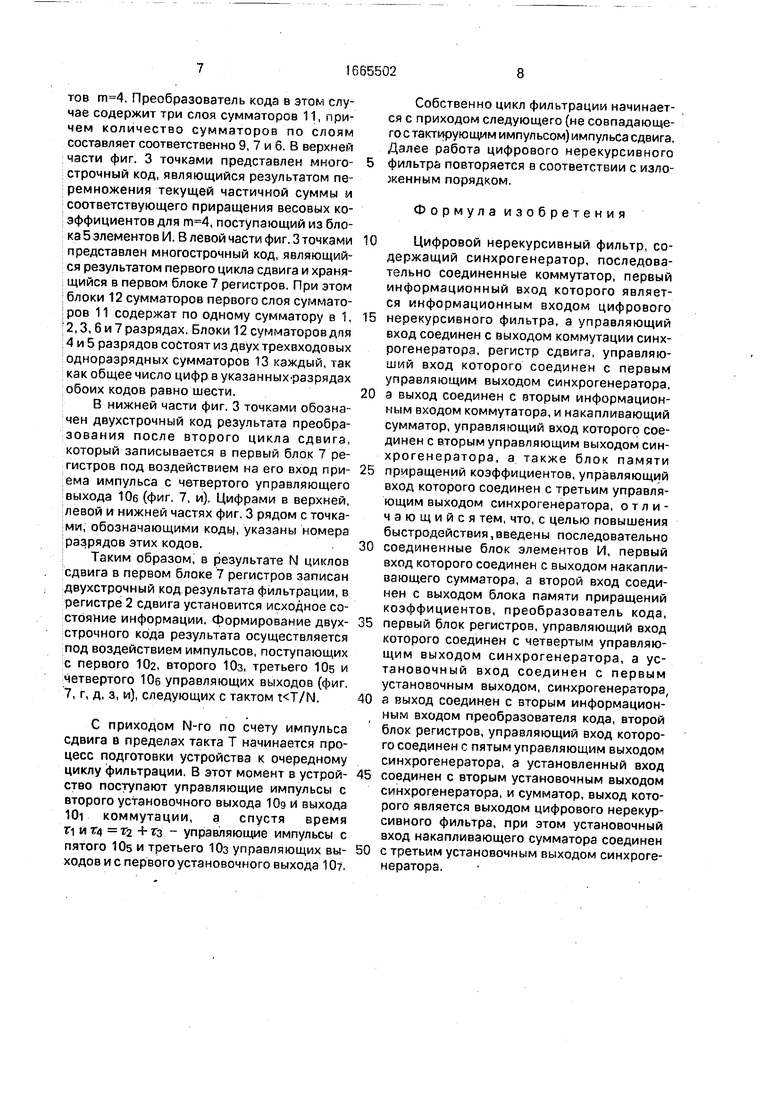

Поскольку выходные шины блока 5 элементов И и первого блока 7 регистров объединены в общую входную шину преобразователя 6 кода, то конкретное указание к входам таких трехвходовых одноразрядных сумматоров 13 подключены выходы указанных блоков значения не имеет. Важно, чтобы одинаковые разряды выходных кодов обоих блоков были подключены к трехвходо- вым одноразрядным сумматорам 13 одного блока сумматоров 12, Это проиллюстрировано на фиг, 3, где изображен преобразователь 6 кода применительно к разрядности входных чисел и приращений коэффициентов , Преобразователь кода в этом случае содержит три слоя сумматоров 11, причем количество сумматоров по слоям составляет соответственно 9, 7 и 6. В верхней части фиг. 3 точками представлен много- строчный код, являющийся результатом перемножения текущей частичной суммы и соответствующего приращения весовых коэффициентов для , поступающий из блока 5 элементов И. В левой части фиг. 3 точками представлен многострочный код, являющийся результатом первого цикла сдвига и хранящийся в первом блоке 7 регистров. При этом блоки 12 сумматоров первого слоя сумматоров 11 содержат по одному сумматору в 1, 2,3, 6и7разрядах. Блоки 12 сумматоров для 4 и 5 разрядов состоят из двух трехвходовых одноразрядных сумматоров 13 каждый, так как общее число цифр в указанных-разрядах обоих кодов равно шести.

В нижней части фиг. 3 точками обозначен двухстрочный код результата преобразования после второго цикла сдвига, который записывается в первый блок 7 регистров под воздействием на его вход приема импульса с четвертого управляющего выхода 10е (фиг, 7, и). Цифрами в верхней, левой и нижней частях фиг. 3 рядом с точками, обозначающими коды, указаны номера разрядов этих кодов.

Таким образом, в результате N циклов сдвига в первом блоке 7 регистров записан двухстрочный код результата фильтрации, в регистре 2 сдвига установится исходное состояние информации. Формирование двухстрочного кода результата осуществляется под воздействием импульсов, поступающих с первого Юз, второго Юз, третьего ЮБ и четвертого 10е управляющих выходов (фиг. 7, г, д, з, и), следующих с тактом .

С приходом N-ro по счету импульса сдвига в пределах такта Т начинается процесс подготовки устройства к очередному циклу фильтрации. В этот момент в устройство поступают управляющие импульсы с второго установочного выхода 10э и выхода 10i коммутации, а спустя время П и Т4 Г2 + гз - управляющие импульсы с пятого 10s и третьего Юз управляющих выходов и с первого установочного выхода 10у.

Собственно цикл фильтрации начинается с приходом следующего (не совпадающего с тактирующим импульсом) импульса сдвига. Далее работа цифрового нерекурсивного фильтра повторяется в соответствии с изложенным порядком.

Формула изобретения

Цифровой нерекурсивный фильтр, содержащий синхрогенератор, последовательно соединенные коммутатор, первый информационный вход которого является информационным входом цифрового

нерекурсивного фильтра, а управляющий вход соединен с выходом коммутации синх- рогенератора, регистр сдвига, управляющий вход которого соединен с первым управляющим выходом синхрогенератора,

а выход соединен с вторым информационным входом коммутатора, и накапливающий сумматор, управляющий вход которого соединен с вторым управляющим выходом син- хрогенератора, а также блок памяти

приращений коэффициентов, управляющий вход которого соединен с третьим управляющим выходом синхрогенератора, отличающийся тем, что, с целью повышения быстродействия,введены последовательно

соединенные блок элементов И, первый вход которого соединен с выходом накапливающего сумматора, а второй вход соединен с выходом блока памяти приращений коэффициентов, преобразователь кода,

первый блок регистров, управляющий вход которого соединен с четвертым управляющим выходом синхрогенератора, а установочный вход соединен с первым установочным выходом, синхрогенератора,

а выход соединен с вторым информационным входом преобразователя кода, второй блок регистров, управляющий вход которого соединен с пятым управляющим выходом синхрогенератора, а установленный вход

соединен с вторым установочным выходом синхрогенератора, и сумматор, выход которого является выходом цифрового нерекурсивного фильтра, при этом установочный вход накапливающего сумматора соединен

0 с третьим установочным выходом синхрогенератора.

. 81 В S Ч 3 I 19 8 7 ff 5 3 г

la з в 7 е s t з г i

| Цифровой нерекурсивный фильтр | 1980 |

|

SU942247A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-07-23—Публикация

1989-08-14—Подача