(54) КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1980 |

|

SU869032A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство управления электромагнитным железоотделителем | 1990 |

|

SU1801584A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Распределитель сигналов | 1974 |

|

SU525073A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| СПОСОБ ДИСКРЕТНОГО КОНТРОЛЯ РАССТОЯНИЙ ДО ИСТОЧНИКА КОЛЕБАНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2028579C1 |

t

Изобретение относится к области автоматики и т елемеханики.

Известны коммутаторы, содержащие генератор, выход которого соединен со входом распределителя, а также ключи и элемент или 1,

К недостаткам такого устройства относятся узкие функциональные возможности.

Наиболее близким техническим решением к данному является коммутатор содержащий генератор, выход которого соединен со входом (пч)-разрядного/ распределителя, первый разрядный выход которого через формирователь реперного сигнала подк.шочен к одному из входов ()-входного элемента ИЛИ, другие входы которого соединены с выходс1ми ключей, управляющий вход Кс1ждого из которых подключен к соответствующей информационной входной шине коммутатораf выходная шина которого соединена с выходом (nfl)входного элемента ИЛИ 2,

Недостатком Данного устройства являются узкие функциональные возможности.

Целью изобретения является расширение функциональныгг возможностей коммутатора.

Указанная цель достигается за счет того, что в KOMMyTiaTop, содержащий 1гёйЩ5а бр,ваход которого- соединен со входом (n-tl)-разрядного распределителя, первый разрядный выход которого через формирователь реперного сигнала подключен к одному из входов ()-входного элемента ИЛИ, другие входы которого соединены с выходами

0 ключей, управляющий вход каждого из которых подключен к соответствукяцей информационной входной шине коммутатора , выходная шина которого соединена с выходом (п-4-1)-входного элемг

5 та ИЛИ, введены триггеры, элементы ИЛИ, И и Запрет и дополнительный фо. мирователь, выход которого соединен с дополнительным входом (п-И)-разрядного распределителя и нулевыми вхо0дами триггеров, причем в каждом канале коммутатора, кроме первого и последнего, соответствующий выход (п+1)-рязряднЬго .распределителя соединен с одним из входов первого эле5мейта ИЛИ, другой вход которого подключен к выходу элемента И предьвдуиего канала, а выход - к прямому входу элемента Запрет и одному из входов элемента И своего канала, другой

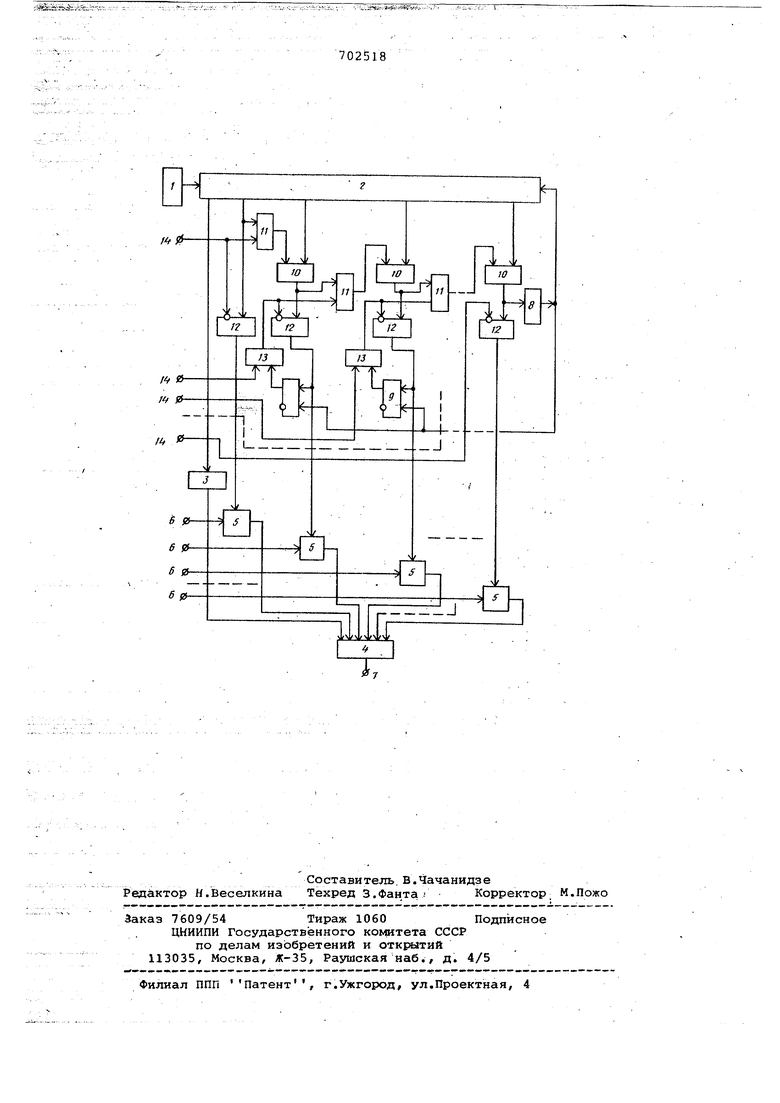

0 вход которого соединен с инверсным входом элемента Запрет и выходом второго элемента ИЛИ, один из входов которого подключен к соответствующей шине управления, а другой, соединен с единичным выходом триггера, единичный вход Которого подключен к выходу элемента Эапрет и управляющему входу соответствующего ключа, в первом канале коммутатора второй разрядный выход (п+1)-рязрядного распределителя соединен с прямым входом элемента Запрет и одним из входов элемента И, другой .вход которого, подключен к перв.ой шине управления и инверсному входу элемента Запрет, выход которого соединен с управляющим входом первого канала, а в последнем канале коммутатора последний выход (п-И)-разрядного распределителя подключен .к одному из входов элемента ИЛИ, другой вход которЬго соединен;.С выходом элемента И (п.-1)-гЬ канала, а выход . - с входом дополнительного формирова теля .и прямым входом элемента Запрёт инверсный вход которого подключен ю п-й шине управления, а выход -к управляющему входу .п-го ключа. Функциональная схема коммутатора представлена на чертеже и содержит следующие элементы: генератор 1, выход которого соединен со входом (п + 41)-разрядного распределителя 2,пер выйразрядный выход которого через формирователь 3 реперного сигнала подключен к одному из входов -(n+l)входного элемента ИЛИ 4, другие входы которого соединены с. выходами клю чей 5, управляющий вход каждого из к торых подключен к соответствующей ин формационной входной шине б коммутатора, выходная шина 7 которого соеди нена с выходом (п + 1)-входного элемен та ИЛИ 4; дополнительный формирователь 8, выход которого соединен с до -полнительным входом (п+-1)-разрядного распределителя 2 и нулевыми входами триггеров 9; в каждом канале, кроме первого и последнего, соответствующи выход (n-vD-разрядного распределителя 2 соединен с одним из входов первого элемента ИЛИ 10, другой вход ко торого подключен к выходу элемента И 11 предыдущего канала, а выход - к прямому входу элемента Запрет 12 и одному из входов элемента И 11 своего канала, другой вход которого соедйне н с инверсным входом элемента Запрета 12 и выходом второго элемента иЛи 13, один из входов которого подключен к соответствующей шине 14 управления, а другой соединен с единичным выходом триггера 9, единичный вход которого подключен к выходу эле мента Запрет 12 и управляющему входу соответствующего ключаЗ; s первом ка нале коммутатора второй разрядный вы ход (n-Vl)-разрядного распределителя 2 соединен с прямым входом элемента Запрет 12 и одним из входов элемента И 11, другой вход которого подключен к первой шине 14 управления и инверсному входу элемента .Запрет 12, выход которого соединен с управляющим входом первого ключа 5; в последнем канале . коммутатора последний .выход (n-f fl)-разрядного распределителя 2 подключен к одному из входов элемента ИЛИ 10, другой вход которого соединен с выходом элемента И 11 (п--1)-го канала, а выход - с входом дополнительного формирователя 8 и прямым входом элемента Запрет 12,. инверсный йход которого подключен к п-й шине 14 управления, а выход - к управляющему входу п-го ключа 5.. - .. Функционирование коммутатора осуществляется следующим образом. Им-.пульсом с выхода генератора 1 запускается распределитель 2, с первого разрядного выхода которого реперный сигнал через формирователь 3 и элемент .4 поступает на выходную шину 7 коммутатора. В случае наличия нулевых логических уровней на шине 14 управления единичный логический уровень со второго разрядного выхода распределителя 2 через элемент Запрет-12 первого канала поступает на управляющий вход первого ключа 5 и осуществляет подключение первой информацион- ной входной шины 6 к выходной шине 7. Далее единичный логический уровень с третьего разрядного выхода распределителя 2 через элементы ИЛИ 10 и З.апрет 12 второго канала поступает на управляющий вход второго ключа 5 и переводит триггер 9 этого канала в единичное состояние. В результате вторая информационная входная шина б подключается к выходной шине 7 и т.д. Единичный логический уровень с последнего разрядного выхода распределителя 2 .через элементы ИЛИ 10 и Запрет 12 поступает на управляющий вход последнего ключа 5 и осуществляет подключение последней информационной шины б к выходной шине 7. Одновременно при помощи единичного логического уровня с выхода элемента ИЛИ 10 последнего канала через дополнительный формирователь 8 осуществляется перевод триггеров 9 в нулевое,состояние и запуск распределителя 2, Если на 1-й шине 14 управления имеется единичный логический уровень, то единичный логический уровень с (f+l)-ro разрядного выхода распределителя 2 или с выхода, элемента И 11 предыдущего канала через элементы 10 и И 11 подается на элемент -; ИЛИ 10 по- j следующего канала и поступит на ключ 5 первого из последующих каналов, на шине 14 управления которого имеется нулевой логический уровень. Указанный уровень одновременно переводит в единичное состояние триггер 9 этого канала, запрещая тем самым прохождение единичного логического уровня с (i42)-ro разрядного выхода распределитель на управляющий вход ключа 5 этого канала. Формула изобретения Коммутатор, содержащий генератор, выход которого соединен .со входом (n+l)-разрядного распределителя, пер вый разрядный выход которого через формирователь реперного сигнала подключен к одному из входов (пч-1)-вход ного элемента. ИЛИ, другие входы которого соединены с выходами ключей, управляющий вход каждого из которых подключен к соответствующей информац онной входной шине коммутатора, вы-, ходная шина которого соединена с выходом (п+1)-входного элемента ИЛИ, отличающийся тем, что, с целью расширения функциональных возможностей,, в него введены триггеры, элементы ИЛИ, И и Запрет и дополнительный формирователь, выход которого соединен с Дополнительным входом (п+1)-разрядного распределителя и ну левыми входами триггеров, причем в каждом Канале коммутатора, кроме пер .вого и последнего, соответствующий вы.ход (пН)-разрядного распределител соединен с одним из входов первогб элемента ИЛИ, другой вход которого подключен к выходу элемента И предыдущего канала, а выход - к -прямому входу элемента Запрет и одному из входов элемента И своего канала, другой вход которого соединен с инверсным входом элемента Запрет и выходом второго элемента ИЛИ, один из входов которого подключен к соответствующей шине управления, а другой соединен с единичным выходом триггера, единичный вхйд которого подключен к выходу элемента Запрет и управляющему входу соответствующего ключа, в первом канале коммутатора второй разрядный выход (n+l)-разрядного распределителя соединен с прямым входом -элемента Запрет и одним из входов элемента И, другой вход которого подключен к .первой шине управления и инверсному входу элемента Запрет, выход которого соединен с управляющим входом первого ключа, а в последием.канале коммутатора последний выход (п-«-1)-разрядного распределителя подключен к одному из входов элемента ИЛИ, другой вход которого соединен с выходом элемента И (п-1)-го Канала, а выход с входом дополнительног-о формирователя и прямым входом элемента Запрет, инверсный вход которого подключен к п-й шине управления, а выход - к управляющему входу п-го ключа. Источники информации, принятые во внимание при экспертизе 1.С.А.Гинзбург и др. Основы автоматики и телемеханики, М., Гос. энергетическое изд-во, 1959, с. 440., рис. 15-24. . 2,Авторское свидетельство 506942, кл. Н 03 К 17/02, 25.01.74.. .

702518

60

Авторы

Даты

1979-12-05—Публикация

1977-05-16—Подача