Изобретение относится к вычислительной .технике и может быть исполь- эовано в вычислительных системах автоматизации научных исследований,

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения доступа к внешней памяти вычислительной системы.

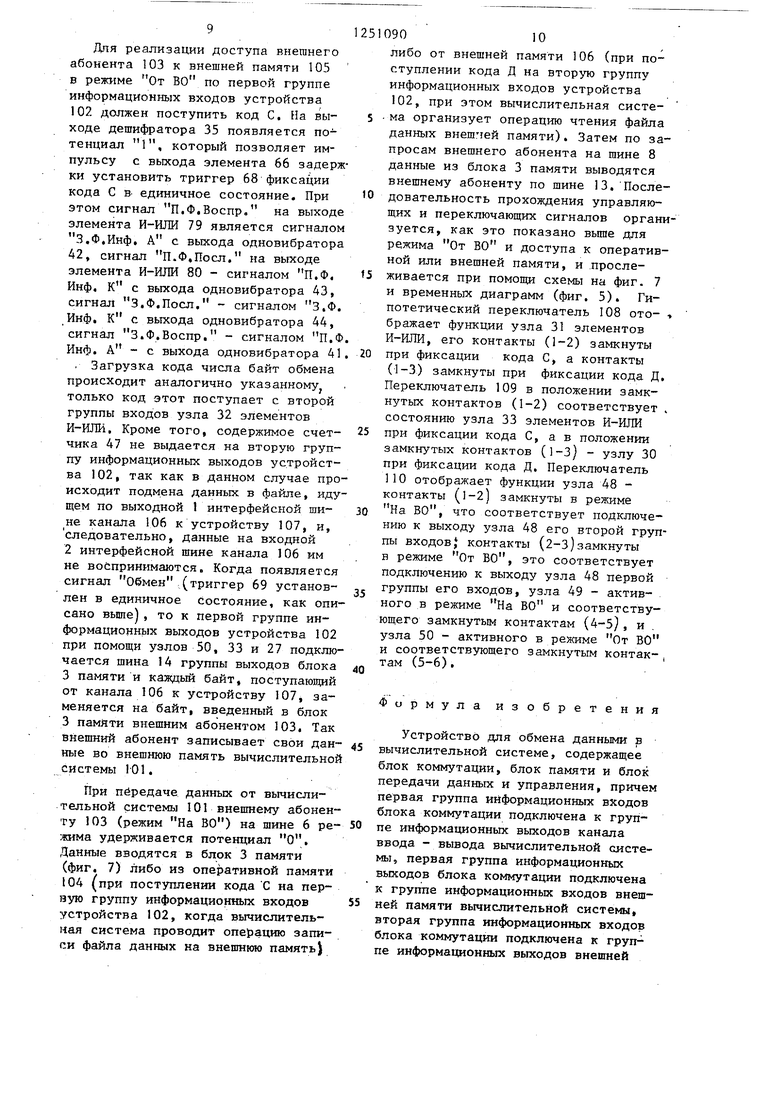

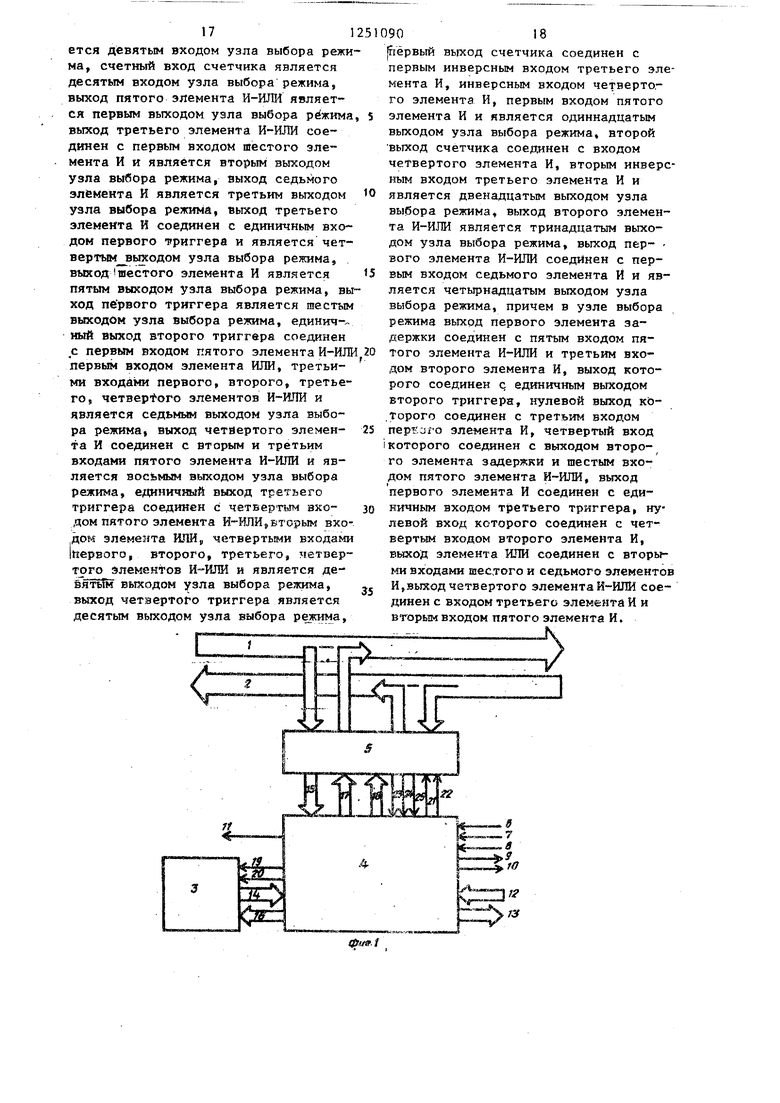

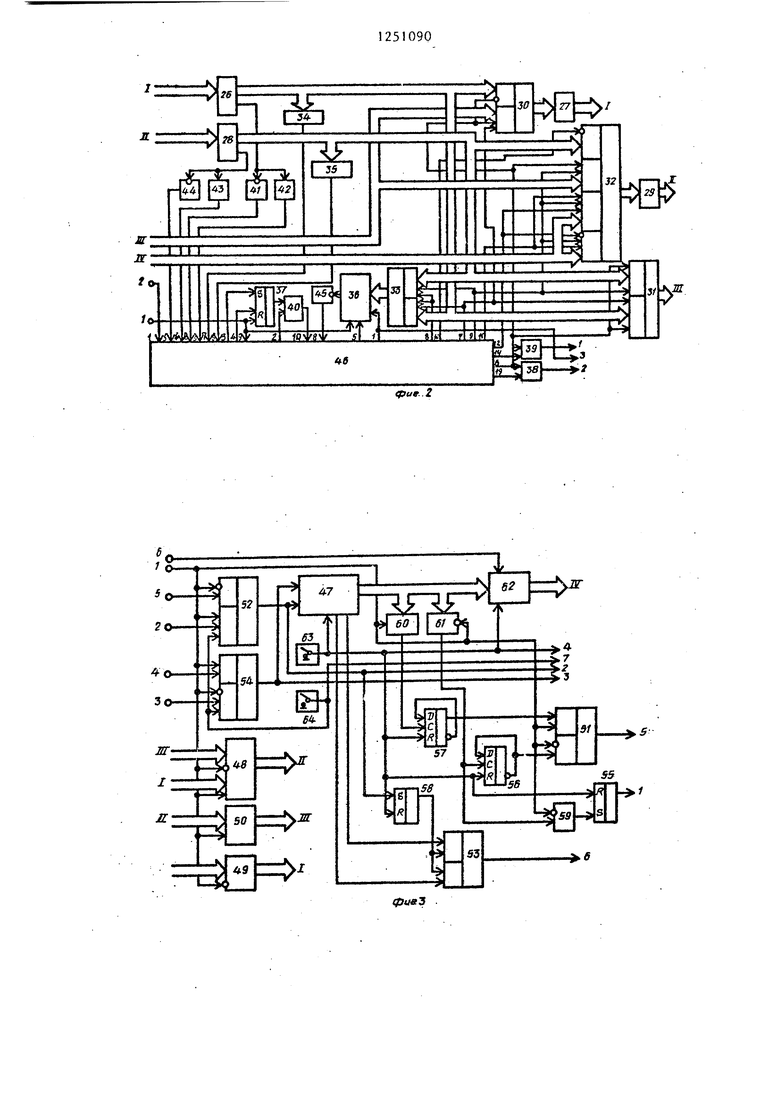

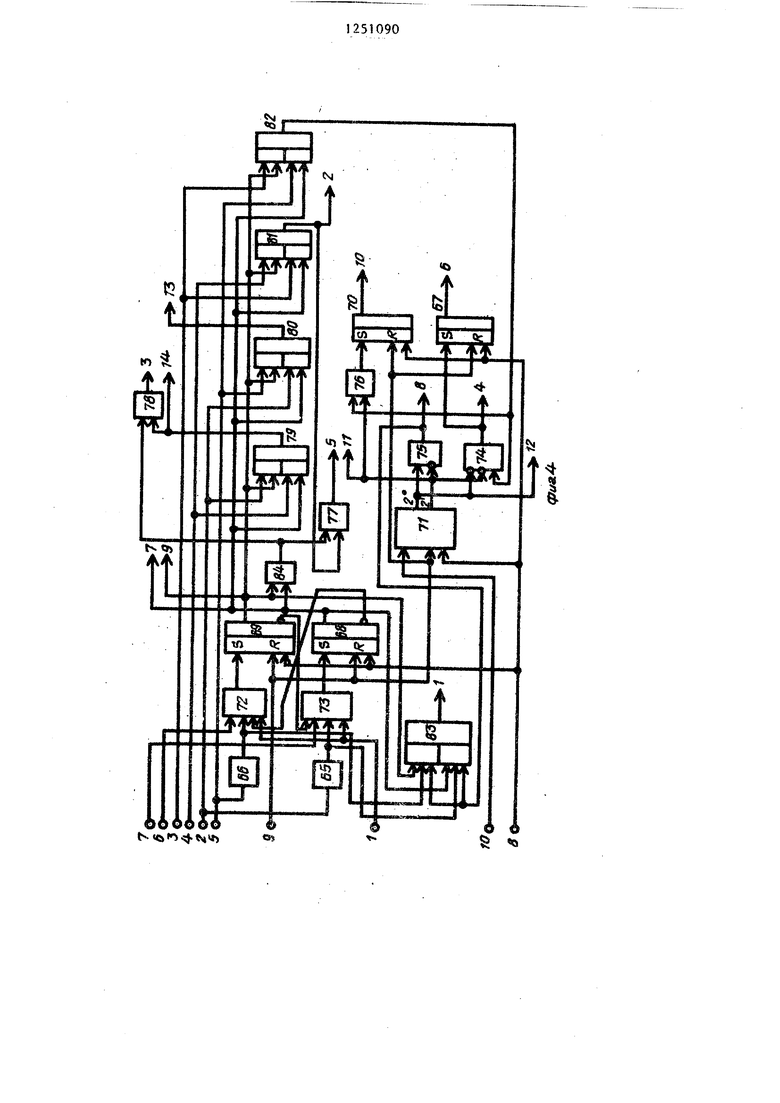

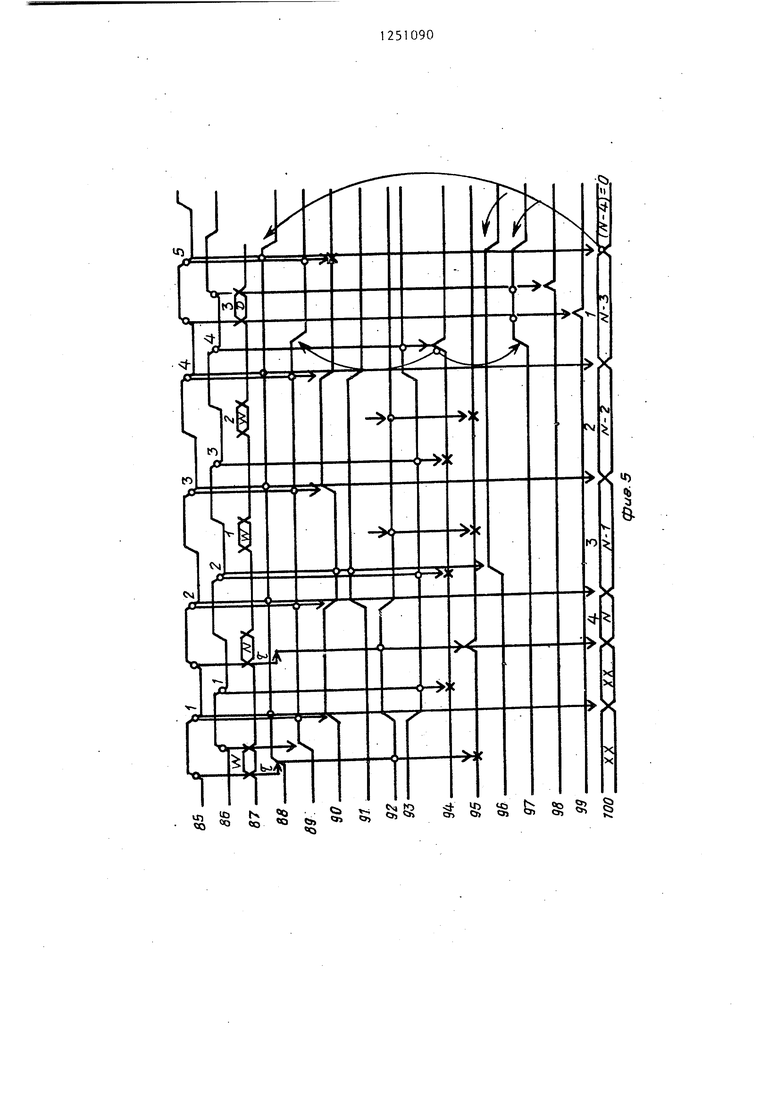

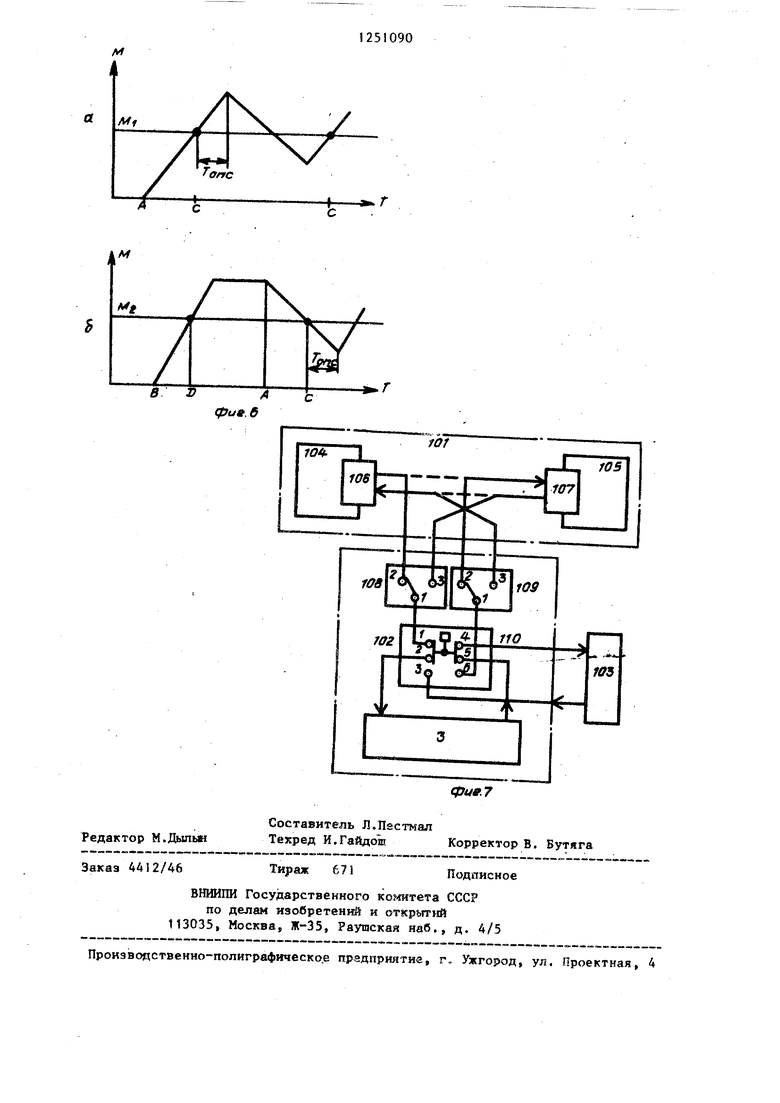

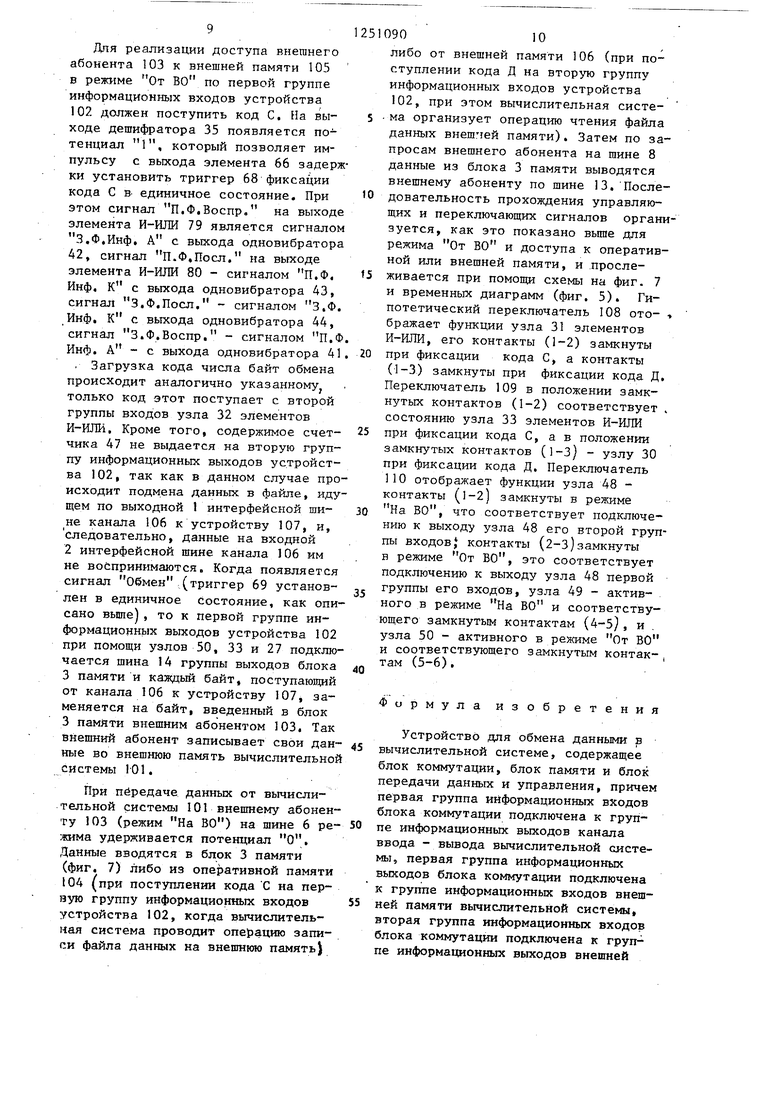

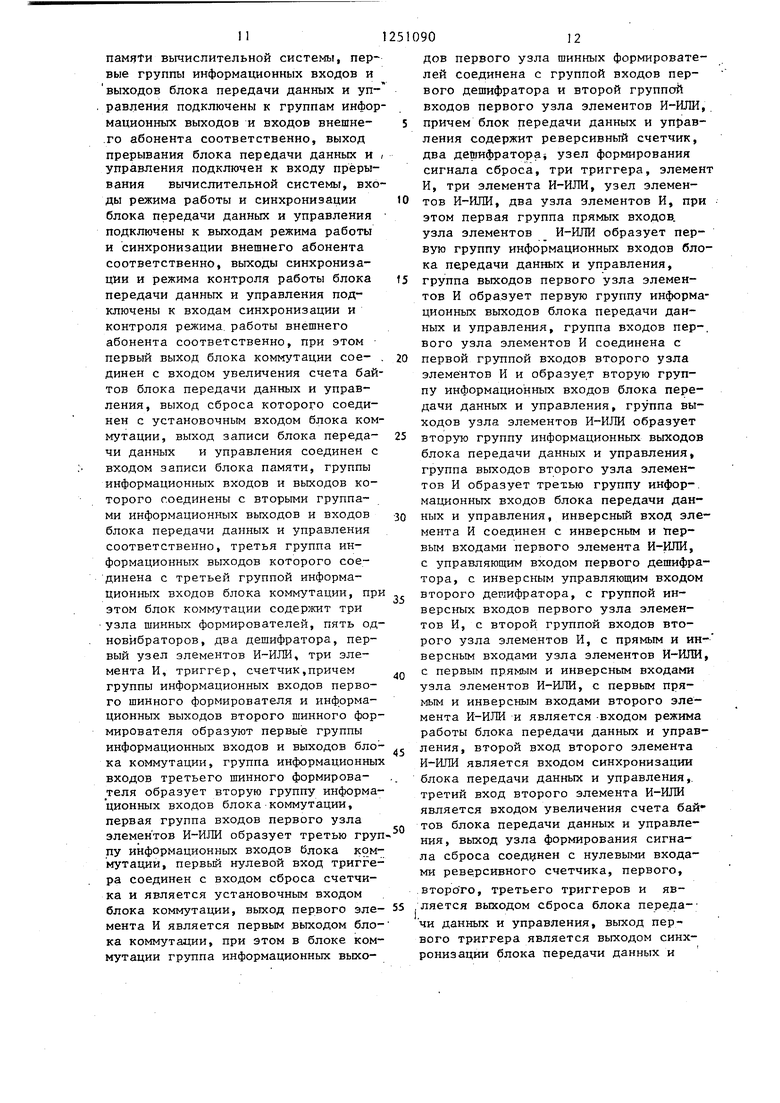

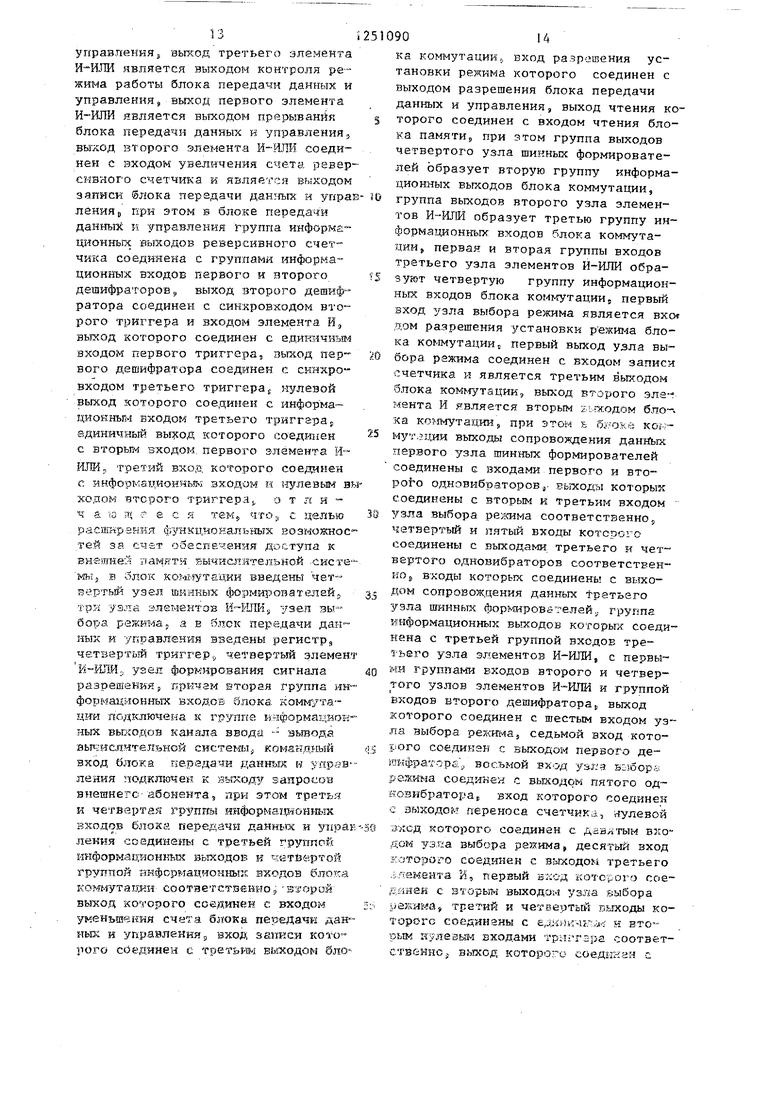

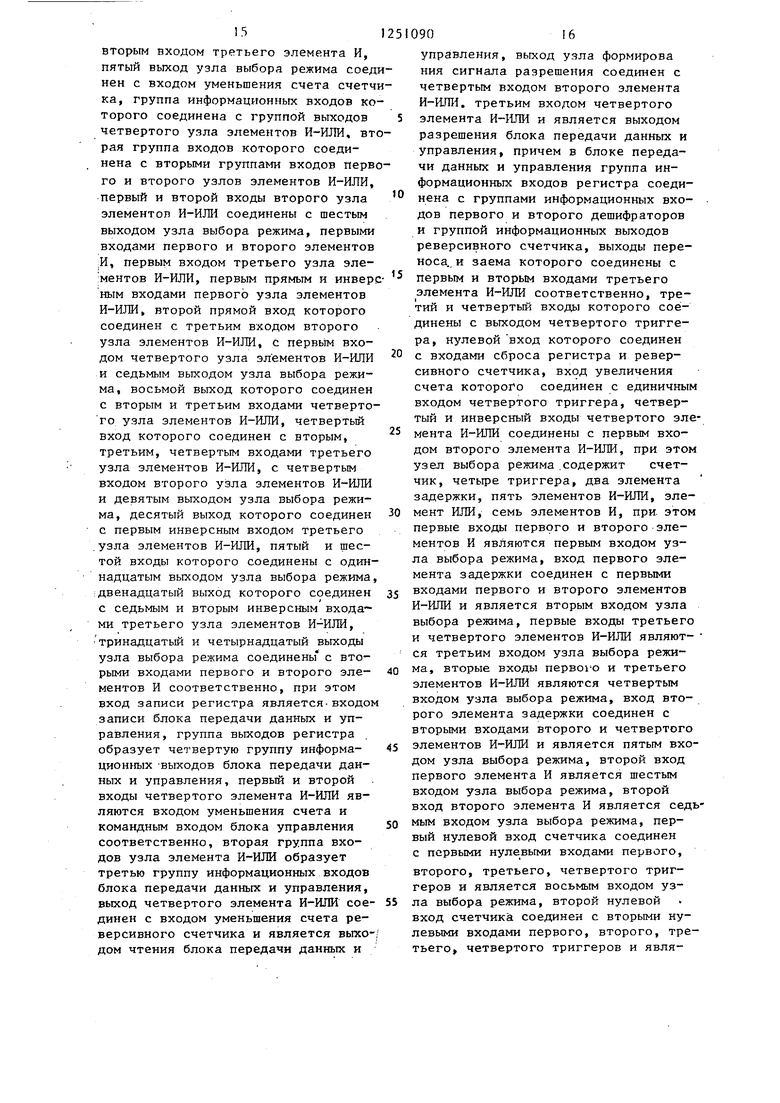

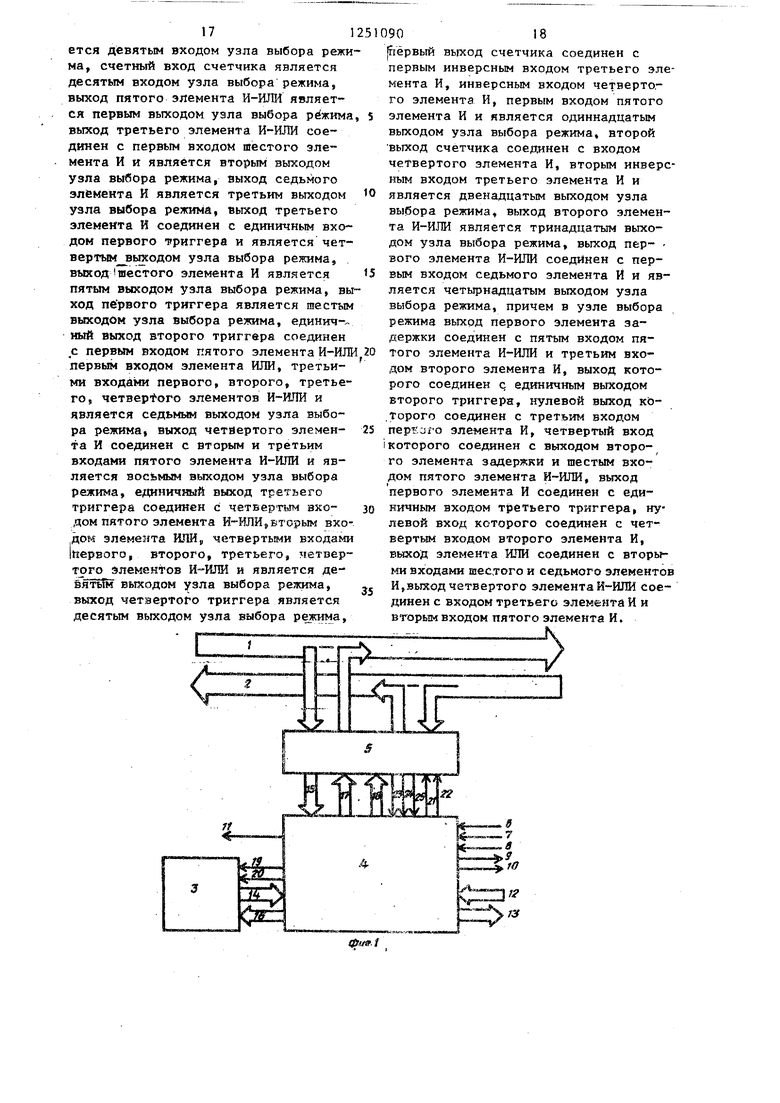

На фиг. 1. представлена блок-схе ма устройстваJ на фиг. 2, 3 и 4 - функциональные схемы блока коммутации, блока передачи данных и управления и узла выбора режима; на фиг. 5 - временные диаграммы работы узла выбора режима и блока коммутации J на фиг. 6 - временные диаграммы распределения объема памяти для режимов От ВО (а) и На ВО (б), на фиг. 7 - схема прохождения ин- формацио ных сигналов при организации обмена между вычислительной системой и внешним абонентом.

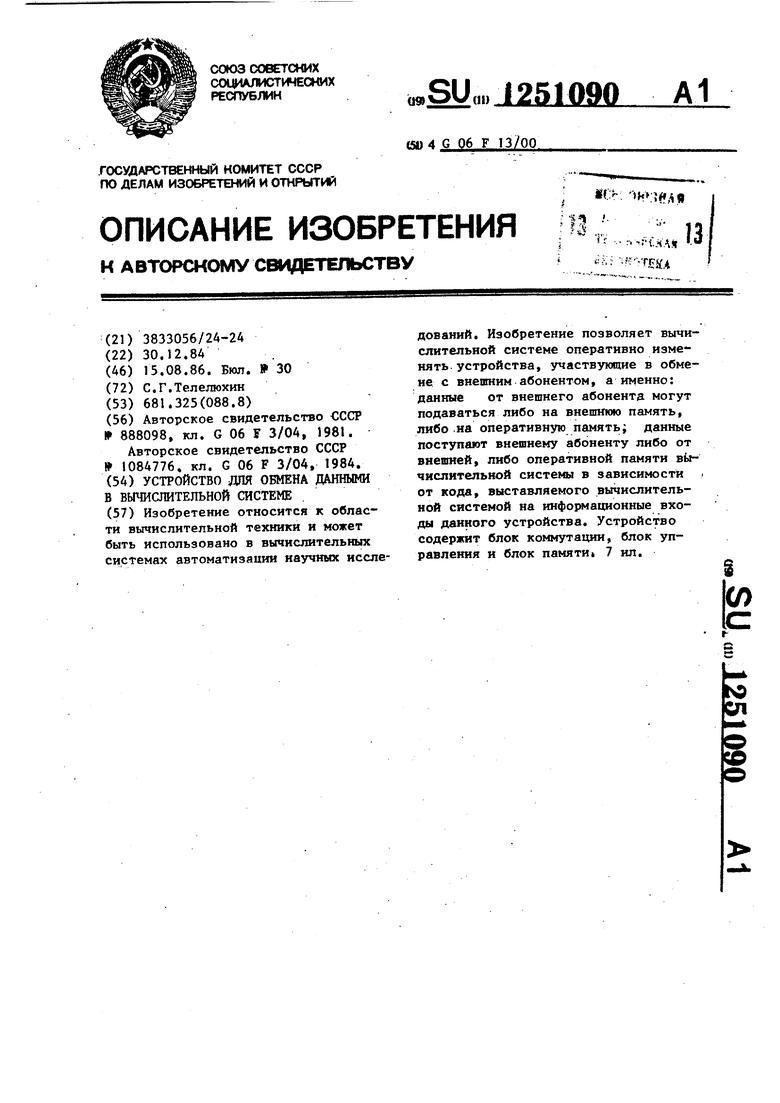

Устройство получает доступ к внеш ней и оперативной памяти вычислительной системь: посредством подключения к выходной 1 и входной 2 интерфейсным шинам канала ввода-вывода вычислительной системы, часть линий которых образуют соответственно первую и вторую группы информационных входов и выходов устройства.

Устройство содержит (фиг. 1) блок 3 памяти, блок 4 передачи данных и управления, блок 5 коммутации, шины 6-1 входа режима, входа синхронизации, входа команды, выхода синхронизации, выхода,контроля и выхода прерывания устройства соответственно входную 12 и выходную 13 шины групп информационных входов и выходов устройства.

На фиг. 1 показаны также входные 14 и 15 и выходные 16 и 17 шины вто рой и третьей групп информационных входов и выходов блока 4 управления, выходная 18 шина четвертой группы информационных выходов блока 4, а также шины 19-22 выходов блока 4 и шины 23-25 входов блока 4.

Блок 5 коммутации содержит (фиг. 2 узлы 26-29 шинных формирователей, узлы 30-33 элементов И-ИЛИ, дешифраторы ЗА и 35, счетчик 36, триггер 37, элементы И 38-40, формирователи импульса (одновибраторы) 41-45 и узел 46 выбора режима.

0

5 о

..

0

S

5

Блок 4 содержит (фиг, 3) двоичный счетчик (реверсивный) 47, узел 48 элементов И-ИЛИ, узлы 49 и 50 элементов И, элементы И-ИЛИ 51-54, триггеры 55-58, элемент И 59, дешифраторы 60 и 61, регистр 62, узел 63 формирования сигнала Сброс и узел .64 формирования сигнала Разреше- тшя.

Узел 46 выбора- режима содержит (фиг. 4) элементы 65 и 66 задержки, триггеры 67-70, двоичный счетчик 71 , элементы 72-78 И, элементы И-ИЛИ 79- 83 и элемент 84 ИЛИ.

На фиг. 5 обозначены сигналы Байт послан 85, Байт воспринят 86, данные на птне интерфейса 87, сигнал 88 фиксации команды на выходе триггера 67 (или 68), сигнал 89 на выходе триггера 37, сигналы 90 и 91 на выходе первого (2) и второго (2) разрядов двоичного счетчика 71, сигнал 91 является также сигналом Маска М на одиннадцатом выходе узла 46 выбора режима, сигнал 92 Маска К на восьмом выходе узла 46, логический 93 сигнал и 2 на элементе 74, сигнал 94 Сброс триггера 37, сигнал 95 загрузки кода длины файла обмена в двоичный счетчик 36, сигнал 96 Подмена данных на десятом выходе узла 46 выбора режима, сигнал 97 Обмен на шестом выходе узла 46, сигнал 98 Запрос очередного байта на выходе элемента 39 И, сигнал 99 Сопровождение текущего байта на выходе элемента 40 И, состояние 100 двоичного счетчика 36.

На фиг. .6 обозначено: М - текущий объем заполненной памяти блока 3, М и Мг - граничные объемы для формирования сигнала Прерывание в режимах От ВО и На ВО соответственно; Т - текущее время; Т - время реакции на сигнал Прерывание А - моменты начала работы внешнего абонента; В - начала обмена канала с внешней памятью; С - формирование сигнала Прерывание j Д - формирование сигнала Пуск внешнего абонента.

На фиг. 7 обозначено: вычислительная система 101, устройство 102 ;у1я обмена информацией, внешний абонент 103, оперативная 104 и внешняя 105 память вычислительной систе- мы, канал 106 ввода-вывода, устJ

ройство 107 управления внешним устройством, гипотетические переключа тели 108, 109 и 110 информационных потокой.

Узлы 30, 31, 32, 33 и 48 элемен- тов И-ИЛИ выполняют функции мультиплексирования входных групп и содержат, на примере узла 48j ряд элементов 2И-2И-2ИЛИ, первые входы элементов 2И объединены (причем один из них инвертирующий вход) и подключены к управляющему входу узла,а к вторым входам подключаются одноименные линии из состава шин первой и второй входньгк групп узла, а выхо- ды элемента 2И-2И-2ИЛИ являются выходом отдельной линии в группе выходов узла, Одновибраторы 42 и 44 формируют выходной импульс по заднему фронту входного сигнала (перепад 1 - О), Одновибраторы 41, 43 и 45 с инвертирующим входом формируют импульс по переднему фронту входного сигнала. Узел 63 формирования сигнала Сброс содержит электричес- кий переключатель без фиксации, на контакте 11 которого установлен потенциал О, поступающий на выход узла (контакт 112) в положении Кнопка нажата. Узел формирования сигна- ла Разрешение содержит тумблер, на контакте 113 которого установлен потенциал О, а на контакте 114 - 1, В положении Работа замкнуты контакты 114-115, в положении Транзит замкнуты контакты И3-115,

.Устройство работает следующим об- paSoM,

Кнопкой узла 63 подается сигнал установки в О всех счетчиков, триг геров и регистра устройства. При потенциале О, на выходе узла 64 устройство 102 дпя обмена информацией находится в режиме транзитной передачи данных. Физически устройство 102 подключено в разрыв шин данных канала (I taH. К) и данных абонента (Шин А) интерфейсного кабеля, соединяющего канал 106 ввода-вывода и устройство 107 управления внешним уст- ройством в составе вычислительной системы 101,

Первая группа информационных входов ус -ройства 102 подключается к линии сигнала идентификации данных канала (Инф, К) и шине данных Шин, К выходной 1 интерфейсной шины канала. При этом данные, пере0904

даваемые по Шин, К, поступают на узел 26 и далее на вторую группу входов узла 33 элементов И-ИЛИ, Синал О с выхода триггера 69 разрешает прохождение этих данных на узел 27, группа выходов которого является первой группой информационых выходов устройства 102 и подключена к части шины Шин, К выходной 1 интерфейсной шииы канала, соединенной с входом устройства 107, Следовательно, данные от канала 106 транзитом поступают на усройство 107,

Вторая группа информационных входов устройства 102 подключается к линии сигнала иденти4н1кации данных абонента (Инф, А) и шине данных Шин, А входной 2 интерфейсно шины канала. Данные, передаваемое устройством 107 по Шин, А, поступают на узел 28 и далее на третью группу входов узла 30 И-ИПИ, Сигнал О с выхода триггера 70 и 67 разрешает прохождение этих данных на узел 29, группа выходов которо- го является второй группой информационных выходов устройства 102 и .подключена к части шины Шин. , соединенной с входом канала 106, при этом данные от устройства 107 транзитом поступают к каналу 106,

Потенциал О с выхода узла 64 подается также на входы элементов И-ИЛИ 53 и 54 и блокирует сигналы внешнего объекта на входе 7 синхронизации и входе 8 команды устройства 102,

При переводе тумблера узла 64 в положение Работа на выходе узла 64 устанавливается потенциал 1, который снимает блокировку сигналов внешнего абонента с входов 7 и 8 и разрешает стробирование на элементах И 72 и 73 сигналов с выходов дешифраторов 34 и 35,

При передаче данных от внешнего абонента 103 к вычислительной системе 101 (режим От ВО) на шине 6 режима удерживается потенциал 1, Данные внешнего абонента с шины 12 подаются узлом 48 элементов И-ИЛИ на шину 16 входа памяти, запись в которую осуществляется по импульсу на шине 19 Запрос записи. Этим импульсом является сигнал Сопровождение от во на шине 7 синхронизначения М, на выходе дешифратора 61 формируется потенциал 1, по фронту которого триггер 56, работающий в режиме делителя на 2, перейдет в состояние 1 по инверсному выходу, при этом на шине 11 появляется потенциал 1 сигнала Прерывание, по которому вычислительная система организует передачу нового файла данных. Триггеры 55 и 56 формируют сигнал Прерывание, причем в режиме От ВО этот.сигнал выдается при заполнении памяти до значения М и более ячеек блока 3 памяти а в режиме На ВО указанный сигнал

зации и поступает он с выхода элемента И-ИЛИ 53 также и на вход прямого счета счетчика 47 (объема за- полнения памяти), что увеличивает его содержимое на единицу. Уменьшение содержимого счетчика 47 происходит при считывании из блока 3 памяти. Для контроля обращения к памяти выходы Перенос и Заем счетчика 47 подключены посредством элемента И-ИЛИ 52 к шине 10 устройства. Разрешение на выдачу сигнала контроля формирует триггер 58, который уста- иавливается в положение I по пер вому импульсу занесения в память.

В режиме От ВО, когда содержимое реверсивного счетчика 47 станет равным М,, на выходе дешифратора 60 установится потенциал 1, по фронту которого триггер 55 перейдет в состояние 1, Потенциал 1 посредством элемента И-ИЛИ 51 будет установлен на шине 11 Прерьгоание, После поступления сигнала Прерывание вычислительная система переходит к подпрограмме записи/считьгаания на внешнюю память файла данных,

В режиме На ВО содержимое реверсивного счетчика 47 увеличивается при поступлении данных: от вычислительной системы. Когда содержимое счетчика станет равным М, на выход дешифратора 61 формируется потенциал 1, по фронту установления которого триггер 56 переходит в состояние О. При этом триггер 57. устанавливается в состояние 1, которое по шине 9 поступает к внешнему абоненту в качестве сигнала Пус объекта. От внешнего абонента начи нают поступать запросы на байты данных, содержимое счетчика 47 уменьшается ( фи. 66 и, когда достигает

формируется при уменьшении заполненного объема памяти до М и менее. Значения М и М выбираются в зависимости от общего объема памяти блока 3, скорости цифровых потоков внешнего абонента и внешней памяти, времени реакции вычислительной системы на Прерывание и от объема файла данных единичного объема между оперативной и внешней памя- тью.

в то же время содержимое счетчика 47 используется для организации второго режима управления обменом - программное управление со стороны вычислительной системы.

При передаче данных к оператив- ной памяти 104 (вычислительная система проводит при этом операцию чте- ния внешней памяти) файл данных

организован таким образом, что первый байт содержит код Д, второй байт - код К, код числа байт в файле, третий и четвертый байты отводятся под содержимое счетчика 47,- затем идут информационные, байты обмена или файл заканчивается.

При прохождении по второй группе информационных входов устройства 102 кода Д на выходе дешифратора 34 формируется сигнал 1, который стробируется предварительно задержанным в элементе 65 импульсом с выхода одновибратора 41 (соответствующим переднему фронту сигнала сопровождения данных устройств 107 Инф, А) и переводит триггер 67 в состояние 1 Фиксация кода Д (фиг 5, поз. 85, 87, 88). Это приводит к тому, что на выходе элемента И-ИЛИ 79 импульс Передний фронт сигнала Байт воспринят (П.Ф.Воспр.) соответствует импульсу переднего фронта сигнала Инф.К, формируемому одновибратором 43, Причем на выходе элемента И-ИЛИ 80 импульс Передний фронт сигнала Байт послан (П,Ф,Посл,) соответствует импульсу переднего фронта сигнала Инф. А, формируемому одновибратором 41, при этом на выходе элемента И-ИЛИ 81 импульс Задний фронт послан (З.Ф.Посл.) соответствует импульсу заднего фронта сигнала Инф. А, формируемому одновибратором 42J а на выходе элемента И-ИЛИ 82 импульс Задний фронт воспринят (З.Ф.Воспр.) соответствует импульсу заднего фронта сигнала Инф. К, формируемому одновнбрато- ром 44, Кроме того, фиксация кода Д разрета:ет сигналу П.В.Боспр. с выхода элемента И 78 поступить на единичный вход тригг ера 37, | на выходе которого разрешает сигналу З.Ф.Посл. с выхода элемента 38 И поступить на счетный вход счетчика 71 (фиг. 5, поз. 85, 88, 90), при этом на выходе первого разряда счетчика 71 устанавливается потенциал 1, который с вьпсода элемента И 75 подается (как сигнал Маска кода К) на элемент И-ИЛИ 83 и узел 32 элементов И-ИЛИ, на первую входную шину которого поступает в это время код второго байта файла. Этот код будет подведен к входу предварительной записи двоичного счетчика 36 и занесен в счетчик 36 по сигналу Загрузка К, который является предварительно задержанным сигналом П.Ф,Поел., поступающим с выхода элемента И-ИЛИ 83 (фиг. 5, поз. 85, 92, 100).

Содержимое счетчика 36 уменьшается на единицу и приходом с выхода элемента И 77 каждого импульса сигнал З.Ф.Посл. (фиг, 5, поз. 85, 100).

С приходом К-го (после загрузки счетчика) импульса счета содержимое счетчика 36 станет равным О и на его выходе Перенос появится сигнал 1 По переходу О, 1 одновибратор 45 формирует импульс Конец файла, кот орый устанавливает . в исходное состояние счетчик 71 и триггеры 67- 70, приводя тем самым устройство 102 в исходное состояние ожидания управления от вычислительной системы 101.

Но прежде чем это произойдет, второй импульс З.Ф.Посл, поступает на вход счетчика 71 и устанавливает на выходе его второго разряда 1 (фиг. 5, поз. 90, 91), Этот потенцигш подается на первый вход элемента И 76 и разрешает импульсу З.Ф.Воспр. с выхода элемента 82 установить триггер 70 в единичное состояние. Сигнал Подмена с выхода триггера 70 поступает на первый инверсный вход узла 30 элементов И-ИЛИ и прекращает режш4 транзитной передачи данных по входной 2 интерфейсной шине канала 106. Одновременно с этим потенциал 1 с вы2510908,

хода второго разряда счетчика 71 поступает (как сигнал Маска М) на девятые и восьмые входы узла 30 и подключает четвертую группу входов 5 узла 5 коммутации к группе входов узла 29, что позволяет передать в оперативную память 106 вычислительной системы Г01 код объема заполнения блока 3 памяти. Сначала переда10 ется содержимое младших восьми, разрядов, а затем старших восьми разрядов кода счетчика 47. При этом младшие разряды подведены к второй группе входов узла 30 элементов И-ИЛИ и

15 выбираются при 1 на вькоде первого разряда счетчика 71, а старшие разряды счетчика 47 подведены к первой группе входов узла 30 и выбираются при О на выходе первого разряда

20 счетчика 71 (в присутствии сигнала Маска М).

Для фиксации содержимого счетчика 47 сигнал Загрузка М с первого выхода узла 46 выбора режима по25 дается на вход занесения в ре- гистр 62.

С приходом пятого импульса 3,Ф. Поел. на обоих разрядах счетчика 71 устанавливается О и импульс

З.Ф.Воспр. с выхода элемента 82 получает возможность пройти элемент И 74 и установить триггер 64 в единичное состояние, а триггер 37 в нулевое положение (фиг. 5, поз. 90,

5 91, 94 и 89). После этого прекращается поступление счетных импульсов на счетчик 71, а сигнал Обмен с выхода триггера 69 подключает к второй группе информационных выходов уст0 ройства выход блока 3 памяти (посредством узла 30 элементов И-ИЛИ и узла 29 шинных формирователей). Кроме того, сигнал П.ф.Воспр. получает возможность пройти элемент 39

5 (фиг, 5, поз, 98) и поступить в/ качестве сигнала Запрос ЕС на третий вход элемента 54, с выхода которого этот импульс поступает на вычитаняций вход счетчика 47 (объема

0 заполнения памяти) и по шине 20 - на вход Запрос чтения блока 3 памяти. По этому запросу на шине 14 блок 3 памяти выставляет очередной байт данных для последующей переда5 чи к вычислительной системе. Так, в режиме От ВО осуществляется доступ внешнего абонента 103 к оперативной памяти 104.

9

Для реализации доступа внеганего абонента 103 к внешней памяти 105 в режиме От ВО по первой группе информационных входов устройства 102 должен поступить код С. Па вы- ходе дешифратора 35 появляется потенциал 1, который позволяет импульсу с выхода элемента 66 задержки установить триггер 68 фиксации кода С в единичное состояние. При этом сигнал П.ФвВоспр, на выходе элемента И-ИЛИ 79 является сигналом З.Ф.Инф, А с выхода одновибратора 42, сигнал П.Ф,Поел, на выходе элемента И-ИЛИ 80 - сигналом П.Ф, Инф, к с выхода одновибратора 43, сигнал З.Ф.Посл, - сигналом З.Ф. Инф. К с выхода одновибратора 44, сигнал З.Ф.Воспр. - сигналом П.Ф. Инф. А - с выхода одновибратора 41.

, Загрузка кода числа байт обмена происходит аналогично указанному, только код этот поступает с второй группы входов узла 32 элементов И-ИЛИ. Кроме того, содержимое счет- чика 47 не выдается на вторую группу информационных выходов устройства 102, так как в данном случае происходит подмена данных в файле, идущем по выходной 1 интерфейсной ши- не канала 106 к устройству 107, и, следовательно, данные на входной

2интерфейсной шине канала 106 им не воспринимаются. Когда появляется сигнал Обмен ;(триггер 69 установ- лен в единичное состояние, как описано выше), то к первой группе информационных выходов устройства 102 при помощи узлов 50, 33 и 27 подключается шина 14 группы выходов блока

3памяти и каждый байт, поступающий от канала 106 к устройству 107, заменяется на байт, введенный в блок 3 памяти внешним абонентом 103. Так внешний абонент записывает свои дан- вые во внешнюю память вычислительной системы rOl.

При передаче данных от вычислительной системы 101 внешнему абоненту 103 (режим На ВО) на шине 6 ре жима удерживается потенциал О. Данные вводятся в блок 3 памяти (фиг. 7) либо из оперативной памяти 104 (при поступлении кода С на пер- }зую группу информационных входов устройства 102, когда вычислитель- мая система проводит операцию записи файла данных на внешнюю памятьJ

5 О 5 20

25 ЗО

,, 40

45

5055

25109010

либо от внешней памяти 106 (при поступлении кода Д на вторую группу информационных входов устройства 102, при этом вычислительная систе- . ма организует операцию чтения файла данных внеш гей памяти). Затем по запросам внешнего абонента на шине 8 данные из блока 3 памяти выводятся внешнему абоненту по шине 13. Последовательность прохождения управляющих и переключающих сигналов организуется, как это показано вьште для режима От ВО и доступа к оперативной или внешней памяти, и прослеживается при помощи схемы на фиг. 7 и временных диаграмм (фиг. 5). Гипотетический переключатель 108 ото- бражает функции узла 31 элементов И-ИЛИ, его контакты (1-2) замкнуты при фиксации кода С, а контакты (1-3) замкнуты при фиксации кода Д. Переключатель 109 в положении замкнутых контактов (1-2) соответствует , состоянию узла 33 элементов И-ИЛИ при фиксации кода С, а в положении замкнутых контактов (1-3) - узлу 30 при фиксации кода Д. Переключатель ПО отображает функции узла 48 - контакты (1-2) замкнуты в режиме На ВО, что соответствует подключению к выходу узла 48 его второй группы входовJ контакты (2-3)замкнуты н режиме От ВО, это соответствует подключению к выходу узла 48 первой группы его входов, узла 49 - активного в режиме На ВО и соответствующего замкнутым контактам (4-5}, и . узла 50 - активного в режиме От ВО и соответствующего замкнутым контак- , там (5-6).

Формула изобретения

Устройство для обмена данными в вычислительной системе, содержащее блок коммутации, блок памяти и блок передачи данных и управления, причем первая группа информационных входов блока коммутации подключена к группе информационных выходов канала ввода - вывода вычислительной систе мы, первая группа информационных выходов блока коммутации подключена к группе информационных входов внешней памяти вычислительной системы, вторая группа информационных входов блока коммутации подключена к группе информационных выходов внешней

11

naMfjtH вычислительной системы, первые группы информационных входов и выходов блока передачи данных и управления подключены к группам информационных выходов и входов внешне- .го абонента соответственно, выход прерывания блока передачи данных и / управления подключен к входу прерывания вычислительной системы, входы режима работы и синхронизации блока передачи данных и управления подключены к выходам режима работы и синхронизации внешнего абонента соответственно, выходы синхронизации и режима контроля работы блока передачи данных и управления подключены к входам синхронизации и контроля режима, работы внешнего абонента соответственно, при этом первый выход блока коммутации сое- . динен с входом увеличения счета байтов блока передачи данных и управления, выход сброса которого соединен с установочным входом блока коммутации, выход записи блока передачи данных и управления соединен с входом записи блока памяти, группы информационных входов и выходов которого соединены с вторыми группами информационных выходов и входов блока передачи данных и управления соответственно, третья группа информационных выходов которого соединена с третьей группой информационных входов блока коммутации, при этом блок коммутации содержит три

узла шинных формирователей, пять од- новибраторов, два дешифратора, первый узел элементов И-ИЛИ, три элемента И, триггер, счетчик,причем группы информационных входов первого шинного формирователя и информационных выходов второго шинного формирователя образуют первые группы информационных входов и выходов блока коммутации, группа информационных входов третьего шинного формирователя образует вторую группу информационных входов блока коммутации, первая группа входов первого узла элементов И-ИЛИ образует третью групу информационных входов блока коммутации, первьй нулевой вход триггера соединен с входом сброса счетчика и является установочньм входом блока коммутации, выход первого элемента И является первым выходом бло- ка коммутации, при этом в блоке комутации группа информационных выхо

251090 2

дов первого узла шинных формирователей соединена с группой входов первого дешифратора и второй группой входов первого узла элементов И-ИЛИ, S причем блок передачи данных и управления содержит реверсивный счетчик, два дешифратора; узел формирования сигнала сброса, три триггера, элемент И, три элемента И-ИЛИ, узел элемен- 10 тов И-ИЛИ, два узла элементов И, при этом первая группа прямых входов, узла элементов И-ИЛИ образует первую группу информационных входов блока передачи данных и управления, t5 группа выходов первого узла элементов И образует первую группу информационных выходов блока передачи данных и управления, группа входов пер-, вого узла элементов И соединена с 20 первой группой входов второго узла элеме нтов И и образует вторую группу информационных входов блока передачи данных и управления, группа выходов узла элементов И-ИЛИ образует

25 вторую группу информационньк выходов блока передачи данных и управления, группа выходов второго узла элементов И образует третью группу инфор-. мационных входов блока передачи дан30 ных и управления, инверсный вход элемента И соединен с инверсным и первым входами первого элемента И-ИЛИ, с управляющим входом первого дешифратора, с инверсным управляющим входом

jr второго дегшфратора, с группой инверсных входов первого узла элементов И, с второй группой входов второго узла элементов И, с прямым и ин- версным входами узла элементов И-ИЛИ,

4Q с первым прямым и инверсным входами узла элементов И-ШШ, с первым пря- мьтм и инверсным входами второго элемента И-ИЛИ и является -входом режима работы блока передачи данных и управ 5 ления, второй вход второго элемента И-ШШ является входом синхронизации блока передачи данных и управления,, третий вход второго элемента И-ИЛИ является входом увеличения счета бай

50 тов блока передачи данных и управления, выход узла формирования сигнала сброса соединен с нулевыми входами реверсивного счетчика, первого, второТо, третьего триггеров и яв55 ляется выходом сброса блока переда- чи данных и управления, выход первого триггера является выходом синхронизации блока передачи данных и

управления5 выкод третьег о элемента И-ЙЛИ 55впяется выходом контроля режима работы блока передачи данных и управления, выход первого элемента И-ИЛИ является выходом прерьшанйк блока передачи данных и управления, выход второго элемента И-ЙШ1 соединен с входом увелтлчения счета реверсивного счетчика и является выходом записи ®лока передачи и управ лениЯв гфи этом в блоке передачи даннызс я управления группа информа- ционньк выходов реверсивного счетчика соединена с группами информационных входов первого и второго дешифраторов,, выход второго дешиф ратора соединен с синхровходом второго триггера и входом элемента и, выход которого соединен с едикичньм входом первого триггера, выход пер- вого дешифратора соединен с синхро- входом третьего триггераj нулевой выход которого соединен с инфор ма- циоиньп входом третьего триггера единичный выход которого соединен с вторым входом, первого элемента И- ЙЛЙ,, третий вхад которого соединен к инфоркадионньйч входом н нулевым аы ходом второго триггераJ, о т л н - чащщреся TeKj что,, с целью расширения функциональгшх возможностей за счет обеспечения доступа к внежней ггамяти вычислигелькой -системьзз в блок коммутации введены четвертый узел шинных формщэонапглей,, три узла элементов И-ШШ; узел бора а в блок передачи дай- нык и управления введены регистрg четварть й триггер., четвертый элемент ., узел формирования сигнала разреагекия 5 причем вторая группа информационных входов блока комьтута™ цин подключена к группа информациок- 1ых выходов канала ввода - вывода вьгеислительной cHCTeMiiij командт-гый вход блока ггередачи данньк и управления подключен к выходу запросов внешнего-абонентаэ при этом треть; к четвертая групгш информатдаонт-щ входов блока передачи данных и уира лекия соединены с третьей группой информационных выходов и четвертой группой информационных входов блока ко мутапу.и соответственно9 З жорой вьжод которого соединен с входет уменьшения счета блока передачи дан- ньш и управления3 вход загшеи которого соединен с третьи вьжодом бло

25

5 JO 1 S хО зз

5109014

ка коммутации.; вход разрешения установки режима которого соединен с выходом разрешения блока передачи данных и управления, выход чтения ко- 5 торого соединен с входом чтения блока памяти5 при этом группа выходов четвертого узла шинных формирователей образует вторую группу информационных выходов блока коммутации, группа выходов второго узла элементов И-ИЛИ образует третью группу информационных входов блока коммутации, первая и вторая группы входов третьего узла элементов И-ИЛИ образуют четвертую группу информационных входов блока коммутации первый :8ход узла выбора режима является вхо дом разрешения установки р ежима блока коммутации-, первый выход узла выбора режима соединен с входом записи йчетчика и является третьим выходом блока ког -гутации, выход второго эле-- мента И является вторым EL-ХОДОМ бло-. ка ком гутации при этом ь блоке ко«ч - му г.зции выходы сопровождения данных первого узла шинных формирователей соединены с входами первого и вто- pofo одновибраторовэ- выходы которых соединены с вторым и третьим входом узла выбора ре;кима соответственноj четвертый и пятый входы которого сое,динены с выходами третьего и четвертого одновибраторов соответствен HOj входы которых соединены с выходом сопровождения данных третьего узла шинных формирователей;, группа информационных выходов которых соединена с третьей группой входов третьего узла элементов И-ЙЛИ, с первыми группами входов второго и четвертого узлов элементов И-ИЛИ и группой входов второго дешифратора;, выход которого соединен с шестым входом узла выбора режима; седьмой вход которого соединен с выходом первого де- кфраторе..) восьмой вход узла Б:;5бор.з режима соединен с вькодом пятого од новибраторае вход которого соединен с выходом переноса счетчика, нулевой зхсд которого соединен с давлтым входом узла выбора режима, десятый вход которого соед1-шен с выходом третьего .йламента И, первый ЕКОД котс рого соединен с вторым выходом узла выбора иежима, третий к четвертый выходы которого соединаны с е,а ;«кчгл::,ы и нто- рык нулевым входами трмггзра соответ- CTBGHHCj вькход которого еоеднкан с

30

40

вторым входом третьего элемента И, пятый выход узла выбора режима соеднен с входом уменьшения счета счетчка, группа информационных входов которого соединена с группой выходов четвертого узла элементов И-ИЛИ, втрая группа входов которого соединена с вторыми группами входов первго и второго узлов элементов И-ИЛИ, первый и второй входы второго узла элементов И-ИЛИ соединены с шестым выходом узла выбора режима, первыми входами первого и второго элементов ;И, первым входом третьего узла эле- ментов И-ИЛИ, первым прямым и инвер ным входами первого узла элементов И-ИЛИ, второй прямой вход которого соединен с третьим входом второго узла элементов И-ИЛИ, с первьЫ входом четвертого узла элементов И-ИЛИ и седьмым выходом узла выбора режима, восьмой выход которого соединен с вторым и третьим входами четверто- го узла элементов И-ИЛИ, четвертый вход которого соединен с вторым, третьим, четвертым входами третьего узла элементов И-ИЛИ, с четвертым входом второго узла элементов И-ИЛИ и девятым выходом узла выбора режима, десятый выход которого соединен с первым инверсным входом третьего .узла элементов И-ИЛИ, пятый и шестой входы которого соединены с одиннадцатым выходом узла выбора режима, :двенадцатый выход которого соединен с седьмым и вторым инверсным входа ми третьего узла элементов И-ИЛИ, тринадцатый и четырнадцатый выходы узла выбора режима соединены с вторыми входами первого и второго элементов И соответственно, при этом вход записи регистра является-входом записи блока передачи данных и управления , группа выходов регистра образует четвертую группу информационных -выходов блока передачи данных и управления, первый и второй входы четвертого элемента И-ИЛИ являются входом уменьшения счета и командным входом блока управления соответственно, вторая группа входов узла элемента И-ИЛИ образует третью группу информационных входов блока передачи данных и управления, выход четвертого элемента И-ИЛИ соединен с входом уменьшения счета реверсивного счетчика и является выходом чтения блока передачи данных и

10

15

го

5

0

5

0

5

0

5

управления, выход узла формирова ния сигнала разрешения соединен с четвертым входом второго элемента И-ИШ1. третьим входом четвертого элемента И-Ш1И и является выходом разрешения блока передачи данных и управления, причем в блоке передачи данных и управления группа информационных входов регистра соединена с группами информационных входов первого и второго дешифраторов и группой информационных выходов реверсивного счетчика, выходы переноса, и заема которого соединены с первым и вторым входами третьего элемента И-ИЛИ соответственно, третий и четвертый входы которого соединены с выходом четвертого триггера, нулевой вход которого соединен с входами сброса регистра и реверсивного счетчика, вход увеличения счета которого соединен с единичным входом четвертого триггера, четвертый и инверсный входы четвертого элемента И-ИЛИ соединены с первым входом второго элемента И-ИЛИ, при этом узел выбора режима .содержит счетчик, четьфе триггера, два элемента задержки, пять элементов И-ИЛИ, элемент ИЛИ, семь элементов И, при этом первые входы первого и второго элементов И являются первым входом узла выбора режима, вход первого элемента задержки соединен с первыми входами первого и второго элементов И-РШИ и является вторым входом узла выбора режима, первые входы третьего и четвертого элементов И-ИЛИ являют- ся третьим входом узла выбора режима, вторые входы первогю и третьего элементов И-ИЛИ являются четвертым входом узла выбора режима, вход второго элемента задержки соединен с вторыми входами второго и четвертого элементов И-ИЛИ и является пятым входом узла выбора режима, второй вход первого элемента И является шестым входом узла выбора режима, второй вход второго элемента И является седьмым входом узла выбора режима, первый нулевой вход счетчика соединен с первыми нулевыми входами первого, второго, третьего, четвертого триггеров и является восьмым входом узла выбора режима, второй нулевой вход счетчика соединен с вторыми нулевыми входами первого, второго, третьего четвертого триггеров и явля

ется девятым входом узла выбора режима, счетный вход счетчика является десятым входом узла выбора режима, выход пятого элемента И-ИЛИ является первым выходом узла выбора режима выход третьего элемента И-ИЛИ соединен с первым входом шестого элемента И и является вторым выходом узла выбора режима, выход седьмого элемента И является третьим выходом узла выбора режима, выход третьего элемента И соединен с едииичным вхо дом первого триггера и является чет- вер тым выход ом узла выбора режима, выход шестого элемента И является пятым выходом узла выбора режима, выход первого триггера является шестым выходом узла выбора режима, единич-- ный выход второго триггера соединен ,с первым входом пятого элемента И-ИЛИ первым входом элемента ИЛИ, третьими входами первого, второго, третьего, 4eTBeptoro элементов И-ИЛИ и является седьмым выходом узла выбора режима, выход четвертого элемента И соединен с вторым и третьим входами пятого элемента И-ИЛИ и является восьмым выходом узла выбора режима, единичный выход третьего триггера соединен с четвертым входом пятого элемента Н-ИЛИ вторым вхо- дом элемента ИЛИ, четвертыми входами первого, второго, третьего, иетвер- того элементов И-ШШ и является де- ёйтйм вь ходом узла выбора режима, выход четвертого триггера является десятым выходом узла выбора режима.

ггёрвый выход счетчика соединен с первым инверсным входом третьего элемента И, инверсным входом четверто,- го элемента И, первым входом пятого элемента И и является одиннадцатым выходом узла выбора режима, второй ВЫХОД счетчика соединен с входом четвертого элемента И, вторым инверсным входом третьего элемента И и является двенадцатым выходом узла выбора режима, выход второго элемента И-ИЛИ является тринадцатым выходом узла выбора режима, выход пер- - вого элемента И-ИЛИ соединен с первым входом седьмого элемента И и является четырнадцатым выходом узла выбора режима, причем в узле выбора режима выход первого элемента задержки соединен с пятым входом пятого элемента И-ИЛИ и третьим входом второго элемента И, выход которого соединен с единичным выходом второго триггера, нулевой выход ко- .Торого соединен с третьим входом nepTtaro элемента И, четвертый вход iкоторого соединен с выходом второго элемента задержки и шестым входом пятого элемента И-ИЛИ, выход первого элемента И соединен с единичным входом третьего триггера, нулевой вход которого соединен с четвертым входом второго элемента И, выход элемента ИЛИ соединен с вторыми входами шестого и седьмого элементов И,выход четвертого элемента И-ИЛИ соединен с входом третьего элемента И и вторым входом пятого элемента И.

434/ «г

m

30

32

лг; jr.1,1 I,

J-L

и

si

R

&

fH AU

Й 2

46

.in I

Л- V

я

LU

IJsf- ll I I

M tn rh

pa

a

35

J

:t3

51

л.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1084776A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Система коммутации вычислительных устройств,устройство коммутации связи и устройство сопряжения | 1984 |

|

SU1180915A1 |

| УСТРОЙСТВО ДЛЯ КОММУТАЦИИ ПАКЕТОВ ИНФОРМАЦИИ | 1994 |

|

RU2075778C1 |

| Устройство для обработки статистических данных о работе аппаратуры вычислительных машин и систем | 1982 |

|

SU1086439A1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Системный коммутатор с приоритетным обслуживанием | 1986 |

|

SU1444799A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах автоматизации научных исследований. Изобретение позволяет вычислительной системе оперативно изменять устройства, участвующие в обмене с внешннм абонентом, а именно: данные от внешнего абонента могут подаваться либо на внешнюю память, либо .на оперативнзгю память; данные поступают внешнему абоненту либо от внешней, либо оперативной памяти Bk- числительной системы в зависимости от кода, выставляемого вычислительной системой на инфо1 ационные входы данного устройства. Устройство содержит блок коммутации, блок управления и блок памяти 7 ил. Од СЛ

fl5«e3

ооооо

N )

S§ ь, 4s

«)

to N OQ O) bi Sj

) Cs OS C

Редактор М.Дыпын

фив.7

Составитель Л.Пйстмал

Техред И.Гайдош Корректор В. Бутяга

Заказ 4412/46

Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое прадприятиа, г. Ужгород, ул. Проектная, 4

Подписное

| Устройство для сопряжения | 1980 |

|

SU888098A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией | 1982 |

|

SU1084776A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1984-12-30—Подача