(54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНОДЕСЯТИЧНБ1Х ЧИСЕЛ В ДВОИЧНЫЕ

исходного двоично-десятичного числа на число 1010 и в передаче полученного результата от входа к выходу вспомогательного п-разрядного сдвигового регистра. При этом п тактов тратится на ввод двоично-десятичного числа в устройство.

Наиболее близким техническим решением к предлагаемому является устройство для преобразования двоично-десятичных чисел в двоичные, содержащее распределитель, информационный вход которого соединен с .первой управляющей шиной устройства, установочный вход - с шиной сброса устройства и нулевым входом триггера, единичный вход которого подключен к выходу первого элемента И, а единичный выход - к первому входу второго элемента И и через первый элемент НЕ к первому входу третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к выходной шине устройства, а второй вход - к выходу сумматора и входу элемента задержки, выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу второго элемента И, при этом разрядные выходы распределителя с первого по четвертый соединены со входами второго элемента ИЛИ, выход которого подключен к первому входу четвертого элемента И, разрядные выходы распределителя с пятого по восьмой соединены со входами третьего элемента ИЛИ, выход-которого подключен к первому входу пятого элемента И, разрядные выходы распределителя с девятого по двенадцатый соединены со входами четвертого элемента ИЛИ, выход которого подключен к первому входу шестого элемента И, разрядные выходы распределителя с тринадцатого по пятнадцатый соединены со входами пятого элемента ИЛИ, выход которого подключен к первому входу седьмого элемента И, шестнадцатый разрядный выход распределителя соединен с первым входом первого элемента И, второй вход которого подключен ко входной информационной шине устройства и ко вторым входам четвертого, пятого, шестого и седьмого элементов И, а также восьмой элемент И, первый вход которого соединен со второй управляющей шиной устройства и через второй элемент НЕ с первым входом девятого элемента И 3.

К недостаткам известного устройства относится низкое быстродействие, так как для преобразования двоично-десятичных чисел в двоичные требуется не менее 5п тактов. Это вызвано тем, что для формирования п-разрядного результата требуется п циклов, а каждый цикл состоит из сдвига (умножение на два) двоично-десятичного числа и корректирующего шага. Корректирующий щаг определяют те т.трады, для которых имеет место условие 4-2. , где М -двоичная цифра (О или 1), а р - номер двоичного разряда двоично-десятичной тетрады. В случае, когда удовлетворяется это условие, корректирующий шаг заключается в посылке корректирующего кода ООП на сум матор, где осуществляется сложение содержимого этих тетрад с кодом, коррекции. Это компенсирует ощибку, образующуюся в результате последующего едвига двоично-десятичного числа. Здесь, как и в выше рассмотренных случаях, п тактов тратится на ввод двоично-десятичного числа в устройство.

Цель изобретения - повышение быстродействия устройства для преобразования двоично-десятичных чисел в двоичные.

Указанная цель достигается за счет того, что в устройстве для преобразования двоично-десятичных чисел в двоичные, содержашем распределитель, информационный вход которого соединен с первой управляющей шиной устройства, установочный входс шиной сброса устройства и нулевым входом триггера, единичный вход которого подключен к выходу первого элемента И, а единичный выход - к первому входу второго элемента И и через первый элемент НЕ - к первому входу третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к выходной шине устройства, а второй вход - к выходу сумматора и входу элемента задержки, выход которого соединен с первым входом сумматора, второй вход которого

0 подключен к выходу второго элемента И, при этом разрядные выходы распределителя с первого по четвертый соединены со входами второго элемента ИЛИ, выход которого подключен к первому входу четвертого элемента И, разрядные выходы распределителя

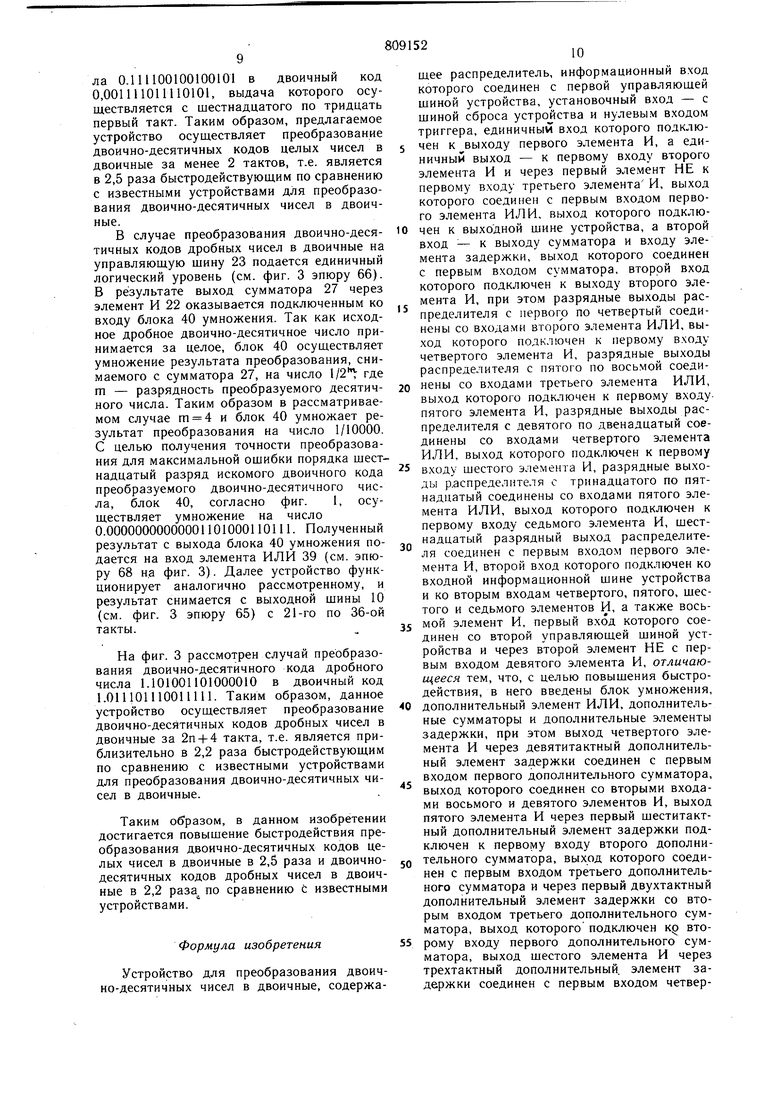

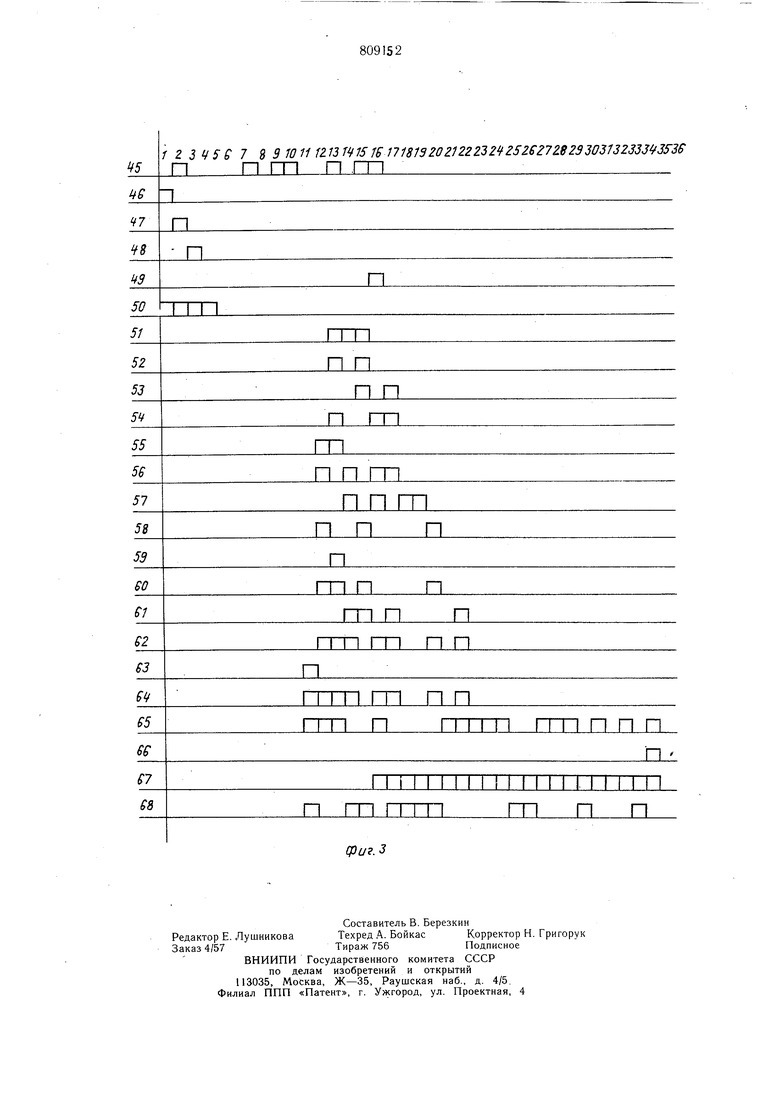

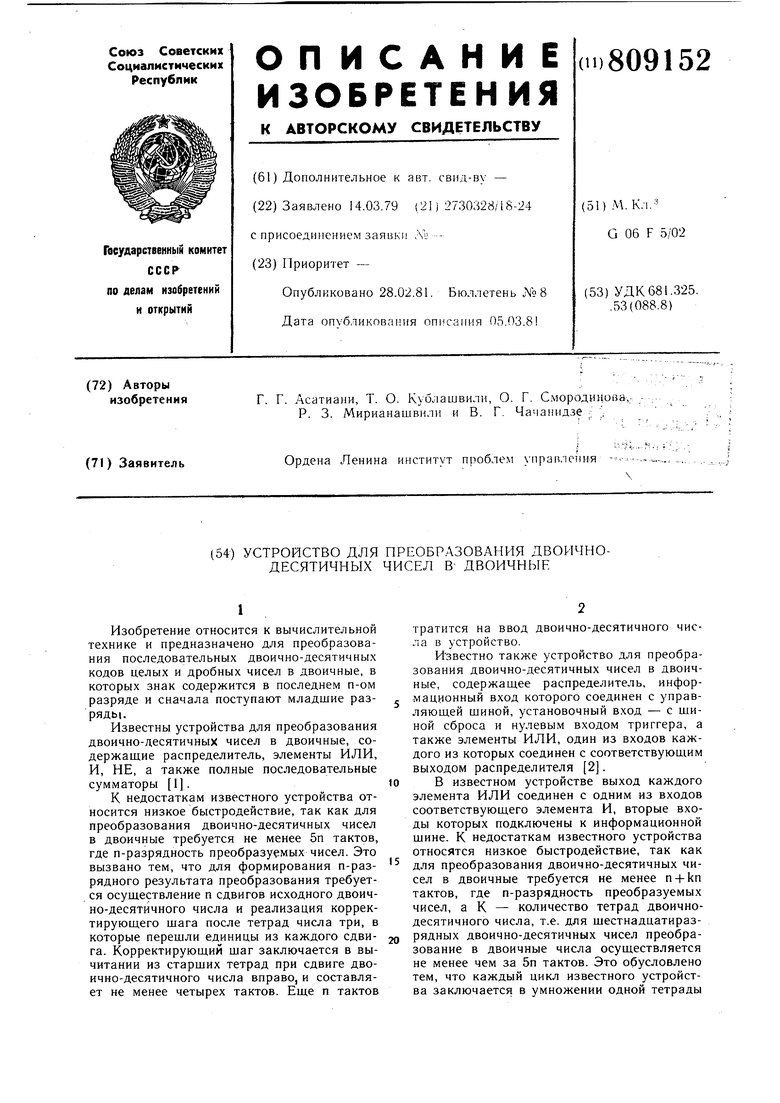

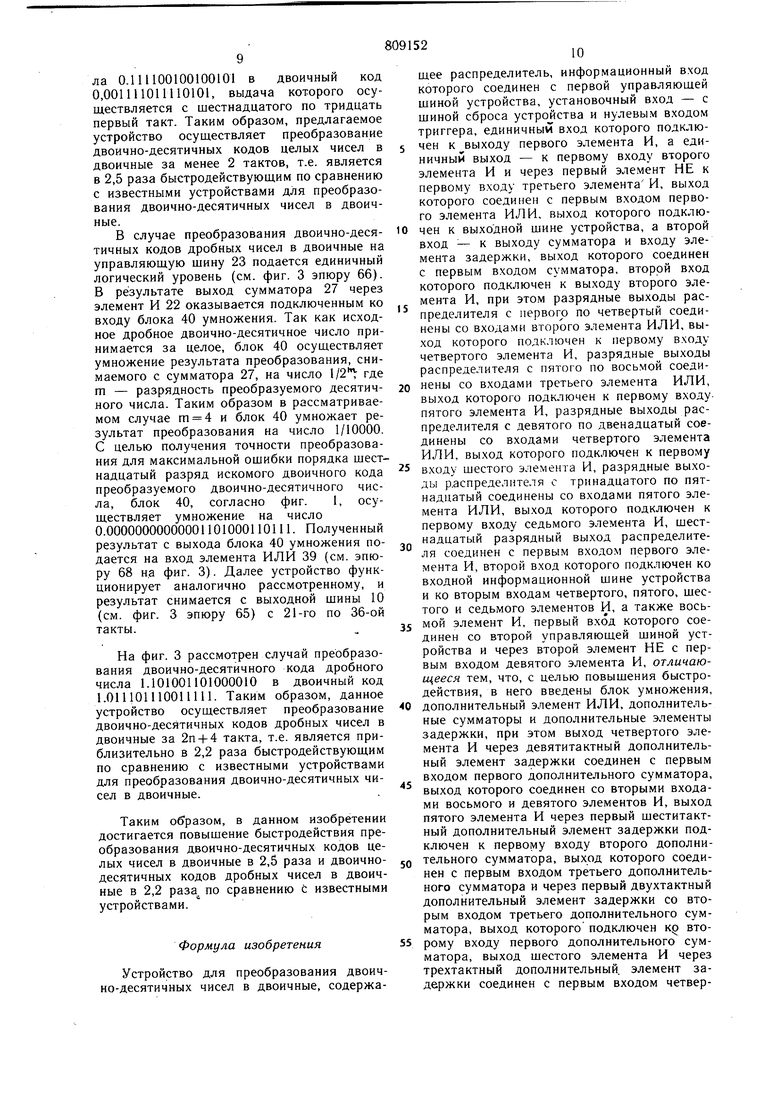

5 с пятого по восьмой соединены со входами третьего элемента ИЛИ, выход которого подключен к первому входу пятого элемента И, разрядные выходы распределителя с девятого по двенадцатый соединены со входами четвертого элемента ИЛИ, выход которого подключен к первому входу шестого элемента И, разрядные выходы распределители с тринадцатого по пятнадцатый соединены со входами пятого элемента ИЛИ, выход которого подключен к первому входу седьмого элемента И, шестнадцатый разрядный выход распределителя соединен с первым входом первого элемента И, второй вход которого подключен ко входной информационной шине устройства и ко вторым входам четвертого, пятого, шестого и седьмого элементов И, а также восьмой элемент И, первый вход которого соединен со второй управляющей шиной устройства и через второй элемент НЕ с первым входом девятого элемента И, введены блок умножения, дополнительный элемент ИЛИ, дополнительные сумматоры и дополнительные элементы задержки, при этом выход четвертого элемента И через девятитактный дополнительный элемент задержки соединен с первым входом первого дополнительного сумматора, выход которого соединен со вторыми входами восьмого и девятого элементов И, выход пятого элемента И через первый шеститактный д ополнительный элеме,чт задержки подключен к первому входу второго дополнительного сумматора, выход которого соединен с первым входом третьего дополнительного сумматора и через первый двухтактный дополнительный элемент задержки со вторым входом третьего дополнительного сумматора, выход которого подключен ко второму входу первого дополнительного сумматора, выход шестого элемента И через трехтактный допол нительный элемент задержки соединен с первым входом четвертого дополнительного сумматора, вь1ход которого подключен к первому входу пятого дополнительного сумматора и через второй двухтактный дополнительный элемент задержки ко второму входу пятого дополнительного сумматора, выход которого соединен со вторым входом второго дополнительного сумматора, выход седьмого элемента И соединен с первым входом шестого дополнительного сумматора и через третий двухтактный дополнительный элемент задержки со вторым входом шестого дополнительного сумматора, выход которого подключен ко второму входу четвертого дополнительного сумматора, выход девятого элемента И через второй шеститактный дополнительный элемент задержки подключен к первому входу дополнительного элемента ИЛИ, второй вход которого через блок умножения соединен с выходом восьмого элемента И при этом выход дополнительного элемента ИЛИ подключен ко вторым входам .второго и третьего элементов И. На фиг. 1 представлена функциональная схема устройства для преобразования двоично-десятичных чисел в двоичные; на фиг. 2 и 3 - временные диаграммы. Устройство содержит распределитель 1, информационный вход которого соединен с первой управляющей шиной 2, установочный вход - с шиной 3 сброса и нулевым входом триггера 4, единичный вход которого подключен к выходу первого элемента И 5; а единичный выход - к первому входу второго элемента И 6 и через первый элемент НЕ 7 к первому входу третьего элемента И 8, выход которого соединен с первым входом первого элемента ИЛИ 9, выход которого подключен к выходной шине 10, а второй вход - к выходу сумматора 11 и входу элемента 12 задержки, выход которого соединен с первым входом сумматора 11, второй вход которого подключен к выходу второго элемента И 6, разрядные выходы распределителя 1 с первого по четвертый соединены со входами второго элемента ИЛИ 13, выход которого подключен к первому входу четвертого элемента И 14, разрядные выходы распределителя 1 с пятого по восьмой соединены со входами третьего элемента ИЛИ 15, выход которого подключен к первому входу пятого элемента И 16, разрядные выходы распределителя 1 с девятого по двенадцатый соединены со входами четвертого элемента ИЛИ 17, выход которого подключен к первому входу шестого .элемента И 18, -разрядные выходы распределителя 1 с тринадцатого по пятнадцатый соединены со входами пятого элемента ИЛИ 19, выход которого подключен к первому входу седьмого элемента И 20, шестнадцатый разрядный выход распределитеЛЯ 1 соединен с первым входом первого эяемента И 5, второй вход которого подключен ко входной информационной шине 21 и ко вторым входам четвертого, пятого, шестого и седьмого элементов И 14, 16, 18 и 20, 22 - восьмой элемент И, первый вход которого соединен со второй управляюшей шиной 23 и через второй элемент НЕ 24 с первым входом девятого элемента И 25, выход четвертого элемента И 14 через девятитактный дополнительный элемент 26 задержки соединен с первым входом первого дополнительного сумматора 27, выход которого соединен со вторыми входами восьмого и девятого элементов И 22 и 25, выход пятого элемента И 16 через первый шеститактный дополнительный элемент 28 задержки подключен к первому входу второго дополнительного сумматора 29, выход которого соединен с первым входом третьего дополнительного сумматора 30 и через.первый двухтактный дополнительный элемент задержки 31 со вторым входом третьего дополнительного сумматора 30, выход которого подключен ко второму входу первого дополнительного сумматора 27 выход шестого элемента И 18 через трехтактный дополнительный элемент 32 задержки соединен с первым входом четвертого дополнительного сумматора 33, выход которого подключен к первому входу пятого дополнительного сумматора 34 и через второй двухтактный дополнительный элемент 35 задержки ко второму входу пятого дополнительного сумматора 34, выход которого соединен со вторым входом второго дополнительного сумматора 29, выход седьмого элемента И соединен с первым входом шестого дополнительного сумматора 36 и через третий двухтактный дополнительный элемент 37 задержки со вторым входом шестого дополнительного сумматора 33, выход девятого элемента И 25 через второй шеститактный дополнительный элемент 38 задержки подключен к первому входу дополнительного элемента ИЛИ 39, второй вход которого через блок 40 умножения соединен с выходом восьмого элемента И 22, выход дополнит- льного элемента ИЛИ 39 подключен ко вторым входам второго и третьего элементов И 6 и 8, 41 - сумматоры, 42 - однотактные элементы задержки, 43 - двухтактные элементы задержки, 44 - четыре.чтактный элемент задержки. На фиг. 2 и 3 представлены временные диаграммы функционирования устройства для преобразования двоично-десятичных чисел в двоичные, гд 45 - код двоично-десятичного числа, подаваемого на входную информационную шину 21; 46, 47, 48, 49 - соответственно логические уровни на первом, втором, третьем и п 16-ом разрядных выходах распределителя 1; 50-логическИе уровни на выходе элемента ИЛИ 13, 51-логические уровни на выходе элемента ИЛИ 19, 52 - логические уровни на выходе элемента И 20, 53 - логические уровни на выходе элемента 37 задержки, 54 - логические уровни на выходе сумматора 36, 55 - логические уровни на выходе элемента 32 задержки, 56 - логические уровни на выходе сумматора 33, 57 - логические уровни на выходе элемента 35 задержки, 58 - логические уровни на выходе сумматора 34, 59 - логические уровни на выходе элемента 28 задержки, 60 :- логические уровни на выходе сумматора 29, 61 - логические уровни на выходе элемента 31 задержки, 62 - логические уровни на выходе сумматора 30, 63 - логические уровни на выходе элемента 26 задержки, 64 - логические уровни на выходе сумматора 27, 65 - код результата, 66 - логические уровни на управляющей шине 23, 67 - логические уровни на выходе элемента И 5, 68 - логические уровни на выходе элемента ИЛИ 39. Функционирование устройства для преобразования двоично-десятичных чисел в двоичные для случая шестнадцатиразрядных чисел, в которых знак содержится в последнем разряде, осуществляется следующим образом. В исходном состоянии при помощи единичного логического уровня, подаваемого по шине сброса 3, триггер 4 и распределитель 1 устанавливаются в нулевое состояние. На первом такте на управляющую шину 2 подается импульс, который за 16 тактов в виде единичных логических уровней распределяется по разрядным выходам распределителя 1 (см. фиг. 2 и 3 эпюры 46-49). Начиная с первого такта на входную информационную щину 21 подается код двоичнодесятичного числа (см. фиг. 2 и 3 эпюру 45) начиная с младших разрядов. Единичный логический уровень с выхода элемента ИЛИ 13 (см. фиг. 2 и 3 эпюру 50) с первого по четвертый такты разблокирует элементы И 14, в результате чего в течение указанных тактов первая тетрада исходного двоично-десятичного числа подается на вход элемента задержки 26, который осуществляет задержку указанной тетрады на девять тактов (см. фиг. 2 и 3 эпюру 63). Аналогично, вторая тетрада исходного двоично-десятичного числа с пятого по восьмой такты подается на вход элемента 28 задержки, который осуществляет задержку этой тетрады на щесть тактов (см. эпюру 59). Аналогич52но, с девятого по двенадцатый такты на вход элемента 32 задержки подается третья тетрада исходного двоично-десятичногр числа, которая снимается с выхода указанного элемента задержки, задержанной на 3 такта (см. эпюру 55). Единичный логический уровень с выхода элемента ИЛИ 19 (см. эпюру 51) с тринадцатого по пятнадцатый такты, разблокирует элемент И 20 (см. эпюру 52) в результате чего с выхода элемента И 20 в течение указанных тактов снимается последняя (четвертая) неполная тетрада исходного двоично-десятичного числа. На элементе 37 задержки осуществляется задержка четвертой тетрады на два такта (см. эпюру 53). Вследствие этого на выходе сумматора 36 образуется результат умножения четвертой тетрады на 1010 (см. эпюру 54), который на су.мматоре 33 (см. эпюру 56) складывается с третьей тетрадой, подаваемой с элемента 32 задержки. Полученный результат при помощи элемента 35 задержки (см. эпюру 57) и сумматора 34 (см. эпюру 58) умножается на 1010 и на сумматоре 29 (см. эпюру 60) складывается со второй тетрадой, подаваемой с выхода элемента 28 задержки. Этот последний результат при помощи элемента 31 задержки (см. эпюру 61) и сумматора 30 (см. эпюру 62) также умножается на 1010 и на сумматоре 27 (см. эпюру 64) складывается с первой тетрадой, подаваемой с выхода элемента 26 задержки. JB случае преобразования двоично-десятичных кодов целых чисел снимаемый с выхода сумматора 27 двоичный код является результатом преобразования, который из-за наличия на управляющей щине 23 (см. фиг. 2 эпюру 66) нулевого логического уровня через элемент И 25 и элемент 38 задержки подается на вход элемента ИЛИ 38. На шестнадцатом такте с выхода элемента И 5 снимается логический уровень, соответствующий знаку преобразуемого двоично-десятичного числа (см. эпюру 67), который фиксируется в триггере 4. Если исходное двоично-десятичное гчисло отрицательно, т.е. триггер 4 находится в единично.м состоянии, элемент И 6 разблокирован и результат преобразования с выхода элемента ИЛИ 39 подается на вход сумматора 11. Этот последний в совокупности с элементом 12 задержки переводит результат преобразования в дополнительный код, который через элел1ент ИЛИ 9 подается на выходную шину 10 (см. эпюру 65). В случае, если исходное двоично-десятичное число положительное, триггер 4 находится в нулевом состоянии, вследствие чего результат преобразования с выхода элемента ИЛИ 39 через элементы И 8 и ИЛИ 9 попадает на выходную щину 10 (см. эпюру 65) На фиг. 2 рассмотрен случай преобразования двоично-десятичного кода целого числа O.llllOOlOOlOOlOi в двоичный код 0,001111011110101, выдача которого осуществляется с шестнадцатого по тридцать первый такт. Таким образом, предлагаемое устройство осуществляет преобразование двоично-десятичных кодов целых чисел в двоичные за менее 2 тактов, т.е. является в 2,5 раза быстродействующим по сравнению с известными устройствами для преобразования двоично-десятичных чисел в двоичные.

В случае преобразования двоично-десятичных кодов дробных чисел в двоичные на управляющую щину 23 подается единичный логический уровень (см. фиг. 3 эпюру 66). В результате выход сумматора 27 через элемент И 22 оказывается подключенным ко входу блока 40 умножения. Так как исходное дробное двоично-десятичное число принимается за целое, блок 40 осуществляет умножение результата преобразования, снимаемого с сумматора 27, на число 1/2 где m - разрядность преобразуемого десятичного числа. Таким образом в рассматриваемом случае т 4 и блок 40 умножает результат преобразования на число 1/10000. С целью получения точности преобразования для максимальной ошибки порядка щестнадцатый разряд искомого двоичного кода преобразуемого двоично-десятичного числа, блок 40, согласно фиг. 1, осуществляет умножение на число 0.00000000000001101000110111. Полученный результат с выхода блока 40 умножения подается на вход элемента ИЛИ 39 (см. эпюру 68 на фиг. 3). Далее устройство функционирует аналогично рассмотренному, и результат снимается с выходной щины 10 (см. фиг. 3 эпюру 65) с 21-го по 36-ой такты.

На фиг. 3 рассмотрен случай преобразования двоично-десятичного кода дробного числа 1.101001101000010 в двоичный код 1.011101110011111. Таким образом, данное устройство осуществляет преобразование двоично-десятичных кодов дробных чисел в двоичные за 2п + 4 такта, т.е. является приблизительно в 2,2 раза быстродействующим по сравнению с известными устройствами для преобразования двоично-десятичных чисел в двоичные.

Таким образом, в данном изобретении достигается повышение быстродействия преобразования двоично-десятичных кодов целых чисел в двоичные в 2,5 раза и двоичнодесятичных кодов дробных чисел в двоичные в 2,2 раза по сравнению с известными устройствами.

Формула изобретения

Устройство для преобразования двоично-десятичных чисел в двоичные, содержащее распределитель, информационный вход которого соединен с первой управляющей щиной устройства, установочный вход - с щиной сброса устройства и нулевым входом триггера, единичный вход которого подключен к выходу первого элемента И, а единичный выход - к первому входу второго элемента И и через первый элемент НЕ к первому входу третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к выходной щине устройства, а второй вход - к выходу сумматора и входу элемента задержки, выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу второго элемента И, при этом разрядные выходы распределителя с первого по четвертый соединены со входами второго элемента ИЛИ, выход которого подключен к первому входу четвертого элемента И, разрядные выходы распределителя с пятого по восьмой соеди0 иены со входами третьего элемента ИЛИ, выход которого подключен к первому входупятого элемента И, разрядные выходы распределителя с девятого по двенадцатый соединены со входами четвертого элемента ИЛИ, выход которого подключен к первому

5 входу шестого элемента И, разрядные выходы распределителя с тринадцатого по пятнадцатый соединены со входами пятого элемента ИЛИ, выход которого подключен к первому входу седьмого элемента И, щестнадцатый разрядный выход распределителя соединен с первым входом первого элемента И, второй вход которого подключен ко входной информационной шине устройства и ко вторым входам четвертого, пятого, шестого и седьмого элементов И, а также восьмой элемент И, первый вход которого соединен со второй управляющей шиной устройства и через второй элемент НЕ с первым входом девятого элемента И, отличающееся тем, что, с целью повышения быстродействия, в него введены блок умножения,

0 дополнительный элемент ИЛИ, дополнительные сумматоры и дополнительные элементы задержки, при этом выход четвертого элемента И через девятитактный дополнительный элемент задержки соединен с первым входом первого дополнительного сумматора, выход которого соединен со вторыми входами восьмого и девятого элементов И, выход пятого элемента И через первый шеститактный дополнительный элемент задержки подключен к первому входу второго дополнительного сумматора, выход которого соединен с первым входом третьего дополнительного сумматора и через первый двухтактный дополнительный элемент задержки со вторым входом третьего дополнительного сумматора, выход которого подключен к второму входу первого дополнительного сумматора, выход шестого элемента И через трехтактный дополнительный, элемент задержки соединен с первым входом четвертого дополнительного сумматора, выход которого подключен к первому входу пятого дополнительного сумматора и через второй двухтактный дополнительный элемент задержки - ко второму входу пятого допол штельного сумматора выход которого соединен со вторым входом второго дополнительного сумматора, выход седьмого элемента И соединен с первым входом шестого дополнительного сумматора и через третий двухтактный дополнительный элемент задержки со вторым входом шестого дополнительного сумматора, выход которого подключен ко второму входу четвертого дополнительного сумматора, выход девятого элемента И через второй шеститактный дополнительный элемент задержки подключен к первому входу дополнительного элемента ИЛИ, второй вход которого через блок умножения соединен с выходом восьмого элемента И, при этом выход дополнительного элемента ИЛИ подключен ко вторым входам второго и третьего элементов И/

Источники информации, принятые во внимание при экспертизе

1.Карцев М. А. Арифметика цифровых машин. М., «Наука, 1969, с. 543, рис. 5-7.

2.Авторское свидетельство СССР № 269598, кл. G 06 F 5/02, 28.03.69.

3.Авторское свидетельство СССР

№ 404077, кл. G 06 F 5/02, 07.10.71 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичныхчиСЕл B дВОичНО-дЕСяТичНыЕ | 1979 |

|

SU809153A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1978 |

|

SU779999A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU669352A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь правильной двоичнодесятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные числа | 1974 |

|

SU526886A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Универсальный преобразователь двоично-десятичных чисел в двоичные | 1973 |

|

SU473179A1 |

Г I 3 Ч 5 6 П П П

7

П

f8

П

э

54

55

5S

57

58

55

ео

SI

62

3

П П

П П гтгп птп

Sf

е5 9е

S7

П

И

ПП

П

П

ГП П ГП

m m

m ГП

гтгп гтгп

П П I I I I I I I I I I 789 Ю111Z 121f15iein81320ZTZZZ32f25ZSZ728293031 П Mill

Авторы

Даты

1981-02-28—Публикация

1979-03-14—Подача