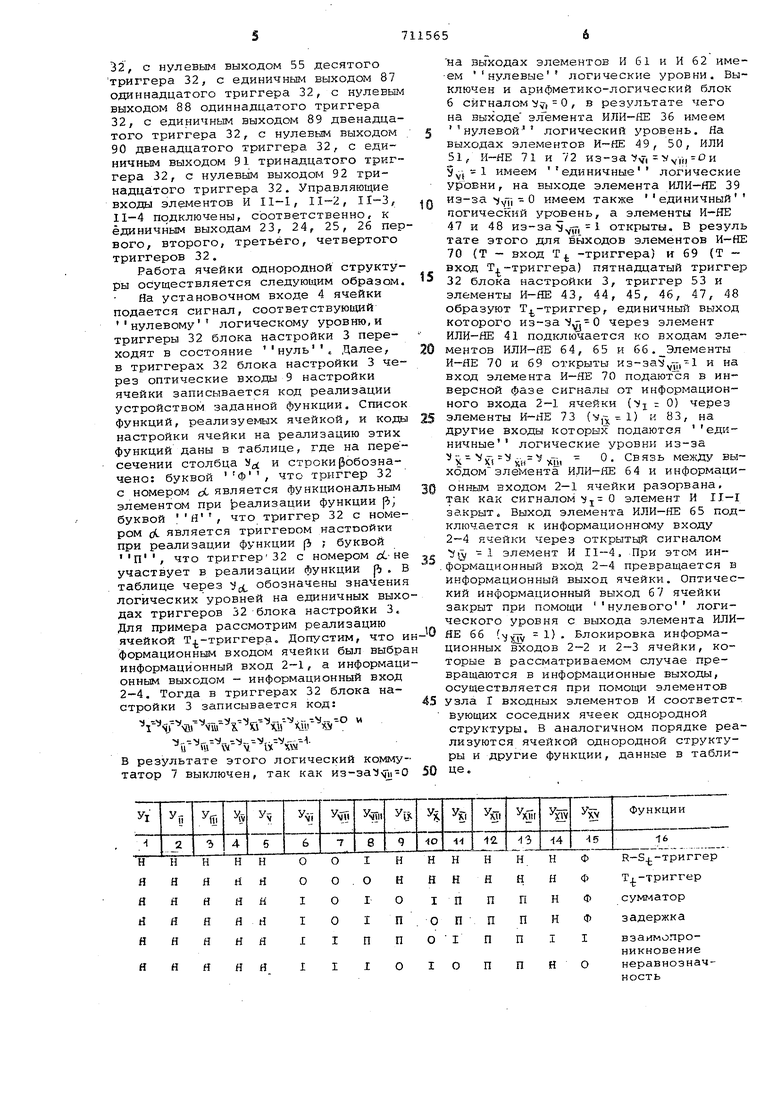

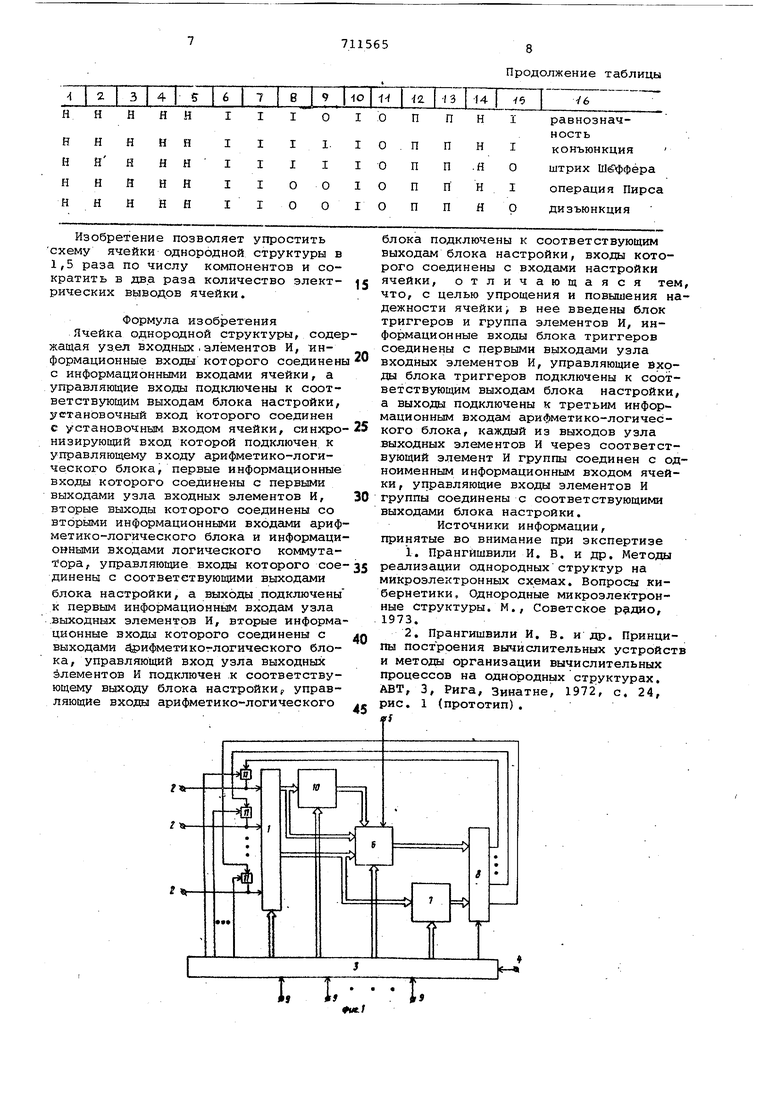

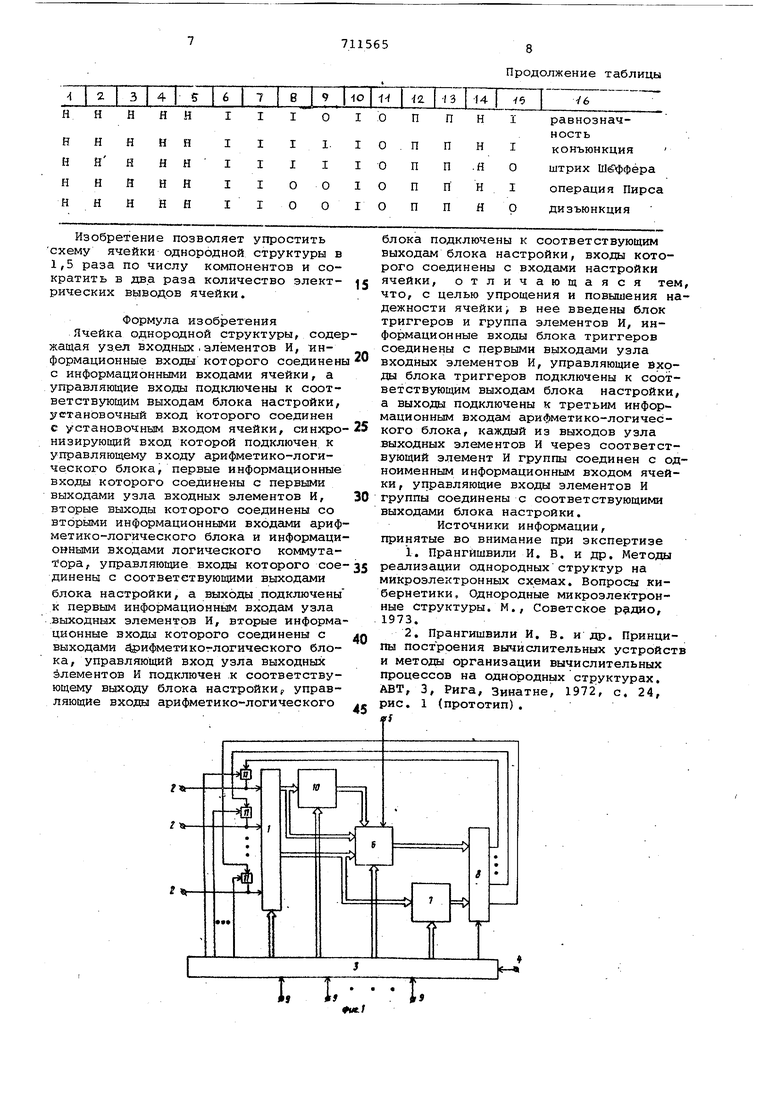

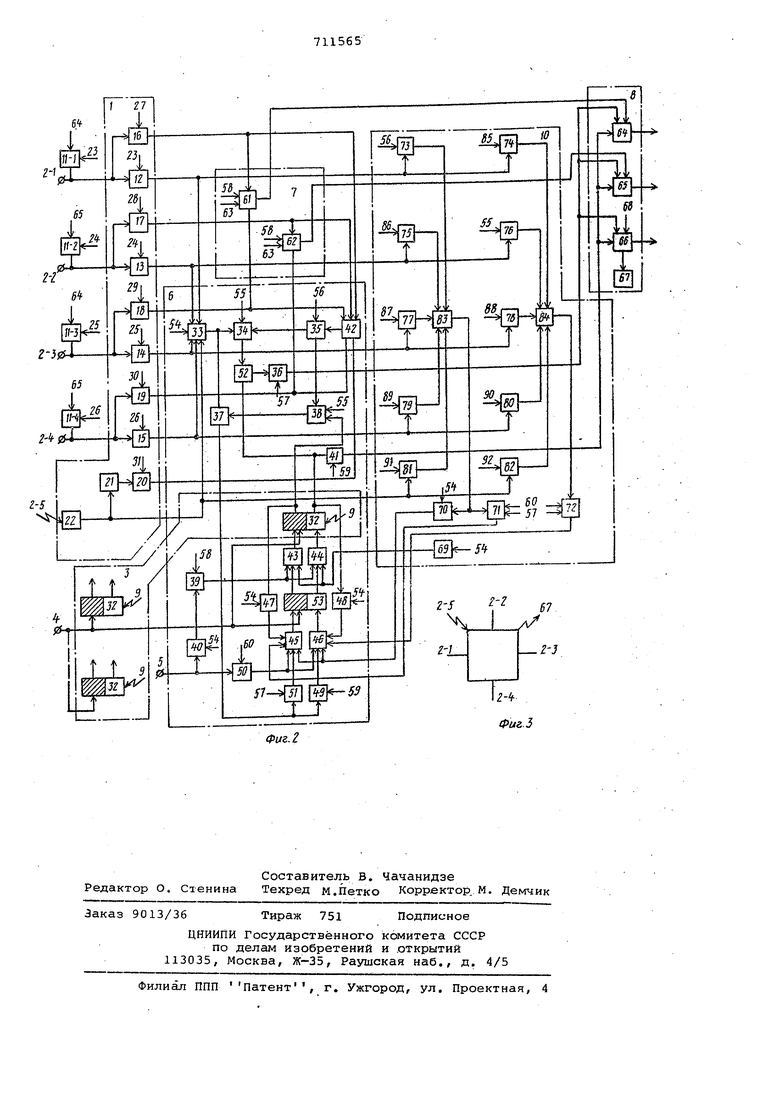

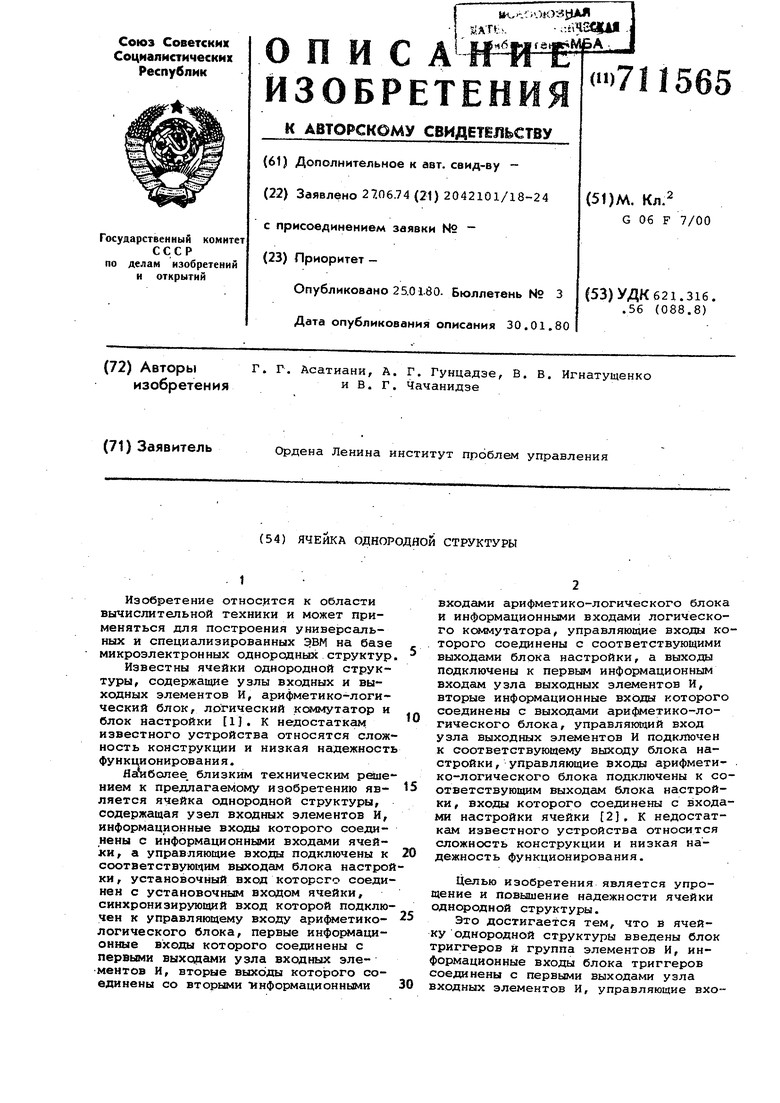

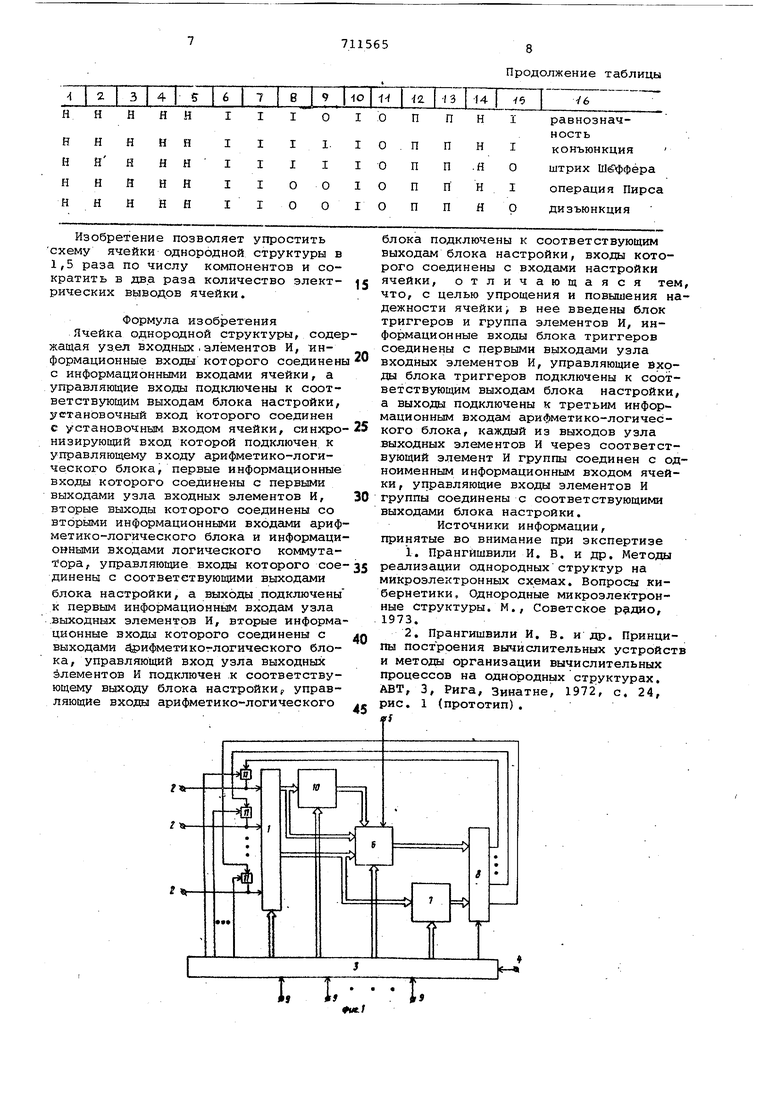

(54) ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ Ды блока триггеров подключены к соответствующим выходам блока настройки, а выходы подключены к третьим ин формационным входам арифметико-логического блока, каждый из выходов узпа выходных элементов И через соответств ющий элемент И группы соединен с одноименным информационным вхо дом, ячейки, управляющие входы элемен тов И группы соединены с соответству ющими выходами .блока настройки. На фиг. 1 представлена функционал ная схема ячейки однородной структуры на фиг. 2 - пример реализации ячейки однородной структуры; на фиг. 3 - сх матическое изображение ячейки одноро ной структуры. Предлагаемая ячейка содержит узел 1 входных элементов И, информационные входы которого соединены с информационными входами 2 ячейки , а управляющие входы подключены к соответствующим выходам блока 3 настройки, установочный вход которого соединен с установочным входом 4 ячейки, синхронизирующий вход 5 которой подключен к управляющему входу арифметико-логического блока б, первые информационные входы которого соединены с первыми выходами узла 1 входных элементов И, вторые выходы которого соединены со вторыми информационными входами арифметико-логического блока 6 и информационными входами логического коммутатора 7, управляющие входы которого соединены с соответствующими выходами блока 3 настройки, а выходы подключены к первым информацион ным входам узла 8 выходных элементов И, вторые информационные входы которого соединены с ВЕЯходами арифметико логическо1ео блока 6 управляющий вход узла 8 выходных элементов И под kлючeн к соответствующему выходу бло ка настройки 3; управляющие входы арифметико-логического блока б под-. ключены к соответствующим выходам блока настройки 3, входы которого со единены с входами 9 настройки ячейки Информационные входы блока 10 триггеров соединены с первыми выходами узла 1 входных элементов И, управляющие входы подключены к соответствующим выходам блока настройки 3, а выходы подключены к третьим информационным входам арифметико-логического бЬока б; Каждый из выходов узла 8 вь кодных элементов И через соответ ствующий элемент И II группы соединен с одноименным информационным вхо дом 2 ячейки; управляющие входы элементов И II группы соединены с соответствующими выходами блока настройки 3. Узел 1 входных элементов И содержит элементы ИЛИ-НЕ 12-15, И-НЕ 16НЕ 21 и фотоприемник 22, представля ший собой, например, работающий в оптическом режиме МОП-транзистор. Управляющие входы элементов ИЛИ-НЕ 1215 соединены с единичными выходами 23-26 первых четырех триггеров блока настройки 3, а управ.ляющие входы элементов И-НЕ 16-19 подключены к нулевым выходам 27-30 этих же .еров; управляющий вход элемента 20 соединен с нулевым выходом 31 пятого триггера блока настройки 3. Выходы элементов ИЛИ-НЕ 12-15 и фотоприемника 22 образуют первые выходы узла 1 входных элементов И, а выходы элементов И-НЕ 16-20 - вторые выходы узла I входных элементов И. Блок настройки, 3 содержит пятнадцать триггеров 32 на элементах И-НЕ с оптической записью единицы. Арифметико-логический блок -6 содержит элементы ИЛИ- НЕ 33-41, И-НЕ 42-50, ИЛИ 51, неравнозначности 52 и триггер ЬЗ на элементах И-НЕ. Управляющие входы элементов ИЛИ-НЕ 33734,,38,39,40, 41 соединены,соответственно, с нулевым выходом 54 восьмого триггера 32, с нулевым выходом 55 десятого триггера 32, с единичным выходом 56 девятого триггера 32, с нулевым выходом 57 шестого триггера 32, с нулевым выходом 55 десятого триггера 32, с единичным выходом 58 седьмого триггера 32, с нулевым выходом 54 восьмого триггера 32,.с единичным выходом 59 шестого триггера 32. Управляющие входы.элементов И-ЯЕ 47 и 48 соединены с нулевым выходом 54 восьмого триггера 32; управляющий вход элемента И-НЕ 49 соединен с единичным выходом 59 шестого триггера 32 управляющий вход .элемента И-НЕ 50 подключен к единичному выходу 60 восьмого триггера 32; Управляющий вход элемента ИЛИ 51 соединен с нулевым выходом 57 шестого триггера 32. Логический коммутатор 7 содержит элементы И 61, 62, управляющие входы которых подключены к единичному выходу 58 седьмого и нулевому выходу 63 одиннадцатого триггеров 32. Узел 8 выходных элементов И содержит элементы ИЛИ-НЕ 64, 65, 66 и светодиод 67; управляющий вход элемента ИЛИ- НЕ 66 соединен с единичным выходом 68 четырнадцатого триггера 32, а выход светодиода 67 образует оптический информационный выход ячейки. Блок 10 триггеров содержит элементы И-НЕ 69-84; управляющие входы элеМентов И-НЕ 69 и 70 соединены с нулевым выходом 54 восьмого триггера 32; управляющие входы элементов И-НЕ 71, 72 подключены к нулевому выходу 57 щестого и единичному выходу 60 восьмого триггеров 32; управляющие входы элементов И-НЕ 73-82 соединены, соответственно, с единичным выходом Ь6 девятого триггера 32, с ну.певым выходом 85 девятого триггера 32, с единичным выходом 86 десятого триггера 32, с нулевым выходом 55 десятого триггера 32, с единичны. выходом 87 одиннадцатого триггера 32, с нулевым выходом 88 одиннадцатого триггера 32, с единичным выходом 89 двенадцатого триггера 32, с нулевым выходом 90 двенадцатого триггера 32, с единичным выходом 91 тринадцатого триггера 32, с нулевым выходом 92 тринадца:того триггера 32. Управляющие входы элементов И II-I, II-2, II-3, 11-4 подключены, соответственно, к единичным выходам 23, 24, 25, 26 пер вого, второго, третьего, четвертого триггеров 32, Работа ячейки однородной структуры осуществляется следующим образом На установочном входе 4 ячейки подается сигнал, соответствующий нулевому логическому уровню,и триггеры 32 блока настройки 3 переходят в состояние нуль. Далее, в триггерах 32 блока настройки 3 через оптические входы 9 настройки ячейки записывается код реализации устройством заданной функции. Список функций, реализуемых ячейкой, и коды настройки ячейки на реализацию этих функций даны в таблице, где на пере сечении столбца V и строки (Зобозначено: буквой Ф, что триггер 32 с номером ciC является функциональнЕЛМ элементом при еализации функции р; буквой Н, что триггер 32 с номе ром oL является триггером насттзойки при реализации функции р буквой П, что триггер32 с номером оС-не участвует в реализации функции Ь . В таблице через у обозначены значени логических уровней на единичных выхо дах триггеров 32 блока настройки 3. Для примера рассмотрим реализацию ячейкой Т -триггера. Допустим, что и формационным входом ячейки был выбра информационный вход 2-1, а информаци онным выходом - информационный вход 2-4. Тогда в триггерах 32 блока настройки 3 записывается код: rV vir 41irW iQrKiH 4,o N - N - -N -N N - и Л lie XW В результате этого логический комму татор 7 выключен, так как из-заЭчщ-О на вь ходах элементов И 61 и И 62 имеем нулевые логические уровни. Выключен и арифметико-логический блок б сигналом Уу-, О , в результате чего на выходе элемента ИЛИ-НЕ 36 имеем нулевой- логический уровень. На выходах элементов 49, 50, ИЛИ 51/ И-НЕ 71 и 72 из-за Nviir и 5у( 1 имеем единичные логические уровни, на выходе элемента ИЛИ-НЕ 39 из-за - О имеем также единичный логический уровень, а элементы И-ЯЕ 47 и 48 из-за , 1 открыты, В резуль тате этого для выходов элементов И-НЕ 70 (Т - вход Т -триггера) и 69 {Т вход Т -триггера) пятнадцатый триггер 32 блока настройки 3, триггер 53 и элементы И-ЯЕ 43, 44, 45, 46, 47, 48 образуют Т -триггер, единичный выход которого из-за j О через элемент ИЛИ-ЯЕ 41 подключается ко входам элементов ИЛИ-ЯЕ 64, 65 и 66.Элементы И-ЯЕ 70 и 69 открыты из-за -,;,-1 и на вход элемента И-ЯЕ 70 подают ся в инверсной фазе сигналы от информационного входа 2-1 ячейки (Vj г 0) через элементы И-ЯЕ 73 (v,- 1) и 83, на другие входы которых подаются единичные логические уровни из-за х Xi W1 О- Связь между выходомэлемента ИЛИ-ЯЕ 64 и информационным входом 2-1 ячейки разорвана, так как сигналом j О элемент И IJ-I закрыт. Выход элемента ИЛИ-ЯЕ 65 подключается к информационному входу 2-4 ячейки через открытый сигналом -1 элемент И 11-4, При этом информационный вход 2-4 превращается в информационный выход ячейки. Оптический информационный выход 67 ячейки закрыт при помощи нулевого логического уровня с выхода элемента ИЛИ- ЯЕ 66 fv)uy Блокировка информационных входов 2-2 и 2-3 ячейки, которые в рассматриваемом случае превращаются в информационные выходы, осуществляется при помощи элементов зла I входных элементов И соответствующих соседних ячеек однородной структуры. В аналогичном порядке реализуются ячейкой однородной структуры и другие функции, данные в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной структуры | 1974 |

|

SU711564A1 |

| Ячейка однородной структуры | 1990 |

|

SU1778757A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 1993 |

|

RU2036511C1 |

| Ячейка однородной структуры | 1985 |

|

SU1363180A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1443000A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Ячейка однородной структуры | 1973 |

|

SU711563A1 |

| УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ РАСТРОВЫХ СИСТЕМ ПРОДУКЦИЙ | 1998 |

|

RU2154858C2 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

Я я

никновение О неравнозначПность Изобретение позволяет упростить схему ячейки однородной структуры в 1,5 раза по числу компонентов и сократить в два раза количество электрических выводов ячейки. Формула изобретения Ячейка однородной структуры, содер жащая узел входных , элементов И, информационные входы которого соединены с информационными входами ячейки, а управляющие входы подключены к соответствующим выходам блока настройки, установочный вход которого соединен с установочным входом ячейки, синхро низирующий вход которой подключен к управляющему входу арифметико-логического блока, первые информационные входы которого соединены с первыми выходами узла входных элементов И, вторые выходы которого соединены со вторыми информационными входами ариф метико-логического блока и информаци онными входами логического коммутатора, управляющие входы которого сое динены с соответствующими выходами блока настройки, а выходы .подключены к первым информационным входам узла .выходных элементов И, вторые информа ционные входы которого соединены с выходами Зрифметикоглогического блока, управляющий вход узла выходных Элементов И подключен .к соответствующему выходу блока настройки, управляющие входы арифметико-логического

I I,- I.

Продолжение таблицы блока подключены к соответствующим выходам блока настройки, входы которого соединены с входами настройки ячейки, отличающаяся тем, что, с целью упрощения и повышения надежности ячейки, в нее введены блок триггеров и группа элементов И, информационные входы блока триггеров соединены с первыми выходами узла входных элементов И, управляющие Входы блока триггеров подключены к соотвeтcтвs oщим выходам блока настройки, а выходы подключены к третьим информационным входам арифметико-логического блока, каждый из выходов узла выходных элементов И через соответствующий элемент И группы соединен с одноименным информационным входом ячейки , управляющие входы элементов И группы соединены с соответствующими выходами блока настройки. Источники информации, принятые во внимание при экспертизе 1.Прангйшвили И, В. и др. Методы реализации однородных структур на микроэлектронных схемах. Вопросы кибернетики. Однородные микроэлектронные структуры. М., Советское , 2.Прангйшвили И. В. и др. Принципы построения вычислительных устройств и метода организации вычислительных процессов на однородных структурах. АВТ, 3, Рига, Зинатне, 1972, с. 24, рис. 1 (прототип).

Авторы

Даты

1980-01-25—Публикация

1974-06-27—Подача