I

Изобретение относится к области запоминающих устройств.

Одно из известных устройств содержит накопитель, адресный дешифратор, блоки ввода и вывода информации 1 .

Недостатком известного устройства являются большие аппаратурные затраты и малая скорость работы.

Из известных устройств наиболее близким техническим решением к данному изобретению является буферное запоминающее устройство, содержащее накопитель, информационные входы которого соединены с выходами элементов И первой группы, а информационные выходы с первыми входами элементов И второй группы, третью группу элементов И, первые входы которых подключены к пине опроса, а выходы - ко входам опроса накопителя, входные шины и шины разрешения записи, соединенные соответственно со входами элементов И первой группы,

выходные шины и шины разрешения считывания 2.

Недостатком этого устройства является неэффективное использование-емкости накопителя, состоящего из отдельных блоков, каждый из которых предназначен для хранения информации только одного какого-либо источника сообщений: возможны случаи отказа одних блоков по причине переполнения, в то время как другие блоки свободны.

Другим недостатком устройства является то, что для регистрации заполнения блоков накопителя необходимо для каждого из блоков накопителя предусмотреть блок .контроля и сигнализации о его заполнении, что приводит к существенным аппаратурным затратам, особенно в случае большого числа обслуживаемых источников сообщений и повышенных требований по обеспечению, надежности.

Целью настоящего изобретения является упрощение и повышение надежности устройства.

37

Поставленная цель достигается тем, что устройство содержит шифратор, дополнительные накопители, дешифратор, элемент ИЛИ-НЕ и блоки формирования сигналов заполнения дополнительных накопителей, входы которых подключены к одним из выходов дополнительных накопителей, а выходы - ко входам элемента ИЛИ-НЕ выкод которого соединен со вторыми входами элементов И третьей группы, другие выходы дополнительных накопителей соединены с выходными шинами, а входы - соответственно с шинами разрешения считывания и выходами элементов И второй группы, входы дешифратора подключены к контрольным выходам накопителя, а выходы - ко вторым входам элементов И второй группы, входы шифратора соединены с шинами разрешения записи, а выходы - с контрольными входами накопителя.

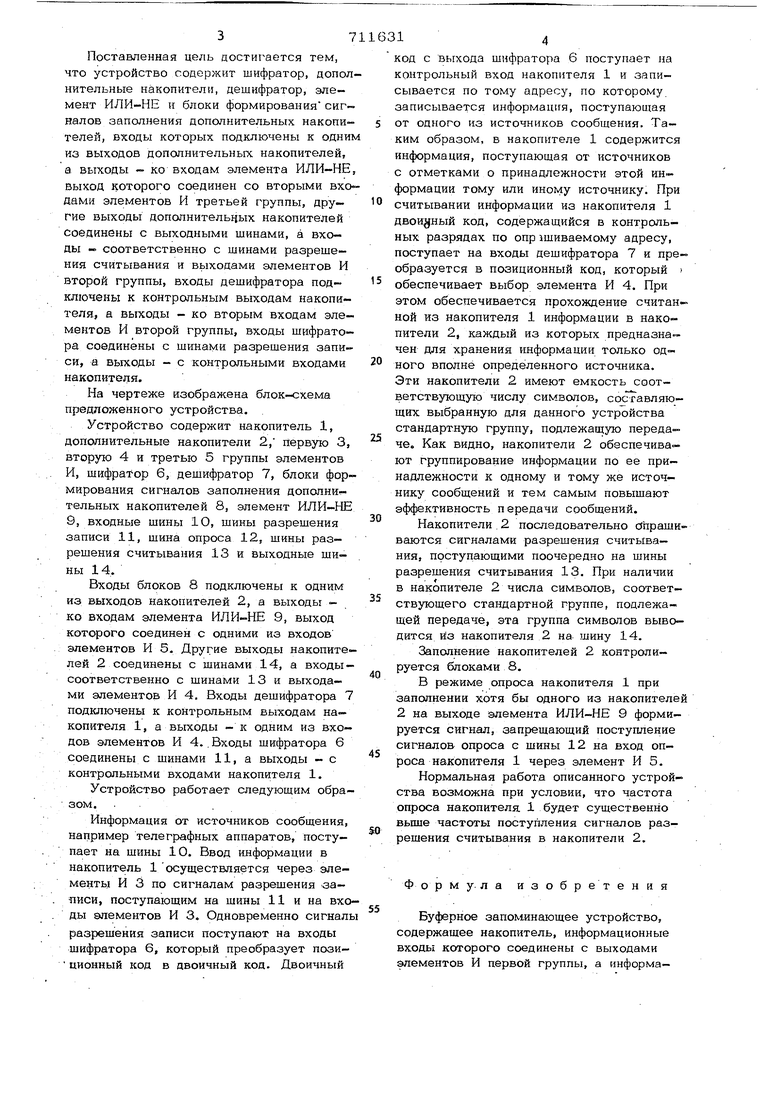

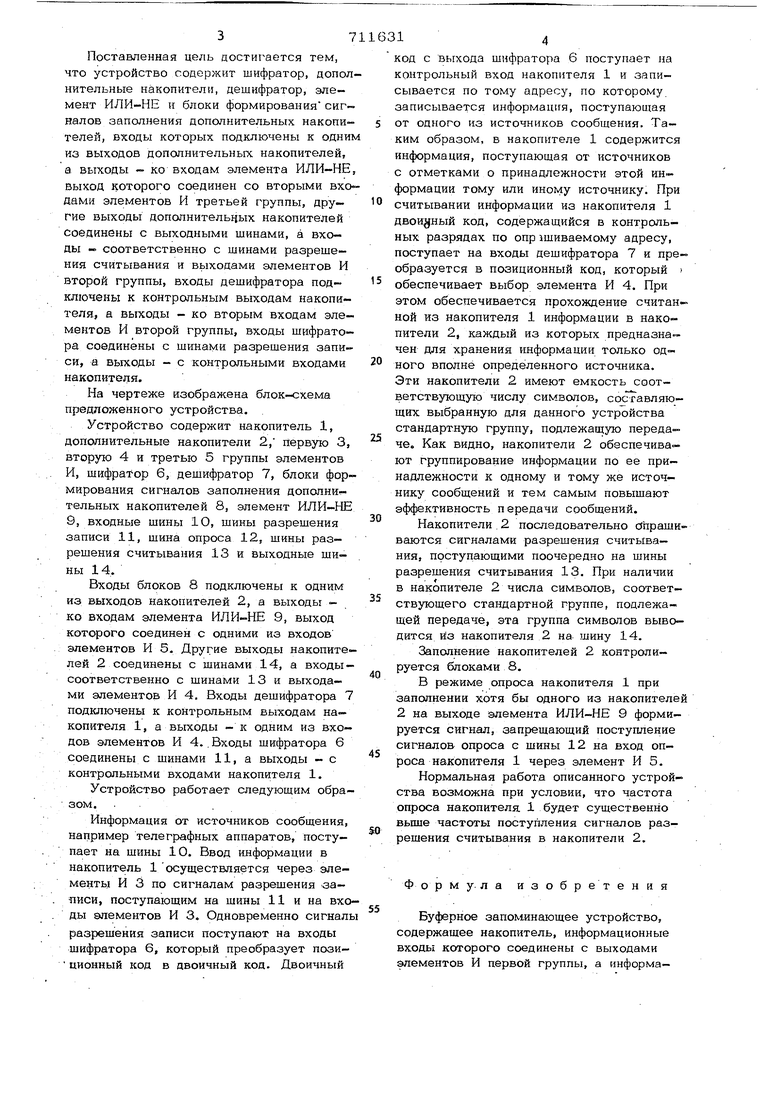

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит накопитель 1, дополнительные накопители 2, первую 3, вторую 4 и третью 5 группы элементов И, шифратор 6, дешифратор 7, блоки формирования сигналов заполнения дополнительных накопителей 8, элемент ИЛИ-НЕ 9, входные шины Ю, шины разрешения записи И, шина опроса 12, шины разрешения считывания 13 и выходные шины 14.

Входы блоков 8 подключены к одним из выходов накопителей 2, а выходы - ко входам элемента ИЛИ-НЕ 9, выход которого соединен с одними из входов элементов И 5. Другие выходы накопителей 2 соединены с шинами 14, а входы - соответственно с шинами 13 и выходами элементов И 4, Входы дешифратора 7 подключены к контрольным выходам накопителя 1, а выходы - к одним из входов элементов И 4. .Входы шифратора 6 соединены с шинами 11, а выходы - с контрольными входами накопителя 1.

Устройство работает следующим обра- зом. .

Информация от источников сообщения, например телеграфных аппаратов, поступает на шины Ю. Ввод информации в накопитель 1 осуществляется через элементы И 3 по сигналам разрешения -записи, поступающим на шины 11 и на входы элементов И 3. Одновременно сигналы разрешения записи поступают на входы шифратора 6, который преобразует позиционный код в двоичный код. Двоичный

6314

код с выхода шифратора 6 поступает на контрольный вход накопителя 1 и записывается по тому адресу, по которому записывается информация, поступающая

5 от одного из источников сообщения. Таким образом, в накопителе 1 содержится информация, поступающая от источников с отметками о принадлежности этой информации тому или иному источнику. При

0 считывании информации из накопителя 1 двоичный код, содержащийся в контрольных разрядах по опр 5шиваемому адресу, поступает на входы дешифратора 7 и преобразуется в позиционный код, который

обеспечивает выбор элемента И 4. При этом обеспечивается прохождение считанной из накопителя 1 информации в накопители 2, каждый из которых предназначен для хранения информации только одного вполне определенного источника. Эти накопители 2 имеют емкость соответствующую числу символов, со(гавляю- щих выбранную для данного устройства стандартную группу, подлежащую передаче. Как видно, накопители 2 обеспечивают группирование информации по ее принадлежности к одному и тому же источнику сообщений и тем самым повышают эффективность передачи сообщений.

Накопители 2 последовательно опрашиваются сигналами разрешения считывания, поступающими поочередно на шины разрешения считывания 13. При наличии в накопителе 2 числа символов, соответствующего стандартной группе, подлежащей передаче, эта группа символов выводится из накопителя 2 на шину 14.

Заполнение накопителей 2 контролируется блоками 8.

В режиме опроса накопителя 1 при заполнении хотя бы одного из накопителей 2 на выходе элемента ИЛИ-НЕ 9 формируется сигнал, запрещающий поступление сигналов опроса с шины 12 ка вход опроса накопителя 1 через элемент И 5.

Нормальная работа описанного устройства возможна при условии, что частота опроса накопителя 1 будет существенно вьшде частоты поступления сигналов разрешения считывания в накопители 2.

Формула изобретения

Буферное запоминающее устройство, содержащее накопитель, информационные входы которого соединены с выходами элементов И первой группы, а информа-

5

ционные выходы - с первыми входами элементов И второй группы, третью груп пу элементов И, первые входы которых подключены к шине опроса, а выходы ко.входам опроса накопителя, входные шины и шины разрешения записи, соеди ненные соответственно со входами элементов И первой группы, выходные шины и шины разрешения считывания, отличающееся тем, что, с целью упрощения и повьш1ения надежности устройства, оно содержит шифратор, дополнительные накопители, дешифратор, элемент ИЛИ-НЕ и блоки формирования сигналов заполнения дополнительных накопителей, входы которых подключены к одним из выходов дополнительных накопителей, а выходы - ко входам элемента ИЛИ-НЕ, выход которого соединен со

16

вторыми входами элементов И третьей группы, другие выходы дополнительных накопителей соединены с выходными шинами, а входы - соответственно с шина-

ми разрешения считывания и выходами элементов И второй группы входы дешифратора подключены к контрольным выходам накопителя, а выходы - ко БТО рым входам элементов И второй группы,

входы шифратора соединены с шинами разрешения записи, а выходы - с контрольными входами накопителя.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 371613, кл. G 11 С 9/ОО, 1971.

2.Патент ФРГ № 1268 652,

кл. G 11 С 9/ОО, 1968 (прототип;.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1980 |

|

SU888202A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗАПОЛНЕНИЯ ПУТЕЙ ПОДГОРОЧНОГО ПАРКА | 1996 |

|

RU2105687C1 |

| Запоминающее устройство | 1978 |

|

SU743031A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1785039A1 |

| Ассоциативное запоминающее устройство | 1991 |

|

SU1833917A1 |

| Буферное запоминающее устройство | 1979 |

|

SU834766A1 |

| Устройство для сопряжения | 1978 |

|

SU777655A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

Авторы

Даты

1980-01-25—Публикация

1977-09-13—Подача