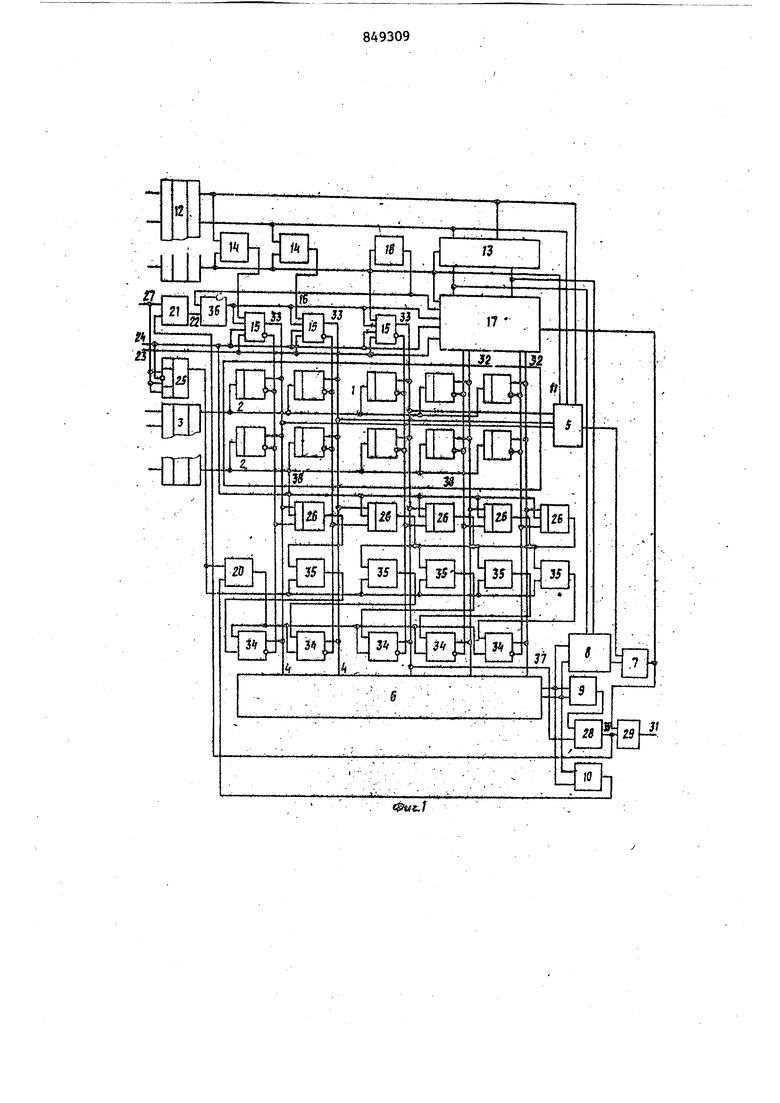

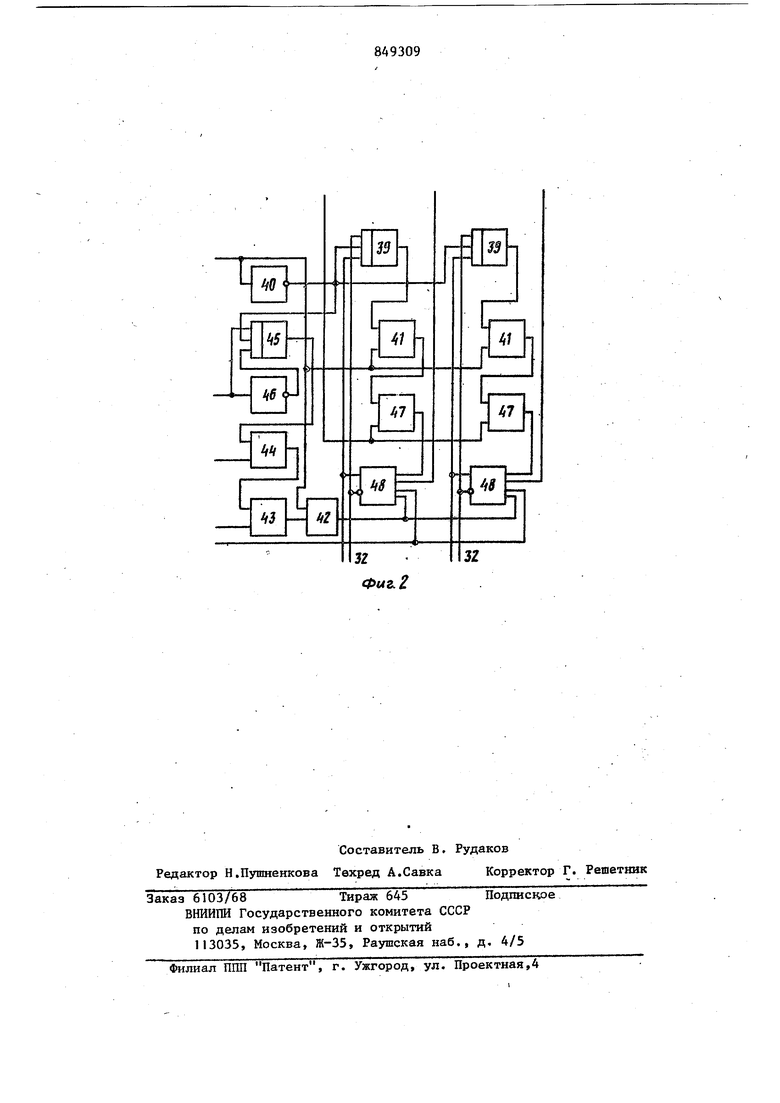

. (54)ЗАПОМ1ШАЩЕЕ УСТРОЙСТВО МАТРИЧНОГО TI-fflA С САМОКОНТРОЛЕМ Изобре тение относится, к области запоминающих устройств. Известно запоминающее устройство матричного ,типа, содержащее на копитель, дешифраторы строк и столбц блок считывания, элемент И, шинь записи, разрешения записи и управления Недостатком этого устройства является то, что его работоспособность нарушается при отказах и сбоях элементов памяти накопителя. Наиболее близким тёкютческим решением к изобретению является запоминающее устройство, содержащее нако питель, дешифраторы адреса столбцов и строки, блоки считывания, кодирова и контроля, первый и второй блоки ко рекции, первый сумматор по модулю два, шины записи, разрешения записи и управления 2, Однако это устройство характеризуется низкой надежностью из-за кор рекции только однократных ошибок в каждой строке накопителя. ,. Цель изобретения - повьшгение надежности устройства за счет исправления двухкратных ошибок в каждой строке накопителя.х Поставленная цель достигается тем, что в запоминающее устройство матричного типа с самоконтролем, содержащее накопитель, дешифратор столбцов, дешифратор , блок кодирования, первый и второй блоки коррекции, блок контроля, -первый сумматор,блок считывания, перовую tpynny элементов И и шины записи, разрешения записи и управления, причем числовые шинЫ накогштеля соединены с выходами дешифратора строк, выходные шины - со входами блока считывания и блока контроля, выходы которого соединены с одними из входов первого блока коррекции, другие входы которого соединены с выходами блока кодирования, выходы дешифратора столбцов подключе11ы к входам блока кодирования и управляюи ям входам блока считывания,выкод которого и выход первого блока коррекции соединены со входами первогр сумматора, одни из входов второго блока коррекции подключены соответственно к выходам блока кодирования, пшне разрешения записи, шине управления и выходу первого сумматора, разрядные шины накопителя подключены к выходам второго блока коррекции и эле ментов И первой группы, одни из входов которых соединены с шиной разрешения записи и шиной управления введены второй, третий и четвертый сумматоры., триггер, первый, второй и третий элементы И, элемент ИЛИ, элемент НЕ, группу триггеров, группу.сум маторов, вторзпо группу элементов И и группу элементов ИЛИ, причем входы второго сумматора соединены с шиной записи, одними из входов триггера и выходом третьего сумматора, выход вто рого сумматора соединен с первым входом третьего элемента И, входы чет вертого сумматора соединены с выходами первого и третьего сумматоров, входы третьего сумматора подключены соответственно к одной из выходных ши накопителя и выходу первого элемента И, входы которого соединены с выходами блока контроля и входами элемента ИЛИ, выход которого соединен с пер вьм входом второго элемента И, второй вход которого подключен к выходу триг гера и первым входам сумматоров группы, управляюшде и информационные входы триггеров группы соединены соответ ственно с шиной разрешетгя записи, другим входом триггера, разрядньп-ш шинами накопителя и выходами элементов И второй группы, выходы триггеров соединены соответственно со вторыми входами сумматоров группы, выходы которых подключены к первым входам элементов И второй группы,вторые входы которых соединены с выходом второго элемента И, другие входы вто рого блока коррекции подключены соответственно к выходу элемента НЕ и второму входу третьего элемента И, к одному из выходов дешифратора столбцов и первым входам, элементов ИЛИ группы, вторые входы кото рых соединены с другими выходами дешифратора столбцов, другие входы эле ментов И первой группы подключены соответственно к выходу третьего элемента И, выходам элементов ИЛИ группы, к одному из выходов дешифра94тора столбцов и входу элемента НЕ, а выход четвертого сумматора является выходом устройства. На фиг. 1 изображена функциональная схема устройства; на фиг. 2 схема выполнения второго блока коррекции. Предлагаемое устройство содержит иг. 1)накопитель 10,соединенный числовыми шинами 2 с выходами дешифратора 3 строк. Выходные шины 4 накопителя соединены с входами блоков считывания 5 и контроля 6. Выходы блоков считывания 5 и контроля 6 подключены соответственно к первому входу первого сумматора 7 и входам первого блока 8 коррекции, входам первого элемента И 9 и элемента ИЛИ 10. Выход первого 8 коррекции соединен со вторым входом первого сумматора 7. Управляющие входы 11 блока 5 считывания соединены с одними из входов дешифратора 12 столбцов, входами блока 13 кодирования. Устройство также содержит группу элементов ИЛИ 14, первую группу элементов И 15, имeюarJИx выходы 16, второй блок 17 коррекции,элемент НЕ 18, имёюшдй выход 19,второй элемент И 20, второй сумматор 21, имеюшлй выход 22, шину 23 управления, шину 24 разрешения записи, триггер 25, группу триггеров 26, шину 27 записи, третий 28 и четвертый 29 сумматоры, имеющие соответственно выходы 30 и 31. Блок 17 коррекции н элементы И 15 имеют соответственно выходы 32 и 33. Устройство также содержит вторую группу элементов И 34, группу сумматоров 35, третий элемент И 36.. Все перечисленные выше сумматоры 7, 21,28,19 и 35 являются сумматорами по модулю два. Входы сумматора 21 соединены с шиной 27, одними из входов триггера 25 и выходом 30 сумматора 28. Выход сумматора 21 соединен с первым входом элемента И 36. Входы сумматора 29 соединены с выходами сумматоров 7 и 28, входы сумматора 28 подключены соответственно к одной из выходных шин 37 накопителя 1 и выходу элемента И 9. Выход элемента ИЛИ 10 соединен с первым входом элемента,И 20, второй вход которого подключен к выходу триггера 25 и первым входам сумматоров 35. Управляющие н информа5ционные входы триггеров 26 соединены соответственно с шиной 24 другим вхрдом триггера 25, разрядными шина ми 38 накопителя 1 и выходами элементов И 34. Выходы триггеров 26 сое иены соответственно со вторыми входами сумматоров. 35, выходы которых подключень к первым входам элементов И 35, вторые входы которых соединены с выходом второго элемента И 20. . Одни .из входов блока 17 подключены; соответственно к выходам блока 13, шинам 23 и 24. Другие входы блока 17 подключены соответственно к выход элемента НЕ 18 и второму входу элемента И 36, к одному из выходов дешифратора 12 и первым входам элементов ИЛИ 11, вторые входы.которых сое динены с другими выходами дешифратора 12. Одни из входов элементов И 15 соединены с шинами 23 и 24, другие соответственно с выходом элемента И 36, выходами элементов ИЛИ 14, с одним из выходов дешифратора 12 и вх дом элемента НЕ 18, выход 31 сумматора 29 является выходом устройства. Второй блок коррекции 17 (фиг. 2) содержит группу триггеров 39, первый элемент НЕ 40, группу сумматоров 41, первый элемент И 42, элемент ИЛИ 43,сумматор по. модулю два 44,триггер 45, второй элемент НЕ 46, первую 47 и вторую 48 группы элементов И. Устройство работает следующим образом. При первоначальном включении источника питания(на фиг.1 не показан) элементы памяти накопителя 1 устанавливаются в нулевое состояние. Для этого на шины 23, 24, 27 подаются соответственно сигналы управления, разрешения записи и записи. При этом . на вход дешифратора 12 столбцов подают код адреса, соответствующий опросу К-го разряда накопителя, а на вход дешифратора 3 строк - код адреса соответствующий опросу первой строки. На выходе дешифратора 12 появляет ся единичный сигнал, который формирует на всех выходах блока 13 единичные сигналы и, проходя через элементы ИЛИ 14 и элемент НЕ 18, открывает элементы И 15, 42 и 48. Одновременно этот сигнал, инвертируясь на элементе НЕ 18, устанавливает на выходах элементов И 20 и 46 нулевые сигналы, которые записьтаются для хранения в первую строку накопителя и : 9 ,6 в триггеры 26. Сигнал с шины 24 снимается, в результате чего прекращается запись информации и производится контрольное считывание информации, хранимой в первой строке. При этом с выхода триггера 25 поступает единичный сигнал на вход элемента И 20, а блок 6 контроля вычисляет контрольные соотношения кода Хемминга.Результатом вычисления является проверочный вектор (синдром S), который равен нулю при отсутствии однократньк и двукратных ошибок в опрашиваемой строке накопителя 1 и не равен нулю - в противном слзгчае. Если сивдром не равен нулю () то с выхода элемента 10 поступает единичный сигнал, который открывает элементы И 36 и 34 и.инвертированная на сумматорах 35 информация записьгеает ся повторно в первую- строку накопителя. Таким образом, если в первой строке хранится слово, состоящее из 111 ..1, то сидром , если же .ВОЗМОЖНО наличие дефектного элемента памяти, находящегося в нулевом состоянии, то S О и информация о том, что слово инвертировано, хранится в к-ом разряде накопителя. Если синдром , то инвертирования хра1шмой информации не происходит, так как на выходе элемента ИЛИ 10 - нулевой сигнал, который держит закрытыми элементы И 38 и . Рассмотрим теперь запись и считывание информац1Ш. При записи информациил первона- . ально происходит контрольное считы- ание, в результате чего на сумматоре 7 корректируется сигнал с опрашиваемого разряда, а затем производится запись информации в основной и проерочные разряды (если опрашиваеый элемент памяти изменяет свое остояние. Одновременно с записью той информации происходит запись нформации о состоянии элементов амяти опрашиваемой строки в триггера 6. После снятия сигнала с шины 24 разрешения записи, производится второе контрольное считывание. При этом, если синдром , то хранимое в триггерах 26 слово не записьгоается инвертированным вновь в опрашиваемую строку накопителя 1. В противном случае, т.е. когца ФО, хранимое в триггерах 26 слово инвертируется на сз мматорах 35 и в таком виде перезаписывается в опрашиваемую строку.

Рассмотрим некоторые возможные случаи такого инвертирования.

1. До записи информации синд j ром . Это говорит о том, что в слове, не было дефелутных элементов памяти, или что записываемая инфор мация была согласована с состоянием дефектных элементов памяти благодаря ю входному инвертированию на сумматоре 21 исправленным на сумматоре 28 сигналом с к-го разряда накопителя 1 (элемент И. 9 служит для вьщеления сиродрома к-го разряда). После записи is

информации в опрапмв емый элемент памяти и в проверочные разряды вто-

рого контрольного считывания, когда синдром &°;t О, инвертирование хранимой информации позволяет согласовать 20 записываемую информацию и при отсут- ствии второго дефектного элемента памяти синдром становится равным

нулю S 0, в противном случае ,

и определяет позицию этой ошибки. 25

2. До записи информации . Это говорит о том, что в слове имеется один дефектный элемент памяти, состояние которого не совпадает с записываемой для хранения информацией. зо После записи информации синдром вновь не равен нулю ° 0. Это говорит о том,ЧТО обращение произошло или к исправному элементу памяти (а), или к дефектному элементу памяти(состоя- 35 ние которого не совпадает с той же хранимой информацией(б), или ко второму дефектному элементу ламяти, состояние которого до этого совпадало с хранимой информацией)с несовпадающей 40 информацией(в). При этом, инвертирование позволяет в случае (а) и (.6 согласовать записываемую для хранеигия информацию с состоянием дефектного элемента, хотя при этом может про- 45 изойти несогласование второго дефекта, на что указывает неравенство . нулю синдрома .

В случае (ё)инвертирование позволяет согласовать оба дефекта, в результате 50 чего .

При считывавши, как и в предыдущем случае, инвертирование считьшаемой информации на су1-1маторах 7 и 29 составляет правильной хранимую информацию. 55

Таким образом, повышается общая надежность хранения и воспроизведения информации. При этом число проверочных разрядов меньше, чем при использовании кодов с кодовым расстоянием, например (, направляющих двойные ошибки и, кроме того, построение схем контроля реализуется сравнительно простыми средствами.

Формула изобретения

Запоминающее устройство матричного типа с самоконтролем, содержащее накопитель, дешифратор столбцов, дешифратор строк, блок кодирования, первый и второй блоки коррекции, блок контроля, первый сумматор, блок считыва1шя, первую группу элементов И и ишны записи, разрешения записи и управления, причем числовые шины накопителя соединены с выходами дешифратора строк, выходные шины - со входами блока считывания и блока контро.ля, вьгходы которого соединены с од- 1шми из входов первого блока коррекции, другие входы которого соединены с выходами блока кодирования, выходы дешифратора столбцов подключены ко входам блока кодирования и управляющим входамблока считывания, выход которого и выход первого блока коррекции соединены со входами первого сумматора, одни из входов второго блока коррекции подключены соответст венно к выходам блока кодирования, шине разрешения записи, шине управления и выходу первого сумматора, разрядные шины накопителя подключены к выходам второго блока.коррекции и элементов И первой группы, одни из входов которых соединены с шиной разрешения записи и шиной правления,, отличающееся тем, что, с целью повьш1ения надежности устройства, оно содержит второй, третий и четвертый сумматоры, триггер, первый, второй и третий элементы И, элемент ИЛИ, элемент НЕ, группу триггеров, группу сумматоров, вторую группу элементов И и группу элементов ИЛ1-1, причем входы второго сумматора соединены с шиной записи, из входов триггера и выходом третьего сумматора, выход второго сумматора соединен с первым входом третьего элемента И, входы четвертого сумматора соединены с выходами .первого и третьего сумматоров, входы третьего сумматора подключены соответственно к одной из выходных шин накопителя и выходу первого элемента И, входы которого соединены с -выходами блока контроля и входами элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого подкл чен к выходу триггера и первым входам сумматоров группы, управляющие и информационные входы триггеров группы соединены соответственно с шиной разрешения записи, другим вхо дом триггера, разрядьшми шинами накопителя и выходами элементов И вто рой группы, выходы триггеров соединены соответственно со вторьми входами сумматоров группы, выходы кото рых подключены к первым входам элементов И второй грзшпы, вторые вхо ды которых соединены с выходом второго элемента И, другие входы втор го блока коррекции подключены соот910ветственно к выходу элемента НЕ и второму входу третьего элемента И, к одному из выходов дешифратора столбцов и первым входам элементов ИЛИ ГРЗШПЫ, вторые входы которых соединены с другими выходами дешифратора столбцов, дру15ие ходы элементов И первой группы Подключены соответственно к выходу третьего элемента И, выходам элементов ИЛИ группы, к одному из выходов дешифратора столбцов и входу элемента НЕ, а выход четвертого сумматора является выходом устройства, Источники информации, принятые во внимание при экспертизе 1. Микроэлектроника. Сб. статей. Под ред. Лукина Ф. А. М., вып. 5, Советское радио, 1972, с. 128-150. 2. Авторское свидетельство СССР № 598118, кл. в 11 С 11/00, 1975 (прототип).

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1975 |

|

SU602995A1 |

| Запоминающее устройство | 1981 |

|

SU1010654A1 |

| Запоминающее устройство | 1975 |

|

SU598118A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955209A1 |

| Запоминающее устройство матрич-НОгО ТипА C САМОКОНТРОлЕМ | 1979 |

|

SU841063A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

Авторы

Даты

1981-07-23—Публикация

1979-11-11—Подача