Изобретение относится к автоматике и вычислительной технике. Известны запоминающие устройства, содержащие накопитель, датчики кода адреса, дешифраторы адреса, группы элементов И и ИЛИ, обеспечивающих подклю чение датчика кода адреса к дешифратору адреса, входных и выходных информационных шин к соответствующим шинам устройства l. Недостатком устройства является то, что для случая записи многоразрядного кода требуется введение дополнительного оборудования в разрядную часть ЗУ (согласующие устройства, дополнительные разряды накопителя) или снижение частоты обращения к запоминающему устройству, которое связано с дополнительными затратами времени на формирование кода адреса для записи (считывания) избыточных разрядов, информационного кода. Наиболее близким по технической сущ ности является запоминающее устройство которое содержит накопитель, дешифратор адреса, датчик кода адреса с выходами, подключенными непосредственно к коммутатору и датчик кода адреса с выходами, подключенными к коммутатору через инверторы (датчик кода адреса с прямыми и HHBepciibiMH выходами), коммутатор (первая и вторая группы элементов И), схем выделения сигналов (третья и четвертая группы элементов И), элементы ИЛИ, делители частоты, схемы формирования контрольных символов f2j. Недостаток этого устройства - ограниченные возможности для случая записи информационного кода с числом ра йдов, превышающим число разрядов накопителя. Цель изобретения- расширение области применения устройства при условии минимальных временных и аппаратурных затрат за счет записи информационного кода с числом разрядов, превышающим число разрядов накопителя.

Поставпенная ЦЕПЬ достигается тем, что в запоминаюпдее устройство содержащее накопитель, одни из входов которого соединены с выходами элементов , другие входы накопителя соединены с выходами дешифратора адреса, -входы которого подключены к вых:одам первых и вторых элементов И, первые входы которых соединены с выходами датчика кода адреса, выходы накопителя соединены с первыми входами третьих и четвертых элементов И, вторые входы третьих элементов И соединены с шиной опроса и с вторыми входами первых элементов И, третьи входы третьих элементов И и вторые входы четвертых элементов И соединены с шнной разрешения считьтания, выходы третьих и- четвертых элементов И соединены с выходами устройства, шину разрешения записи и ин- . формашюнные шины, введены элемент зaдep кки, пятые и шестые элементы И,

выходы которых подключены к входам элементов ИЛИ, первые входы пятых и шестых элементов И соединены с информационными шинами, вторые входы - с шиной разрешения записи, третьи входы пятых элементов И соединены с шиной опроса и входом элемента задергкки, вы.ход которого соединен с вторыми входами вторых элементов И, третьими входами четвертых и шестых элементов И.

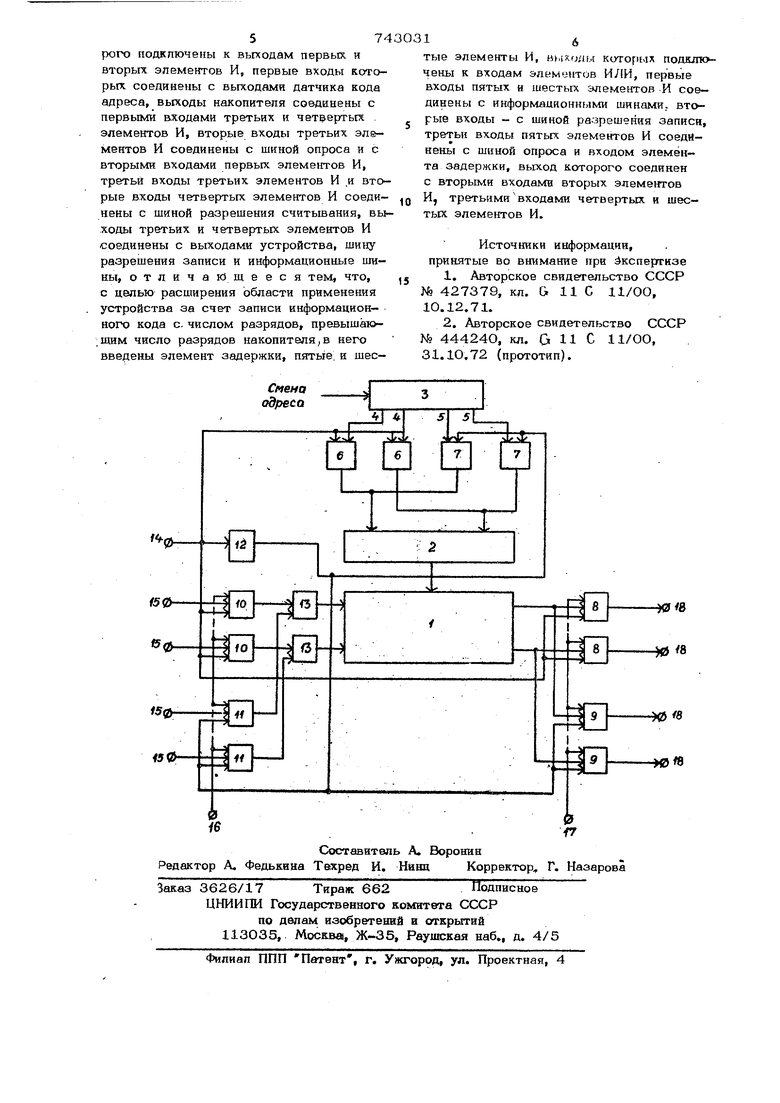

Сущность изобретения, поясняется чер тежом.

Устройство содержит накопитель 1, дешифратор 2 адреса, датчик 3 кода адреса, имеющий прямые выходы 4 и инверсные выходы 5, первые, вторые,

третьи, четвертые пятые и шестые элементы 6-11 И, элемент 12 задержки, элементы 13 ИЛИ, шину 14 опроса, информационные шины 15, шину 16 разрешения записи, шину 17 .разрешения считывания и выходы 18 устройства

Устройство рабоаает следующим образом.

По сигналу смена адреса, поступающему на вход датчика 3, кода адреса, . на его выходах 4 g 5 вырабатываются соответственно прямой и инверсный коды адреса. Опрос накопителя осуществляется при поступлении сигнала опрос на шину 14. При этом накопитель опрашивается вначале по адресу, соответствующему прямому коду адреса, а затем тот же импульс опроса, задержанный элементом 12 задержки j обеспечивает опрос накопителя по инверсному коду a/jpeca, В режиме Зегпись (на шину 16 подается сигнал, разрешающий запись) одна половина Htiформационного кода, подаваемого на шины 15 и поступающая на входы элементов , по сигналу опрос записывается в накопитель по прямому коду адреса, а вторая половина информационного кода, поступающая на входы элементов И 11 по сигналу опроса, задержанного элементом 12, записывается в накопитель по инверсному коду адреса. В режиме считывание на шину 17 подается сигнал, разрешающий считывание. При этом сигнал опрос обеспечивает считывание одной половины информационного кода, записанного по прямому коду адреса, а после задержки элементом 12 также и второй половины информационного кода, записанного по инверсному коду адреса.

Предложенное устройство обладает большими возможностями. Оно обеспечивает хранение как информационного кода с числом- разрядов, не превышающим число разрядов накопителя, так и информационного кода, число разрядов которого превышает (не более чем в 2 раза) число разрядов накопителя. При этом емкость накопителя используется эффективно.

Полученный эффект достигается минимальными аппаратурными и временными затратами. Не требуется значительные аппаратурные затраты на дополнительные разрядные блоки согласования входов и выходов устройства с входными и выхоными шинами накопителя, имеющими место при увеличении рйзрядов накопителя для записи многоразрядного кода, не требуется существенных временных затрат для смены кода адреса в датчике кода адреса, имеющих место при использовании малоразрядного накопителя для записи многоразрядного информационного код путам деления информационного кода на части и записи каждой части по вйовь сформированному коду адреса в датчика кода адреса.

Формула изобретения

Запоминающее устройство, содержащее накопитель, одни из входов которого соединены с выходами элементов ИЛИ, другие входы накопителя соединены с выходами дешифратора адреса, входы кото

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU964730A1 |

| Буферное запоминающее устройство | 1977 |

|

SU711631A1 |

| Запоминающее устройство | 1981 |

|

SU1010653A1 |

| Буферное запоминающее устройство | 1980 |

|

SU888202A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Магнитное оперативное запоминающее устройство | 1983 |

|

SU1129654A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

Авторы

Даты

1980-06-25—Публикация

1978-03-03—Подача