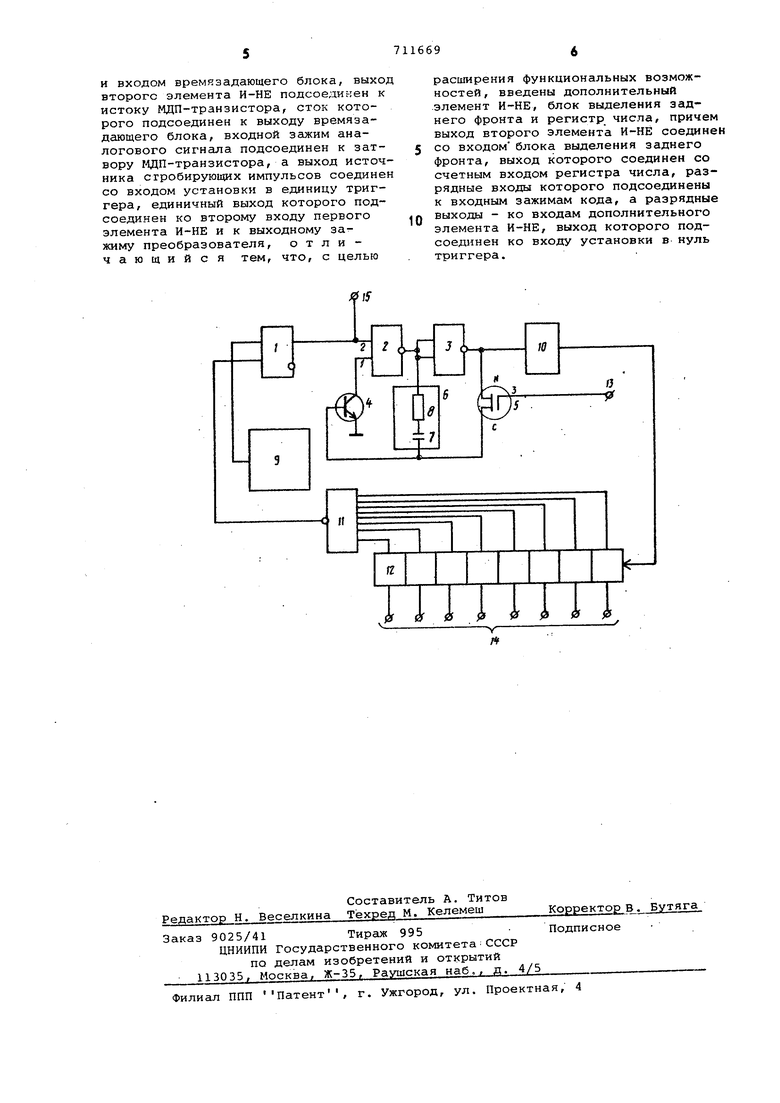

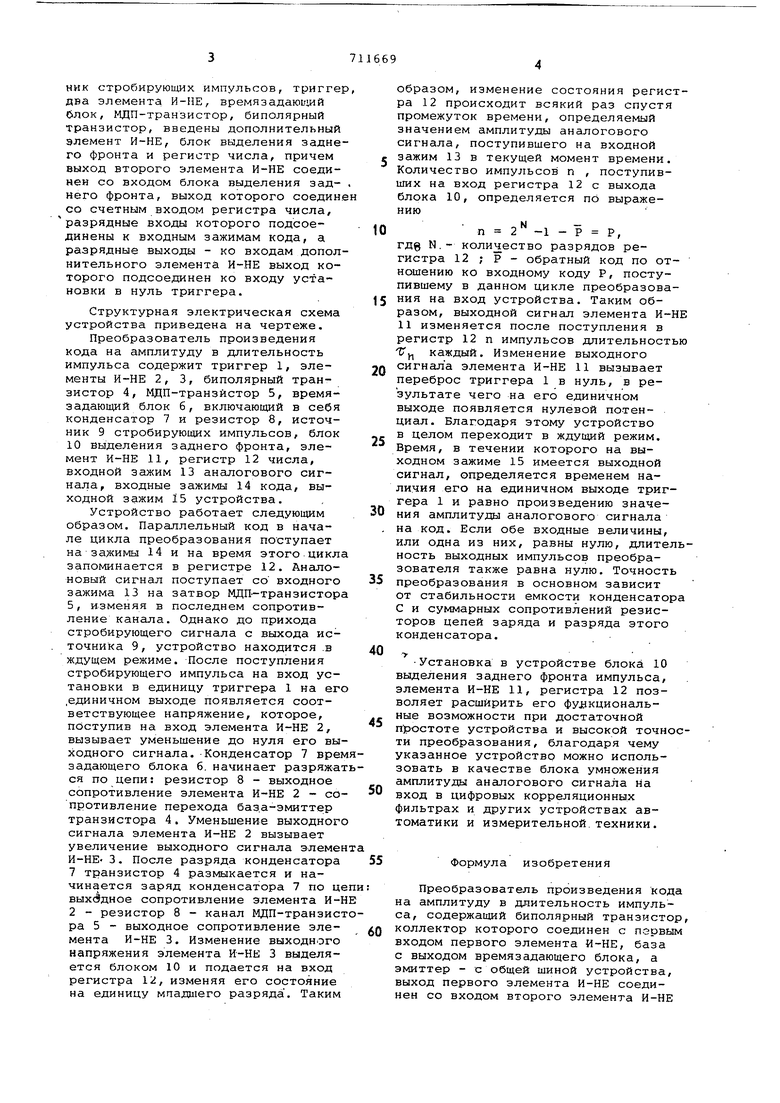

Изобретение относится к цифровой измерительной технике. Известен преобразователь произведения кода на амплитуду в длитель ность импульса , в состав которого входят перемножгиощие ячейки с запоминанием, которые производят перемножение двоичного кода, поступающего с соответствующего выхода сдвигающего регистра, на амплитуду аналогового сигнала, поступающего выхода преобразователя код-аналог, и содержат перекидные ключи, регистивные делители типа R - 2R и запоминающий конденсатор. Однако, точность работы такого устройства невысока, что ограничив ет область его применения. Известен также преобразователь амплитуды сигнала в длительность И1 ульса, содержащий источник синх роимпульса, триггер, МДП-транзисто два элемента И-НЕ, времязадающую цепочку и биполярный транзистор, коллектор которого соединен с одни из входов первого элемента И-НЕ, б за - с времязадающей цепочкой, а эмиттер - с общей шиной, выход пер вого элемента И-НЕ подсоединен ко входам второго элемента И-НЕ и к времязадающей цепочке, затвор МДП-транзистора подсоединен ко входному зажиму преобразователя,, а исток с одной стороны - к базе биполярного транзистора, а с другой ко входу второго элемента И-НЕ и ко входу установки в нуль триггера, вход установки в единицу которого подсоединен к выходу источника стробирующих импульсов, а единичный выход - к выходному зажиму преобразователя и к первым входам первого элемента И-НЕ. Однако указанный преобразователь амплитуды сигнала в длительность импульса не позволяет непосре.цственно получить длительность выходного импульса, пропорциональную произведению амплитуды аналогового сигнала на двоичный код, что ограничивает функциональные возможности устройства. Целью настоящего изобретения является расширение функциональных возможностей устройства. Указанная цель достигается тем, что в преобразователь произведения кода на амплитуду в длительность импульса, содержащий источник стробирующих импульсов, триггер два элемента И-НЕ, времязадаюид1й блок, МДП-транзистор, биполярный транзистор, введены дополнительный элемент И-НЕ, блок выделения заднего фронта и регистр числа, причем выход второго элемента И-НЕ соединен со входом блока выделения заднего фронта, выход которого соедине со счетным входом регистра числа, разрядные входы которого подсоединены к входным зажимам кода, а разрядные выходы - ко входам дополнительного элемента И-НЕ выход которого подсоединен ко входу установки в нуль триггера. Структурная электрическая схема устройства приведена на чертеже. Преобразователь произведения кода на амплитуду в длительность импульса содержит триггер 1, элементы И-НЕ 2, 3, биполярный транзистор 4, МДП-транзйстор 5, времязадающий блок 6, включающий в себя конденсатор 7 и резистор 8, источник 9 стробирующих импульсов, блок 10 выделения заднего фронта, элемент И-НЕ 11, регистр 12 числа, входной зажим 13 аналогового сигнала, входные зажимы 14 кода, выходной зажим 15 устройства. Устройство работает следующим образом. Параллельный код в начале цикла преобразования поступает на зажимы 14 и на время этого.цикл запоминается в регистре 12. Аналоновый сигнал поступает со входного зажима 13 на затвор МДП-транзистор 5, изменяя в последнем сопротивление канала. Однако до прихода стробирующего сигнала с выхода источника 9, устройство находится .в ждущем режиме. После поступления стробирующего импульса на вход установки в единицу триггера 1 на ег .единичном выходе появляется соответствующее напряжение, которое, поступив на вход элемента И-НЕ 2, вызывает уменьшение до нуля его вы ходного сигнала. Конденсатор 7 вре задающего блока 6. начинает разряжа ся по цепи: резистор 8 - выходное сопротивление элемента И-НЕ 2 - со противление перехода баз.а-эмиттер транзистора 4. Уменьшение выходног сигнала элемента И-НЕ 2 вызывает увеличение выходного сигнала элеме И-НЕ- 3. После разряда конденсатора 7 транзистор 4 размыкается и начинается заряд конденсатора 7 по ц сопротивление элемента И2 - резистор 8 - канал МДП-транзис ра 5 - выходное сопротивление элемента И-НЕ 3. Изменение выходного напряжения элемента И-НЕ 3 выделяется блоком 10 и подается на вход регистра 12, изменяя его состояние на единицу мпадщего разряда . Таким образом, изменение состояния регистра 12 происходит всякий раз спустя промежуток времени, определяемый значением амплитуды аналогового сигнала, поступившего на входной зажим 13 в текущей момент времени. Количество импульсов п , поступивших на вход регистра 12 с выхода блока 10, определяется по выражениюп Р, гдй N.- количество разрядов регистра 12 ; Р - обратный код по отношению ко входному коду Р, поступившему в данном цикле преобразования на вход устройства. Таким образом, выходной сигнал элемента И-НЕ 11 изменяется после поступления в регистр 12 п импульсов длительностью Tj каждый. Изменение выходного сигнала элемента И-НЕ 11 вызывает переброс триггера 1 в нуль, в результате чего на его единичном выходе появляется нулевой потенциал. Благодаря этому устройство в целом переходит в ждущий режим. Время, в течении которого на выходном зажиме 15 имеется выходной сигнал, определяется временем наличия его на единичном выходе триггера 1 и равно произведению значения амплитуды аналогового сигнала на код. Если обе входные величины, или одна из них, равны нулю, длительность выходных импульсов преобразователя также равна нулю. Точность преобразования в основном зависит от стабильности емкости конденсатора С и суммарных сопротивлений резисторов цепей заряда и разряда этого конденсатора. Установка в устройстве блока 10 выделения заднего фронта импульса, элемента И-НЕ 11, регистра 12 позволяет расширить его фу 1кциональные возможности при достаточной п зостоте устройства и высокой точности преобразования, благодаря чему указанное устройство можно использовать в качестве блока умножения амплитуды аналогового сигнала на вход в цифровых корреляционных фильтрах и других устройствах автоматики и измерительной, техники. Формула изобретения Преобразователь произведения кода на амплитуду в длительность импульса, содержащий биполярный транзистор, коллектор которого соединен с парвым входом первого элемента И-НЕ, база с выходом времязадающего блока, а эмиттер - с общей шиной устройства, выход первого элемента И-НЕ соединен со входом второго элемента И-НЕ

и входом времязадающего блока, выход второго элемента И-НЕ подсоединен к истоку МДП-транзистора, сток которого подсоединен к выходу времяэадающего блока, входной зажим аналогового сигнала подсоединен к затвору МДП-транзистора, а выход источника сгробирующих импульсов соединен со входом установки в единицу триггера, единичный выход которого подсоединен ко второму входу первого элемента И-НЕ и к выходному зажиму преобразователя, отличающийся тем, что, с целью

расширения функциональных возможностей, введены дополнительный элемент И-НЕ, блок выделения заднего фронта и регистр числа, причем выход второго элемента И-НЁ соединен со входом блока выделения заднего фронта, выход которого соединен со счетным входом регистра числа, разрядные входы которого подсоединены к входным зажимам кода, а разрядные выходы - ко входам дополнительного элемента И-НЕ, выход которого подсоединен ко входу установки в нуль триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь амплитуды сигнала в длительность импульса | 1976 |

|

SU586553A1 |

| ЦИФРОВОЙ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU297071A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2005 |

|

RU2303803C2 |

| Устройство для геоэлектроразведки | 1990 |

|

SU1777110A1 |

| Формирователь центра тяжести импульсов | 1986 |

|

SU1374173A2 |

| Устройство регенерации трехуровневого линейного сигнала | 1983 |

|

SU1107297A1 |

| Устройство для контроля времени установления цифроаналогового преобразователя | 1990 |

|

SU1786660A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

i 1 i И И Г

Авторы

Даты

1980-01-25—Публикация

1977-09-05—Подача