yrojuyro RS-цепь подключен ко второму ходу второго логического элемента -НЕ, третий вход которого соединен о входом дополнительного инвертоа и нулевым выходом Т-триггера, ервый вход которого через инвертор оединен с выходом первого логичесого элемента И-НЕ, а второй вход соединен со вторым входом D-триггеа, первый вход которого соединен с -входом RS-триггера.

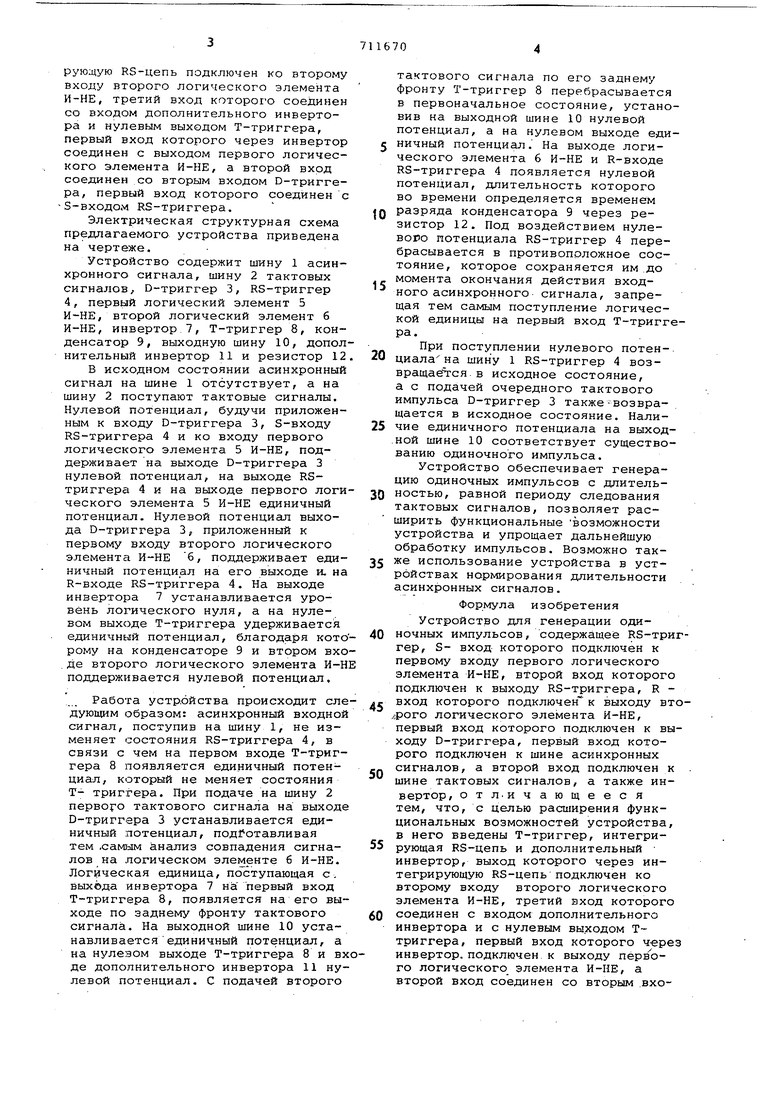

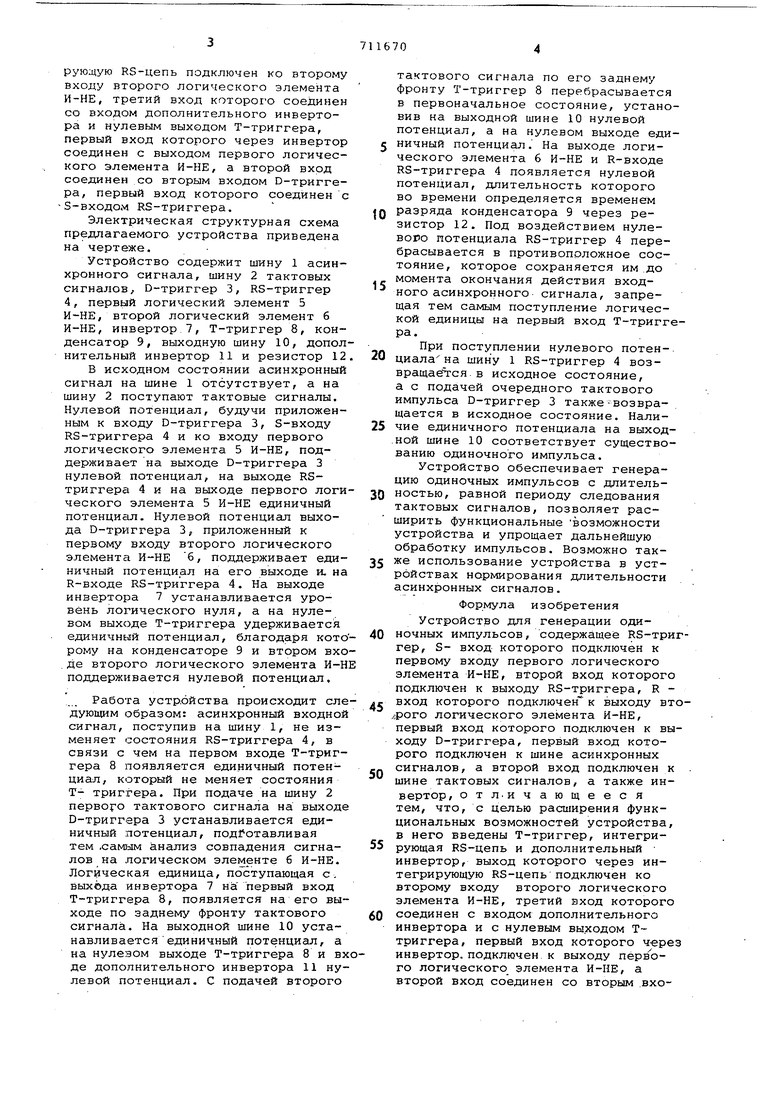

Электрическая структурная схема предлагаемого устройства приведена а чертеже.

Устройство содержит шину 1 асинхронного сигнала, шину 2 тактовых сигналов, D-триггер 3, RS-триггер 4, первый логический элемент 5 И-НЕ, второй логический элемент б И-НЕ, инвертор 7, Т-триггер 8, конденсатор 9, выходную шину 10, дополнительный инвертор 11 и резистор 12. В исходном состоянии асинхронный сигнал на шине 1 отсутствует, а на шину 2 поступают тактовые сигналы. Нулевой потенциал, будучи приложенным к входу D-триггера 3, S-входу RS-триггера 4 и ко входу первого логического элемента 5 И-НЕ, поддерживает на выходе D-триггера 3 нулевой потенциал, на выходе RSтриггера 4 и на выходе первого логического элемента 5 И-НЕ единичный потенцисш. Нулевой потенциал выхода D-триггера 3, приложенный к первому входу второго логического элемента И-НЕ б, поддерживает единичный потенциал на его выходе и. на R-входе RS-триггера 4. На выходе инвертора 7 устанавливается уровень логического нуля, а на нулевом выходе Т-триггера удерживается единичный потенциал, благодаря которому на конденсаторе 9 и втором входе второго логического элемента И-НЕ поддерживается нулевой потенциал.

Работа устройства происходит следующим образом: асинхронный входной сигнал, поступив на шину 1, не изменяет состояния RS-триггера 4, в связи с чем на первом входе Т-тритгера 8 появляется единичный потенциал, который не меняет состояния Т- триггера. При подаче на шину 2 первого тактового сигнала на выходе D-триггера 3 устанавливается единичный потенциал, подготавливая тем .самым анализ совпадения сигналов на логическом элементе б И-НЕ. Логическая единица, поступающая с. выхода инвертора 7 на; первый вход Т-триггера 8, появляется на его выходе по заднему фронту тактового сигнала. На выходной шине 10 устанавливается единичный потенциал, а на нулеэом выходе Т-триггера 8 и входе дополнительного инвертора 11 нулевой потенциал. С подачей второго

тактового сигнала по его заднему фронту Т-триггер 8 перебрасывается в первоначальное состояние, установив на выходной шине 10 нулевой потенциал, а на нулевом выходе единичный потенциал. На выходе логического элемента 6 И-НЕ и R-входе RS-триггера 4 появляется нулевой потенциал, длительность которого во времени определяется временем разряда конденсатора 9 через резистор 12. Под воздействием нулевого потенциала RS-триггер 4 перебрасывается в противоположное состояние, которое сохраняется им до момента окончания действия входного асинхронного сигнала, запрещая тем самым поступление логической единицы на первый вход Т-триггера.

При поступлении нулевого потенциала на шину 1 RS-триггер 4 возвращаеТся. в исходное состояние, а с подачей очередного тактового импульса D-триггер 3 также-возвращается в исходное состояние. Наличие единичного потенциала на выход.ной шине 10 соответствует существованию одиночного импульса.

Устройство обеспечивает генерацию одиночных импульсов с длительностью, равной периоду следования тактовых сигналов, позволяет расширить функциональные возможности устройства и упрощает дальнейшую обработку импульсов. Возможно также использование устройства в устройствах нормирования длительности асинхронных сигналов.

Формула изобретения Устройство для генерации одиночных импульсов, содержащее RS-тригер, S- вход которого подключен к первому входу первого логического элемента И-НЕ, второй вход которого подключен к выходу RS-триггера, R вход которого подключен к выходу вт,.;рого логического элемента И-НЕ, первый вход которого подключен к выходу D-триггера, первый вход которого подключен к шине асинхронных сигналов, а второй вход подключен к шине тактовых сигналов, а также инвертор, отл.ичающееся тем, что, с целью расширения функциональных возможностей устройства в него введены Т-триггер, интегрирующая RS-цепь и дополнительный инвертор, выход которого через интегрирующую RS-цепь подключен ко второму входу второго логического элемента И-НЕ, третий вход которого соединен с входом дополнительного инвертора и с нулевым выходом Т триггера, первый вход которого ч-ере инвертор, подключен к выходу пёрвого логического элемента И-НЕ, а второй вход соединен со вторым входом D-триггера, первый вход которого соединен с S-входом RS-триггера.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 528693, кл. Н 03 К 3/78, 15.09.76

2.Авторское свидетельство СССР

№ 501470, кл. Н 03 К 3/78, 30.01.76,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения одиночного импульса | 1989 |

|

SU1621147A1 |

| Формирователь одиночного импульса | 1980 |

|

SU892677A2 |

| Регистр | 1981 |

|

SU1024989A1 |

| Формирователь одиночных импульсов | 1978 |

|

SU999148A1 |

| Формирователь синхроимпульсов | 1981 |

|

SU951669A1 |

| Фазоимпульсный преобразователь | 1989 |

|

SU1691947A1 |

| Устройство для выделения одиночного импульса | 1978 |

|

SU744935A1 |

| Устройство для выделения одиночных импульсов | 1984 |

|

SU1213531A1 |

| Формирователь одиночных импульсов | 1985 |

|

SU1283955A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834548A1 |

Авторы

Даты

1980-01-25—Публикация

1977-09-08—Подача