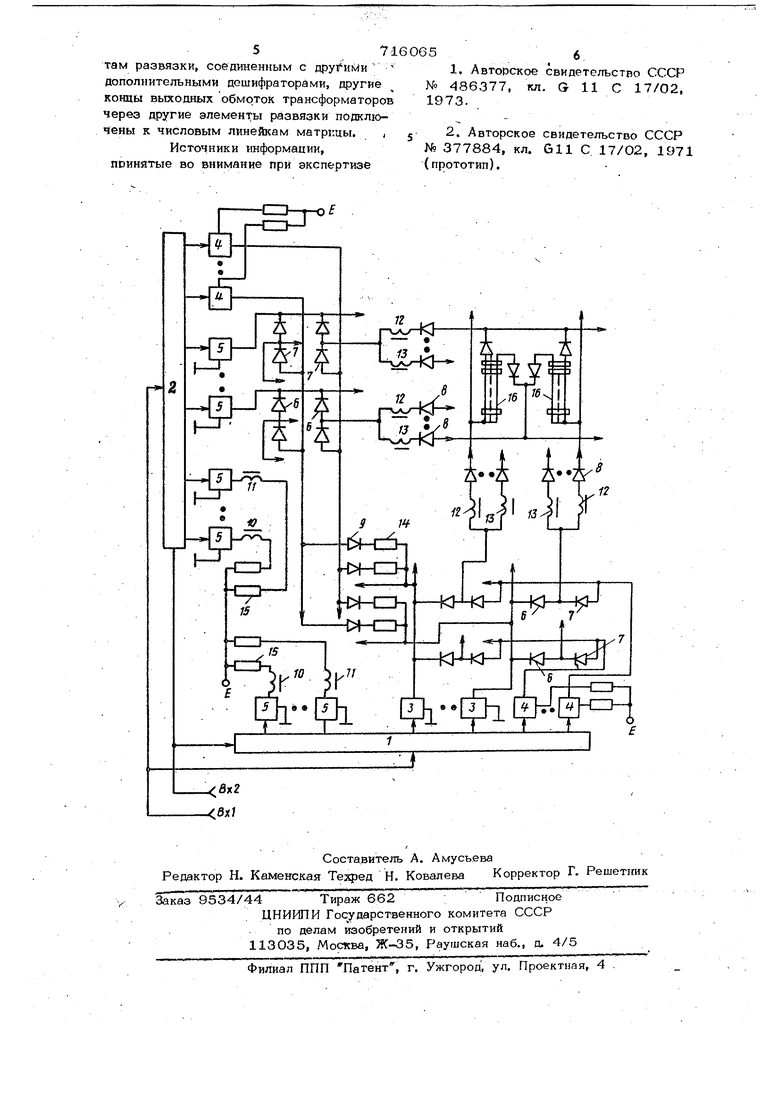

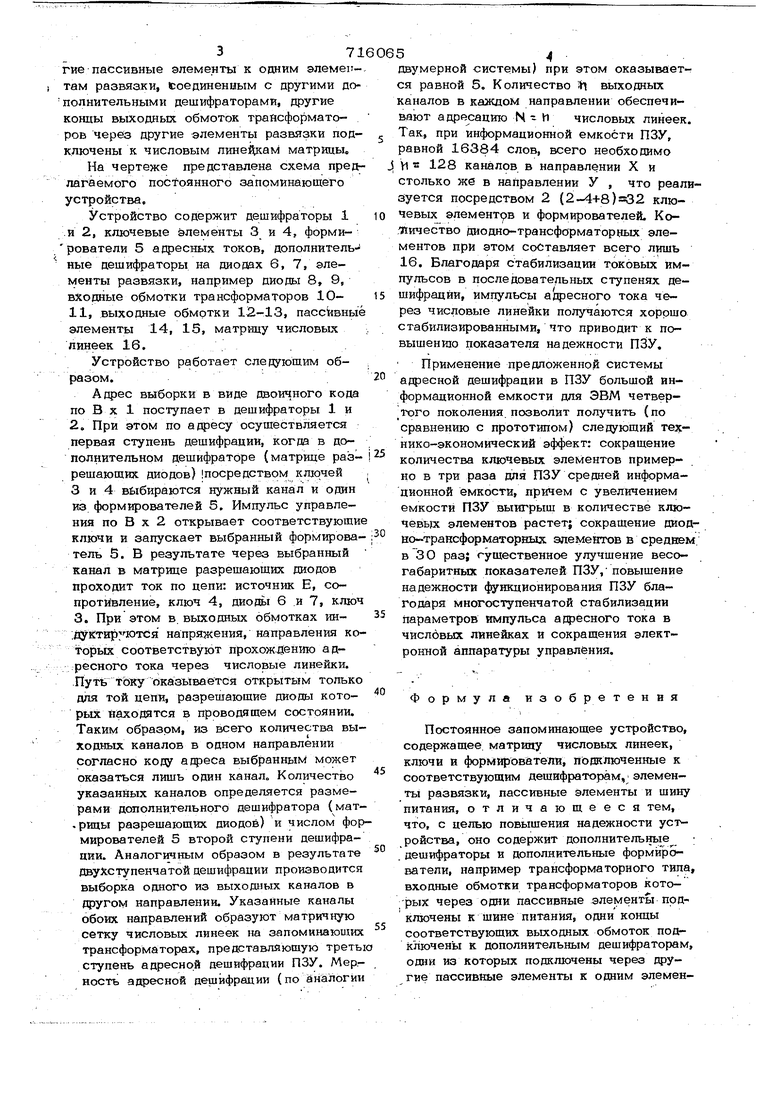

(54) ПОСТОЯ1ННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО гие пассивные элементы к одаим элемеитам развязки, Соединенным с другими дополнительными дешифраторами, другие концы выходных обмоток трайсформа торов через другие элементы развязки подключены к числовым матрицы На чертеже представлена схема пред лагаемого постоянного запоминающего устройства. Устройство содержит дешифраторы 1 .и 2, ключевые элементы 3 и 4, формирователи 5 адресных токов, дополнительные дешифраторы на диодах 6, 7, элементы развязки, например диоды 8, 9, входные обмотки трансформаторов 1011, выходные обмотки 12-13, пассивны элементы 14, 15, матрвду числовьк линеек 16. Устройство работает следуюш.им образом. Ащ)ес выборки в виде двоичного кода по В X 1 поступает в дешифраторы 1 и 2.При этом по адресу осуществляется первая ступень дешифрации, когда в дополнительном дещифраторе (матрице разрешающих диодов) посредством кшочей 3 и 4 выбираются нужный канал и один из формирователей 5. Импульс управления по В X 2 открывает соответствующи ключи и запускает выбранный формирователь 5. В результате через выбранный канал в матрице разрешающих диодов проходит ток по цепи: источник Е, сопротивление, ключ 4, диояь 6 .и 7, ключ 3.При этом в. выходных обмотках ин;/5 к:тируютСя напряжения, направления которых соответствуют прохождению адресного тока через числовые линейки. .Путь току оказывается открытым только для той цепи, разрешающие диоды которых ййходзтся; в проводящем состоянии. Таким образом, из всего количества выходных каналов в одном направлении согласно KOj:; адреса выбранньтм может оказаться лишь один канал. Количест1зо указанных каналов определяется размерами дополнительного дешифратора (мат.рицы разрешающих диодов) и числом фор мирователей 5 второй ступени дешифрации. Аналогичным образом в результате двухступенчатой дешифрации производится выборка одного из выходных каналов в другом направлении. Указанные каналы обоих направлений образуют матричную сетку числовых линеек на запоминающих трансформаторах, представлйющую треть ступень адресной дешифрации ПЗУ. Мерность адресной дешифрации (по аналогии двумерной системы) при этом оказывается равной 5. Количество выходных каналов в каждом направлении обеспечивают адресацию N - И числовых линеек. Так, при информационной емкости ПЗУ, равной 16384 слов, всего необходимо VI « 128 каналов в направлении X и столько жб в направлении У , что реализуется посредством 2 {2-4+8)«32 ключевых элемент9в и формирователей. Ко,71ичество диодно-трансформаторных элементов при этом Составляет всего лишь 16. Благодаря стабилизации токовых импульсов в после доватедьных ступенях дешифрации, импульсы адресного тока через числовые линейки получаются хорошо стабилизированными, что приводит к повышению показателя надежности ПЗУ. Применение предложенной системы адресной дешифрации в ПЗУ большой информационной емкости для ЭВМ четвер того поколения позволит получить (по сравнению с прототипом) следующий технико-экономический эффект: сокращение количества ключевых элементов примерно в три раза для ПЗУ средней информационной емкости, причем с увеличением емкости ПЗУ выигрыш в количестве клюЧевьрс элементов растет; сокращение диодво-трансф(фматорйых элементов в среднем, в 30 раз; гущественное улучшение весогабаритных показателей ПЗУ, повышение надежности 4ункционирования ПЗУ благодаря многоступенчатой стабилизации параметров импульса адресного тока в числовых линейках и сокращения электронной аппаратуры управления. Формула изобретения Постоянное запоминающее устройство, содержащее, матрицу числовых линеек, ключи в формирователи, подключенные к соответствующим дещифраторам, элементы развязки, пассивные элементы и шину питания, отличающееся тем, что, с целью повышения надежности усгройства, оно содержит дополнительные ; дешифраторы и дополнительные формйрователи, например трансформаторного типа, входные обмотки трансформаторов кото- -рых через одни пассивные элементы прдключены к шине питания, одни концы соответствующих выходных обмоток подключены к дополнительным дешифраторам, одни из которых подключены через рругие пассивные элементы к одним элемен

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| ПРОГРАММНОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛИТЕЛЬНОЙМАШИНЫ | 1969 |

|

SU254204A1 |

| Трансформаторное постоянное запо-МиНАющЕЕ уСТРОйСТВО | 1979 |

|

SU841048A1 |

| Постоянное запоминающее устройство | 1972 |

|

SU466551A1 |

| КОММУТАТОР КООРДИНАТНЫХ ТОКОВ | 1966 |

|

SU186198A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU750562A1 |

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1310901A2 |

| Трансформаторное постоянное запоминающее устройство | 1974 |

|

SU577566A1 |

| Запоминающее устройство | 1973 |

|

SU444239A1 |

Авторы

Даты

1980-02-15—Публикация

1976-12-07—Подача