(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАШИ ВЫЧИСЛИТЕЛЬНОЙ

ОЙСГГБМЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации системыОбМЕНА иНфОРМАциЕй | 1979 |

|

SU847310A1 |

| Устройство для сопряжения цифровой вычислительной машины с общей магистралью | 1980 |

|

SU907536A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1982 |

|

SU1062681A2 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU940148A1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

| Устройство для расчета сетевыхгРАфиКОВ | 1979 |

|

SU851417A1 |

| Вычислительное устройство для решения задач сетевого планирования | 1978 |

|

SU750503A1 |

| Устройство для синхронизации вычис-лиТЕльНОй СиСТЕМы | 1978 |

|

SU809132A1 |

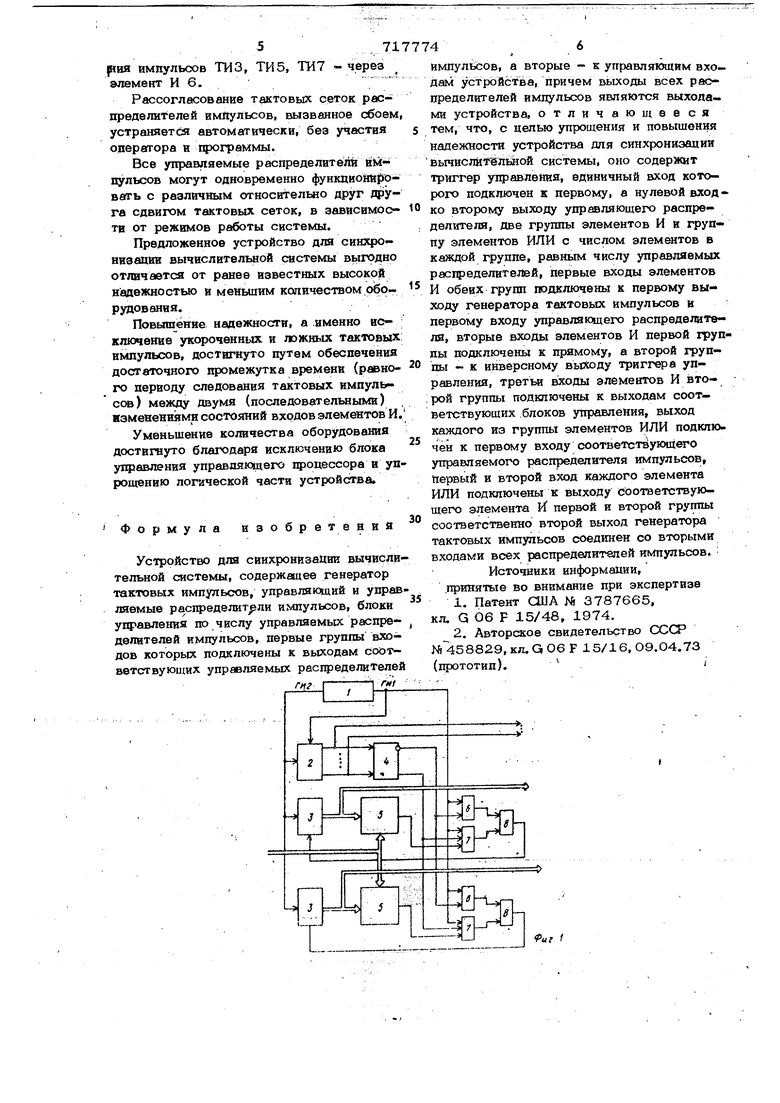

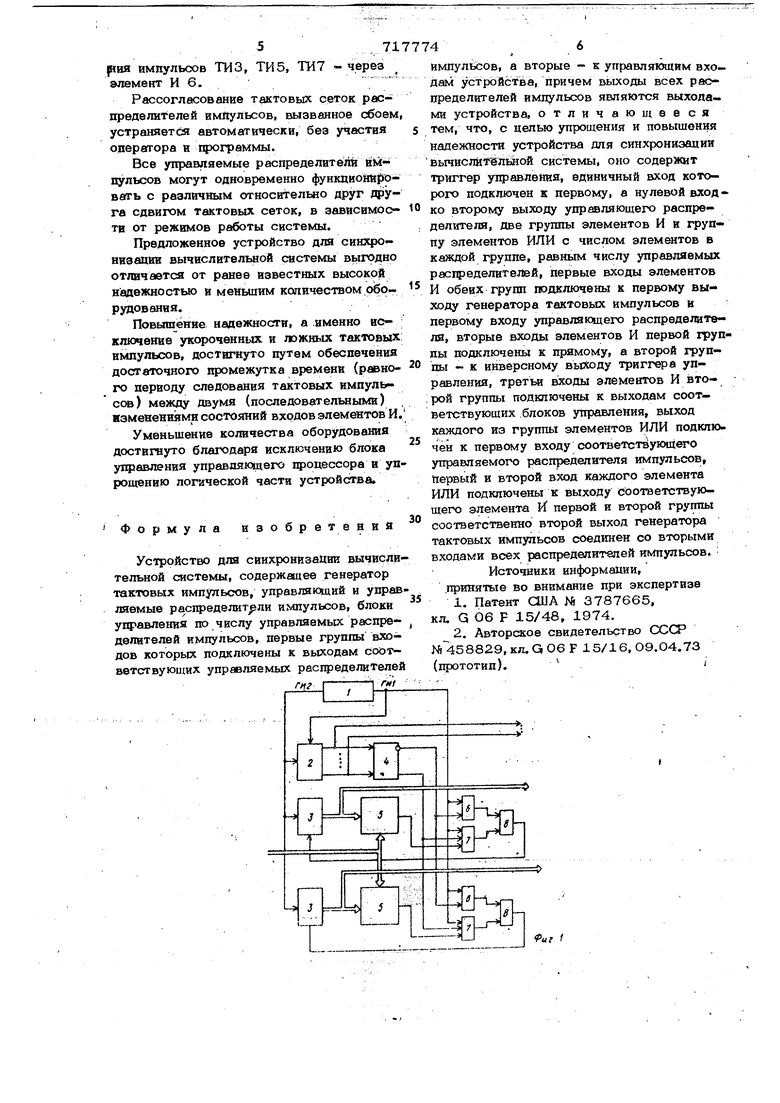

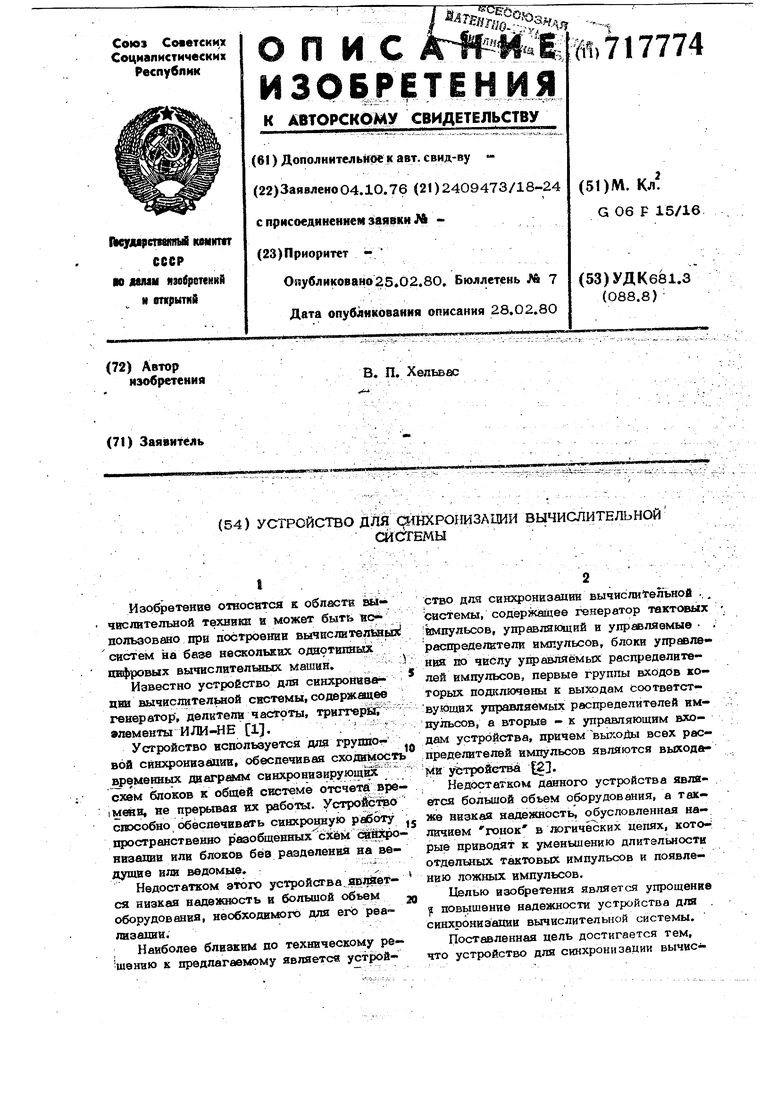

Изобретение относится к области вычислительной техники и может быть 1яо пользовано при построении вычисли те лшЦ систем на базе нескольких одаотвпньлх цифровых вычислителыодх машин. Известно устройство для синхронивегции вычислительной системы, содержащее генератор , делители частоты, трнггерйй влементы ИЛИ-НЕ 1.i ; v Устройство используется для грушювой синхронизации, обеспечивая сходимост еменных щегреми синхронизирующш схем блоков к общей системе отсчета вре 1мши, не прерывая их работы. Устройстео способно обеспечивеггь синхроцную работу пространственно рааобщенных сзсем низаши или блоков без р @деления на ведущие или ведомые.t Недостатком этого устройства Я15ляет- ся низкая надежность и большой объем оборудования, необходимого для его реализации. Наиболее близким по техническому ре шению к предлагаемому является устройство для синхронизации вычисли епьной .. системы, содержащее генератор тактовых :ИМпульсов, управляющий и управляемые . распределители импульсов, блоки управления по числу управляемых распределителей импульсов, первые группы входов которых подгслючены к выходам ьоответствующих управляемых распределителей импульсов, а вторые - к управляющим входам устройства, причем выхойы всех распределителей импульсов являются выходами устройства J. Кедостатком данного устройства является объем оборудования, а также низкая надежность, обусловленная наличием гонок в логических цепях, которыв приводят к уменьшению длительности отдельных тактовых импульсов и появлению ложных импульсов. Целью изобретения является упрощение f повышение надежности устройства для . синхронизации вычислительной системы. Поставленная цель достигается тем, что устройство для синхронизации вычис.. 3 71 лительной Системь содержит триггер упрйвления/единичный Ё сбдкЪ1 орЬ1ЧУ Шйключен к первому, а нулевой вход - ко Ёторому выходу управляющего распределителя, две группы элементов И и группу элементов ИЛИ с числом элементов в каж дой группе, равнймчислу управляемых распределителей, первые вхбдь эле1лёнтов И обеих групп подключены к п ервому выходу генератора та ктовых импульсов и пер jBOKiy упраепяющёгЬ рёспреде(ййтеля, вторые входы элементов И первой группы Евэдключены к прямому, а второй группы к инверсному выходу триггера управления, третьи входы элементов И второй группы подключены к выходам соответствующих блоков управления, выход каждого из групч пы элементов ИЛИ подключен к первому входу оэответствующего упрайпяемого распределителя импзшьсов, первый и . второй вход каждого элемента ИЛИ под ключены к выходу cooTseTcTByiouiefo элемента И первой и второй группы соответственно, второй выход генератора тактовых импулызов соединен со вторыми входами всех расгфё делите лей импульсов. На фиг. 1 предсггавлена функциональная схема устройства для синхронизации вычислительнрй системы, на фиг. 2 - вйзможная схема блока управления; на фиг. 3 временная диаграмма устройства. Устройство (см. фиг. 1) содержит генератор тактовых импзшьсов 1, двухтакт.ный управляющий .рае1фёйёШ ёль ийпульсов 2, двухтактные управляемые распре. делители импульсов 3, триггер управления 4, блоки угфавления 5, элементы И 6 первой группы, элементь И 7 второй группы, группу элементов ИЛИ 8. Каждый блок управления 5 (см. фиг. 2) содержит элементы И 9-16, ИЛИ 17, 18 и триггер 19. Устройство работает следующим образом. Генератором 1 тактовых импульсов фор Мйруются две сдвинуть1е пруг относительно друг;а на 1/2 периода серии тактовых импульсов ГИ1 и ГИ2 (см. фиг. 3). Серия импульсов ГИ2 поступает На входы всех распределителей 2, 3 икшульсов. Серия импульсов ГИ1 поступает на вход рас пределителя 2 иигогльсов непбЬрёдбт вённо а на Bxbjihi распределителей 3 б1МПульсов чёрез лозтвческие цепи на элеме йгах И 6, 7, ИЛИ 8. Поступление серии имгцгльсов nil на входы распределителей импульсов управляется блоками 5 управления и триг гером 4. Рассмотрим работу устройства на примере синхронизации одного из распределителей 3 импульсов с распределителем 2 (рассматривается случай совпадения тактовых импульсов обоих распределителей). Все распределители импульсов формируют четные импульсы из серии ГИ2, а нечетные - из ГИ1, причем, если после подачи на распределитель импульсов, импульса ГИ2 .и формирования соответствующего чёткого Шл&уУ1&с Ъпё1 кяам импульс ГИ1 на него не поступает, то при поступлении очередного импульса ГИ2 на выходе распределителя формируется тот же. четный выходной импульс. Распределителем 2 импульсов из входных серий импульсов ГИ1 и ГИ2 формируются восемь выходных сигналов ТИ1-.ТИ85. как это показано на временной диаграмме (cM. фиг. 3). Два из них (в рассматрива.емом случае ТИ8 и ТИ2) подаются на единичный и нулевой входы триггера, на (Выходах которого формируются стробы (8-2). Допустим, что в момент, когда подана |команда на синхронизацию распределите,лей импульсов, они работали таким обра|зом, что сигнал ТИ8 распределителя 2 совпадает с сигналом ТИ4 раснределите ля 3, как это показано на временной диаграмме. Формирование строба 8-2 в данном случае обеспечивается блоком управления 5. После того, как распределителем 3 будет сформирован импульс ТИ4, сигналом с нулевого выхода триггера 4 и сигналом с выхода блока управления 5 будет заблокирована подача на этот распределитель импульса ГИ1, и при поступлении следующего импульса ГИ2 на его вы;х.оде появится повторно импульс ТИ4, после чего сниМаЪтся блокировка импульсов ГИ1. После формирования импульса ТИ 2 повторяется блокировка импульсаГИ1, повторно выдается импульс ТИ2, который уже совпадает во времени с импульсом ТИ2 распределителя 2, т.е. оба распределителя импульсов, начиная сэтого момента (на временной диаграмме указан стрелкой), работают синхронно. При синхроцной работе распределителей импульсов стробы с нулевого выхода триггера управления 4 и с выхода блока управления 5 совпадают во времени, но различаются по полярности. Это обеспечивает прохождение импульсов ГИ1 на вход распределителя 3 для формирования импульсов ТИ1 через элемент И 7, а для формирова5.71 рия импульсов ТИЗ, ТИ5, ТИ7 через элемент И 6.-.л Рассогласование тактовых сеток распределителей имйульсов, вызванное сбоем устраняется автоматически, без участия оператора и программы. Все управляемые распределите Ш импульсов могут одновременно функдиойирговвггь с различным относительно друг друга сдвигом тактовых сеток, в зависимоетн от режимов работы системы. Предложенное устройство для синхронизации вычислител1лой системы вь1годно отличается от ранее известных высокой н:адежностью и меньшим количеством оЬо рудования. Повышение надежности, а .именно исключение укороченных и ложных тактовых импульсов, достигнуто путем обеспечения достаточного промежутка времени (равного периоду следования тактовых импуль сов) между двумя (последовательными) взмененнями состояний входов элементов И. Уменьшение количества оборудования достигнуто благодаря исключению блока управления управляющего процессора и упрощению логической части устройства. Формула изобретения Устройство для синхронизации вычислительной системы, содержацее генератор тактовых импульсов, управляющий и управ ляемые распределит;эли импульсов, блоки угфавления по числу управляемьцс распределителей импульсов, первые группы входов которых подключены к выходам соответствующих управляемых распределителей гцг I- -Vw 4 импульсов, а вторые - к управляющим входам устройства, причем выходы всех распределителей импульсов являются выходами устройства, отличающееся тем, что, с целью упрощения и повышения надежности устройства для синхронизации вычислйтёлШой системы, оно содержит триггер управления, единичный вход которого подключен к первому, а нулевой входко второму выходу управляющего распределителя, две группы элементов И и группу элементов ИЛИ с числом элементов в каждой группе, равным числу управляемых расщ)еделителей| первые входы элементов И обеих групп подключены к первому выходу генератора тактовых импульсов и первому входу управляющего распределителя, вторые входы элементов И первой группы подключены к прямому, а второй групцы к инверсному выходу триггера управлания, третьи вЬсоды элементов И второй группы подключены к выходам соот- ветствующих блоков управления, выход каждого из группы элементов ИЛИ подключен к первому входу соответствующего управляемого распределителя импульсов, Первый и второй вход каждого элемента ИЛИ подключены к выходу соответствующего элемента И первой и второй группы соответственно второй выход генератора тактовых импульсов соединен со вторыми входами всех распределителей импульсов. Источники информации, .принятые во внимание при экспертизе 1.Патент США М 3787665, кл. G Об F 15/48, 1974. 2.Авторское свидетельство СССР м458829,кп.а06Р 15/16,09.04.73 (прототип). .2-« t:jfr7«jA«, Л«./,, .-

Авторы

Даты

1980-02-25—Публикация

1976-10-04—Подача