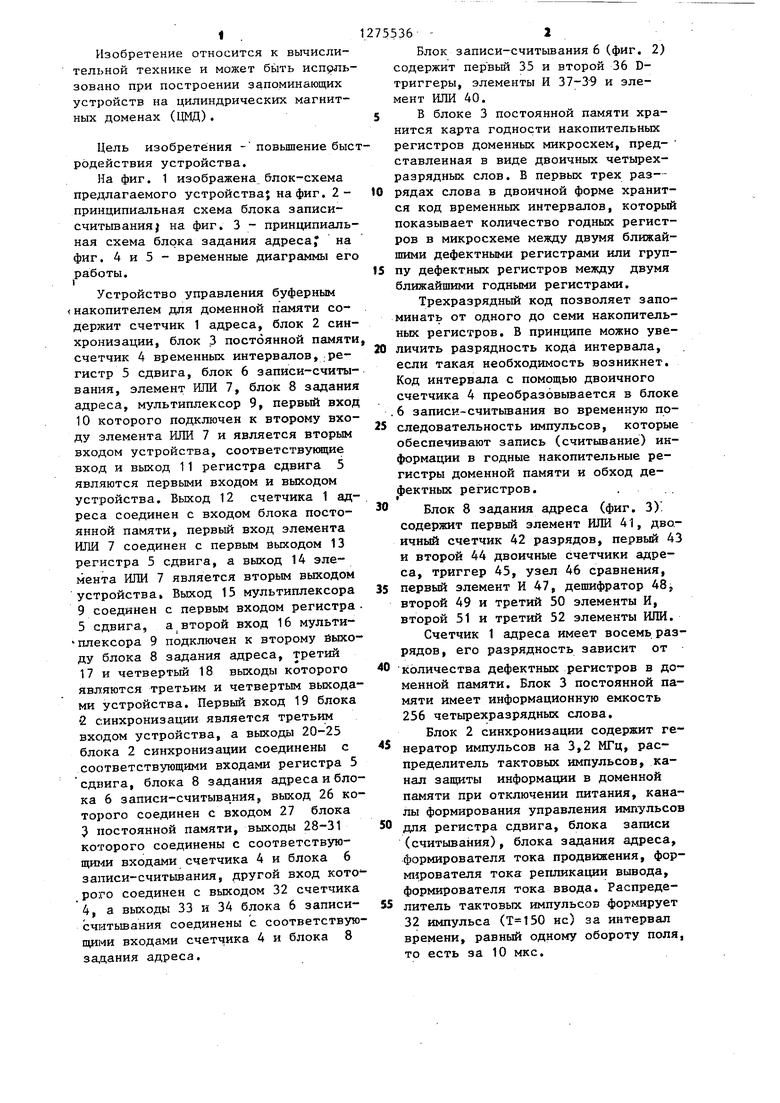

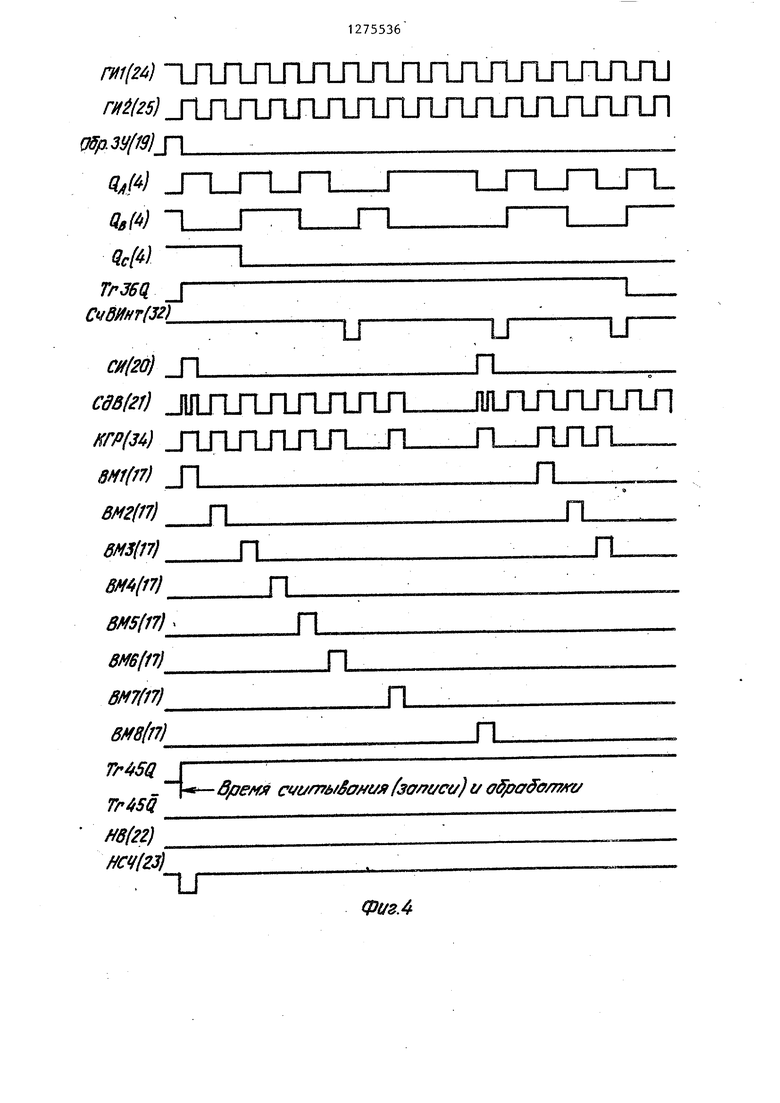

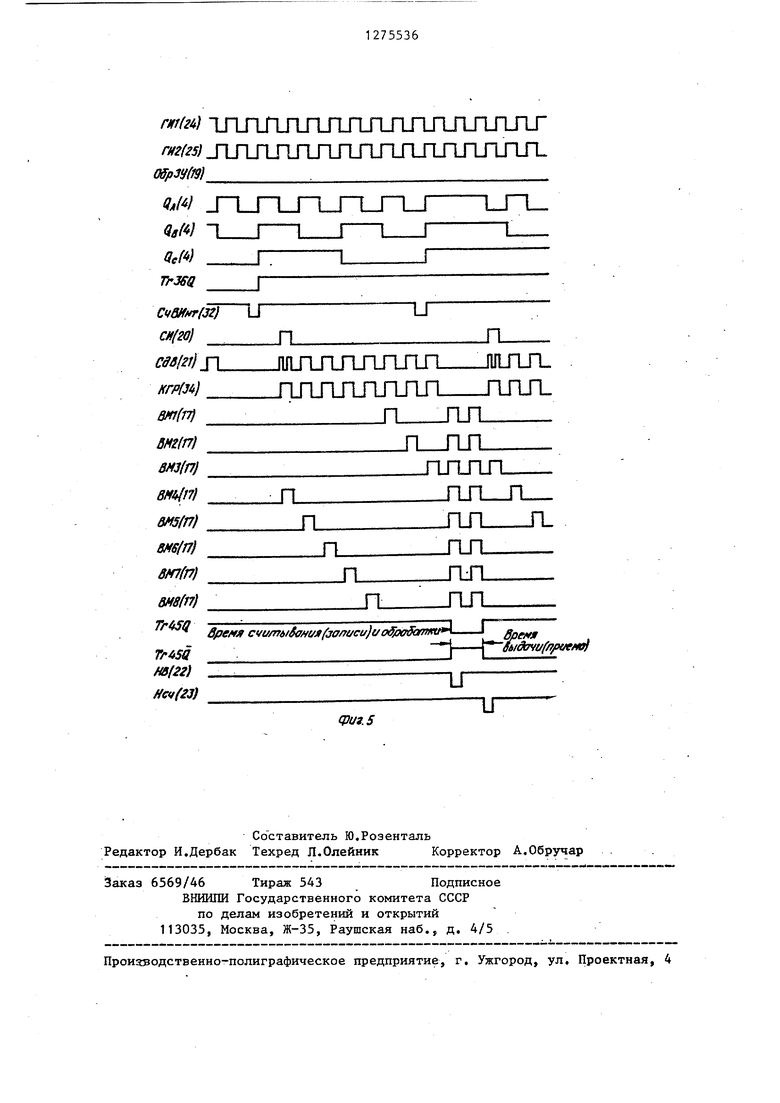

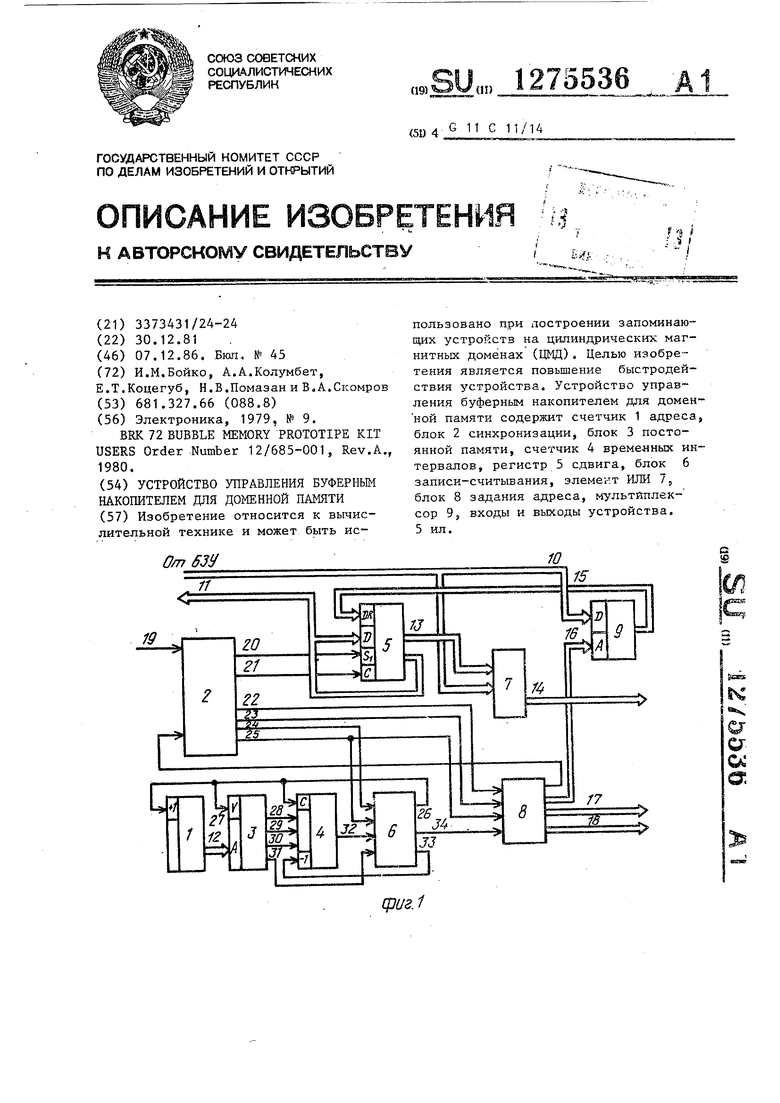

(иг.1 Изобретение относится к вычислительной технике и может быть испсрльзовано при построении запоминающих устройств на цилиндрических магнитных доменах (ЦМД). Цель изобретения -повьшение быс родействия устройства. На фиг. 1 изображена блок-схема предлагаемого устройства на фиг. 2принципиальная схема блока записисчитьшания} на фиг. 3 - принципиаль ная схема блока задания адресаJ на фиг. 4 и 5 - временные диаграммы его работы. Устройство управления буферным (накопителем для доменной памяти содержит счетчик 1 адреса, блок 2 синхронизации, блок 3 постоянной памяти счетчик 4 временных интервалов, регистр 5 сдвига, блок 6 записи-считывания, элемент ШТИ 7, блок 8 задания адреса, мультиплексор 9, первый вход 10 которого подключен к второму входу элемента ИЛИ 7 и является вторым входом устройства, соответствующие вход и выход 11 регистра сдвига 5 являются первыми входом и выходом устройства. Выход 12 счетчика 1 адреса соединен с входом блока постоянной памяти, первый вход элемента ИЛИ 7 соединен с первым йыходом 13 регистра 5 сдвига, а выход 14 элемента ИЛИ 7 является вторым выходом устройства. Выход 15 мультиплексора 9 соединен с первым входом регистра 5 сдвига, а второй вход 16 мультиплексора 9 подключен к второму выходу блока 8 задания адреса, третий 17 и четвертый 18 выходы которого являются третьим и четвертым выходами устройства. Первый вход 19 блока 2 синхронизации является третьим входом устройства, а выходы 20-25 блока 2 синхронизации соединены с соответствующими входами регистра 5 сдвига, блока 8 задания адреса и блока 6 записи-считывания, выход 26 которого соединен с входом 27 блока 3 постоянной памяти, выходы 28-31 которого соединены с соответствующими входами счетчика 4 и блока 6 записи-считывания, другой вход кото рого соединен с выходом 32 счетчика 4, а выходы 33 и 34 блока 6 записисчитьюания соединены с соответствую щими входами счетчика 4 и блока 8 за,п,ания адреса. 536 2 Блок записи-считьшания6 (фиг. 2) содержит первый 35 и второй 36 Dтриггеры, элементы И 37-3-9 и элемент ИЛИ 40. В блоке 3 постоянной памяти хранится карта годности накопительных регистров доменных микросхем, пред- ставленная в виде двоичных четырехразрядных слов. В первых трех раз- рядах слова в двоичной форме хранится код временных интервалов, который показывает количество годных регистров в микросхеме между двумя ближайщими дефектными регистрами или группу дефектных регистров между двумя ближайшими годными регистрами. Трехразрядный код позволяет запоминать от одного до семи накопительных регистров. В принципе можно увеличить разрядность кода интервала, если такая необходимость возникнет. Код интервала с помощью двоичного счетчика 4 преобразовывается в блоке 6 записи-считывания во временную прследовательность импульсов, которые обеспечивают запись (считывание) информации в годные накопительные регистры доменной памяти и обход дефектных регистров. Блок 8 задания адреса (фиг. 3), содержит первый элемент ИЛИ 41, двоичный счетчик 42 разрядов, первый 43 и второй 44 двоичные счетчики адреса, триггер 45, узел 46 сравнения, первый элемент И 47, дешифратор 48, второй 49 и третий 50 элементы И, второй 51 и третий 52 элементы ИЛИ. Счетчик 1 адреса имеет восемь разрядов, его разрядность зависит от количества дефектных регистров в доменной памяти. Блок 3 постоянной памяти имеет информационную емкость 256 четырехразрядных слова. Блок 2 синхронизации содержит генератор импульсов на 3,2 МГц, распределитель тактовых импульсов, канал защиты информахщи в доменной памяти при отключении питания, каналы формирования управления импульсов для регистра сдвига, блока записи (считьтания), блока задания адреса, формирователя тока продвижения, форМ1фователя тока репликации вывода, формирователя тока ввода. Распределитель тактовых импульсов юрмнрует 32 импульса ( не) за интервал времени, равный одному обороту поля, то есть за 10 мкс.

Блок 6 записи-считывания преобразует код карты годности регистров во временную последовательность импульсов, которые обеспечивают запись информации в доменную память, а также 5 считывание информации с доменной памяти в буферньш накопитель в соответствии с картой годности.

Устройство работает следующим образом.10

На вход 19 блока синхронизации 2 поступает импульс обращения к ЗУ (фиг, 4 и 5), который разрешает выдачу синхроимпульсов на все блоки устройства. В режиме считывания ин- 5 формации с доменной памяти и записи ее в буферный накопитель импульс Начало считьгоания (НСЧ) устанавливает в состояние 1 триггер 46, выход которого разрешает прохолсдение импуль- ю сов Выбор микросхемы (ВМ) и десятиразрядного кода адреса на буферньш накопитель. Во время действия импульса СИ восьмиразрядное слово считывается с доменной памяти и по шине 25 11 параллельно записывает :я в регистр 5 сдвига. Частота следования импульсов СИ соответствует частоте считывания информации с доменной памяти и равна 100 кГц (фиг. 4 и 5). Частота ЗО следования импульсов ГИ1 и ГИ2 равна 1 мГц. Считанное слово содержит не только записанную информацию, но и считанные с дефектных накопительных регистров ложные нули (единицы), которые в дальнейшем необходимо исключить .

Для этого с блока 3 постоянной памяти считьгеается код карты годности 40 регистров (КГР), который затем в блоке б преобразуется в последовательность импульсов КГР (34). Импульсы КГР используются в блоке 8 задания адреса для формирования сиг- 45 налов, управляющих записью информации с доменной памяти в буферный накопитель. Вьтолняется это в следующей последовательности. С блока 3 постоянной памяти считывается первьш 50 код интервала, три разряда (28, 29 и 30) которого записываются в счетчике 4 временных интервалов, а четвертый разряд (31), где хранится признак интервала, запоминается на 55 триггере 36 блока записи-считьшания, Первый интервала равен шести, признак кода интервала равен единице. Поступающие на регистр 5 сдвига (фиг. 1) импульсы СдВ (21) обеспечивают поразрядную выдачу слова на шину 13 -и запись этого слова через элемент ИЛИ 7 и шину 14 в буферный накопитель. Каждый разряд слова, который появляется нашине 13, через элементы ИЛИ 7 поступает параплельно на все входы буферного накопителя, но записьгоается код только к тот разряд на который поступил ВМ. Импульсы ВМ формируются с импульсов КГР (34) в блоке 8 задания адреса с помощью двоичного счетчика 42 разрядов и дешифратора 48. Импульсы КГР через элемент ИЛИ 40 блока 6 записи-считьшания поступают на вычитающий-.вход счетчика 4 временных интервалов и его содержание уменьшается на единицу после каждого сдвига с регистра сдвига 5 и выдачи на шину 13 одного разряда слова. Для первого кода 110 выполняется шесть сдвигов в регистре и вырабатывается в блоке 8 задания адреса шесть импульсов ВМ (ВМ1-ВМ6), которые обеспечивают запись шести разрядов первого слова в буферный накопитель. В седьмом .такте на шине 13 появляется считанньй с дефектного регистра ложный нуль. В этот момент счетчик временных интервалов устанавливается в нулевое состояние, и на его выходе появляется импульс СчВИнт которьй устанавливает триггер 35 в нулевое состояние и тем самым запрещает прохождение через элемент 38 седьмого импульса КГР (фиг. 4) на блок 8 задания адреса. На регистр 5 сдвига подается седьмой импульс СдВ ;(21), которьм обеспечивает сдвиг на один разряд5 а импульс ВМ не вырабатывается, поэтому ложный нуль с дефектного регистра не записывается в буферньш накопитель. Таким образом, производится исключение ложных нулей и соответствующее сжатие кодов . Положительный потенциал с нулевого плеча триггера 35 разрешает прохождение через элемент 37 импульса ГИ, которьм на единицу увеличивает код счетчика 1 адреса и считывает с блока 3 постоянной памяти новый ко интервала. После этого перезапись кодов из регистра 5 сдвига в буферный накопитель повторяется. Второе восьмиразрядное слово принимается в регистр 5 сдвига по второму импульсу СИ и преобразовывается предлагаемым способом в параллельный код, а затем записьгоается з буферньгл накопитель. С четвертого адреса блока постоянной пакяти считывается код импульса, равный и . и с признаком, равным нулю. Это означает, что в считанном с доменной памяти слове имеется группа (три) ложных нулей, которые необходимо исключить при записи слова в буферный накопитель. Так как признак кода интервала равен нулю, то отрицательный потенциал с единичного плеча триггера 36 запрещает прохождение импульсов КГР через схему И 38 на блок задания адреса. Поэтому импульсы ВМ не вьфабатываются изапись в буферный накопитель разрядов числа не производится (фиг.4 и 5). В это время импульсы ГИ2 через элемент И 39 и элемент ИЛИ 40 поступают на вычитакнций вход счетчика временных интервалов, уменьшая содержание его кода на единицу после каждого сдвига кода в регистре 5 сдвига. После трех сдвигов счетчик врехченных интервалов обнулйется и на его выходе появляется импульс СиВИнт, который устанавливает в нулевое состояние триггер 35, разрешающий прохождение через элемент И 38 импульса ГИ1, который увеличивает на единицу код двоичного счетчика 1 адреса и считывает с блока постоянной памяти следующий код временного интервала. Работа устройства в дальнейшем аналогично повторяется д тех пор, пока с доменной памяти не будет считана заданная страница. Ко личество слов, записываемых в буферный. накопитель, запоминается первым двоичным счетчиком 43 адреса. Вьщача информации с буферного на копителя производится синхронно со считыванием информации с доменной .памяти. После записи в буферный накопитель первых двух считанных слбв импульс НАЧАПО ВЫДАЧИ (НВ) устанав ливает в нулевое положение триггер 45,, который запрещает формирование поразрядных импульсов ВМ и разрешает подачу импульсов ГИ2 на вход элемен та 51 и вход второго двоичного счет чика 44 адреса для формирования импульсов ВМ и кода адреса, которые обеспечивают параллельную выдачу восьмиразрядных слов с буферного на копителя. В этом случае импульсы ВМ подаются параллельно на восемь разрядов буферного накопителя и обеспечивают выдачу двух восьмиразрядных слов в ЦВМ. С временной диаграммы (фиг. 5) ридно, что вьщача информации с буферного накопителя производится в калодом десятимикросекундном цикле считьтания по девятому и десятому импульсу ГИ2, После этого триггер 45 устанавливается в единичное состояние и снова продолжается считывание информации с доменной памяти и запись ее в буферный накопитель. Узел 46 сравнения предохраняет выдачу неполного слова. Выдача информации с буферного накопителя прекращается, когда код первого двоичного счетчика 43 адреса совпадает с кодом второго двоичного счетчика 44 адреса. В принципе возможно выдачу информации производить различными масси.вами в зависимости от требований конкретной системы. Формула изобретения Устройство управления буферным накопителем для доменной памяти, содержащее счетчик адреса, выход которого соединен с входом блока постоянной памяти, счетчик временных интервалов, блок синхронизации, блок заданного адреса, регистр сдвига, соответствующие вход и выход которого являются первыми входом и выходом устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит мультиплексор, элемент ИЛИ, блок записи-считывания, первый вход которого подключен к пятому выходу блока синхронизации, второй вход - к шестому выходу блока синхронизации и третьему входу блока задания адреса, третий вход - к выходу временных интервалов, четвертый вход - к четвертому выходу блока постоянной памяти, первый выход - к входам счетчкка временных интервалов, блока постоянной памяти, счетчика адреса, вто-рой выход - к четвертому входу блока задания адреса, третий выход - к пятому входу счетчика временных интервалов, второй, третий и четвертый входы счетчика временньгк интервалов подключены соответственно к nepBOMyj второму и третьему выходам блока пос71

тоянной памяти, первьй вход элемента ИЛИ подключен к первому выходу регистра сдвига, второй вхрд элемента ИЛИ - к первому входу мультиплексора и является вторым входом устройства, а выход является вторым выходом устройства, второй вход мультиплексора подключен к второму выходу блока задания адреса, а, выход - к первому входу регистра сдвига, первый вход блока синхронизации является треть24

2 7 5368

им входом устройства, .второй вход подключен к первому выходу блока задания адреса, первый и второй выходы к третьему и четвертому входам регистра сдвига, Третий и чет5вертый выходы - к первому и втотому входам блока задания адреса, третий и четвертый выходы блока задания адреса являются третьим

10 и четвертым выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Устройство для контроля памяти | 1976 |

|

SU673203A3 |

Изобретение относится к вычислительной технике и может быть 63У пользовано при построении запоминаюпщх устройств на цилиндрических магнитных доменах (ЦМД). Целью изобретения является повышение быстродействия устройства. Устройство управления буферным накопителем для доменной памяти содержит счетчик 1 адреса, блок 2 синхронизации, блок 3 постоянной памяти, счетчик 4 време«ных интервалов, регистр 5 сдвига, блок 6 записи-считывания, элемент РШИ 7, блок 8 задания адреса, мультиплексор 9, входы и выходы устройства, 5 ил. с 10

Фиг.З

aгlnJlJггLГlЛJПJl )

. 3{/ff9l П

M вМ П n 1 TrJ6q j (зг) Cffl20) П сдв121} JШJ J JlПJlГlл ППП П П П П 8М1(П) // //7;П 6MS(17)П . 4/y;yП

8M5I17} П

BM6I17)П

вМ7{17)П вМ81п) , .. HC4fZ3) и

. ct i/n7&/Sa i/ji f3a/ i/ct/) tf оф отлг/ 2 г 1 r U и П luuijnjiJTJLn П ППП П П П

гя1(2 гIlлЛJгпJIЛJlJlJ Jгjl

ги2(г5 JlJIJlJljmiJlJlJlJlJlJl

QSp3y(f9}

| Электроника, 1979, № 9 | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

Авторы

Даты

1986-12-07—Публикация

1981-12-30—Подача