(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU940148A1 |

| Устройство для синхронизации системыОбМЕНА иНфОРМАциЕй | 1979 |

|

SU847310A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1980 |

|

SU907537A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1982 |

|

SU1062681A2 |

| Устройство для сопряжения цифровой вычислительной машины с общей магистралью | 1980 |

|

SU907536A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для синхронизации вычислительной системы | 1976 |

|

SU717774A1 |

Изобретение относится к вычислительной технике и может бить :1спользовано при построении вычислительных систем на базе нескольких однотипных цифровых вычислительных машин. Язвестно устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов, распределители тактовых импульсов по числу процессоров в системе, устройства управления и первые схемы И по числу управляемых процессоров в Системе, причем выход генератора тактовых импульсов соединен с входом распределителя импульсов управляющего процессора и первыми входами первых элементов И, выходы которых соединены с входами распредлителей импульсов управляемых процессоров, группы входов устройств управления соединены с группой, выходов соответствующего распределителя импульсов, первые входы распределителей импульсов управляемых процессоров соединены с выходом соответствующего элемента И 1. Распределители импульсов управляются импульсами, поступающими с генератора тактовых импульсов на вход распределителя импульсов управляющего процессо эа непосредственно, а на входы распределителей импульсов управляемых процессоров через схемы И. Разрешение (или запрет) на прохождение тактовых импульсов на распределители импульсов управляемых процессоров формируется по состоянию соответствующего распределителя импульсов. Недостатком устройства является его низкая надежность, которая обусловлена наличием в устройстве состязаний сигналов, что приводит к уменьщепию длительности отдельных тактовых импульсов на выходах распределителей импульсов управляемых процессоров, а также к появлению ложных тактовых импульсов, которые не позволяют осуществить заданную синхронизацию распределителей импульсов. Причиной состязаний сигналов является различие во времени их прохождения по логическим цепям и через запоминающие элементы (триггеры). Наиболее близким к предлагаемому по технической сущности является устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов, .двухтактные управляющий и управляемые распределители импульсов, выходы которых

являются выходами устройства, блоки управления по числу управляемых распределителей импульсов, две группы элементов И и группу элементов ИЛИ с числом элементов в каждой группе, равным числу управляемых распределителей, выход генератора тактовых импульсов соединен со входом управляющего распределителя и с первыми входами элементов И обеих групп, вторые входы элементов первой группы подключены к выходам соответствующих блоков управления, первая группа входов которых подключена к выходам соответствующих распределителей импульсов, вторые группы входов блоков управления являются входами устройства, входы элементов ИЛИ соединены с выходами соответствующих элементов И первой и второй групп, а выходы - с соответствующими входами управляемых распределителей импульсов 2.

Устройство позволяет обеспечить заданную по программе сходимость временных диаграмм двух м более двухтактных распределителей импульсов.

Генератор тактовых импульсов формирует две серии импульсов, сдвинутых друг относительно друга на 1/2 периода. Одна из этих серий поступает на первые входы всех распределителей импульсов, другая поступоступает на второй вход управляющего распределителя имлульсов непосредственно, а на управляемые распределители импульсов через группы элементов И и ИЛИ. Из одной серии тактовых импульсов распределителями формируются четные, а из другой нечетные тактовые импульсы. Управление передачей серии импульсов на вторые входы управляемых распределителей производится соответствующими блока1ми управления на группах элементов И и ИЛИ.

Однако известное устройство пригодно только для синхронизации двухтактных распределителей импульсов, а для синхронизации однотактных распределителей импульсов оно неприменимо, что существенно сужает область его применения.

Цель изобретения - расщирение области применения устройства.

Поставленная цель достигается тем, что устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов, управляющий и К управляемых распределителей импульсов (К-число каналов синхронизации), К. блоков управления, первую и вторую группу из К. элеметов и И группу из К элементов ИЛИ, причем выход генератора тактовых импульсов соединен со входом управляющего распределителя и с первыми входами элементов И первой и второй группы, вторые входы элементов И первой группы подключены к выходам соответствующих блоков управления, группа выходов каждого управляемого распределителя импульсов подключена к первой группе входов каждого блока управления, вторая группа входов каждого

ИЗ которых соединена со входами устройства, входы каждого элемента ИЛИ группы соединены с выходами соответствующих элементов И первой и второй групп, а выход - со входом соответствующего управляе.мого распредлителя импульсов, содержит элементы ИЛИ-НЕ и НЕ, триггер, элемент задержки, выход которого подключен ко вторым входам элементов И второй группы, а вход - к выходу триггера, счетный вход которого соединен с выходом элемента ИЛИ -

НЕ, вход установки триггера через элемент НЕ подключен к первому выходу управляющего распределителя импульсов, выходы ко-, торого с второго по 1-ый соединены со входами элемента ИЛИ-НЕ.

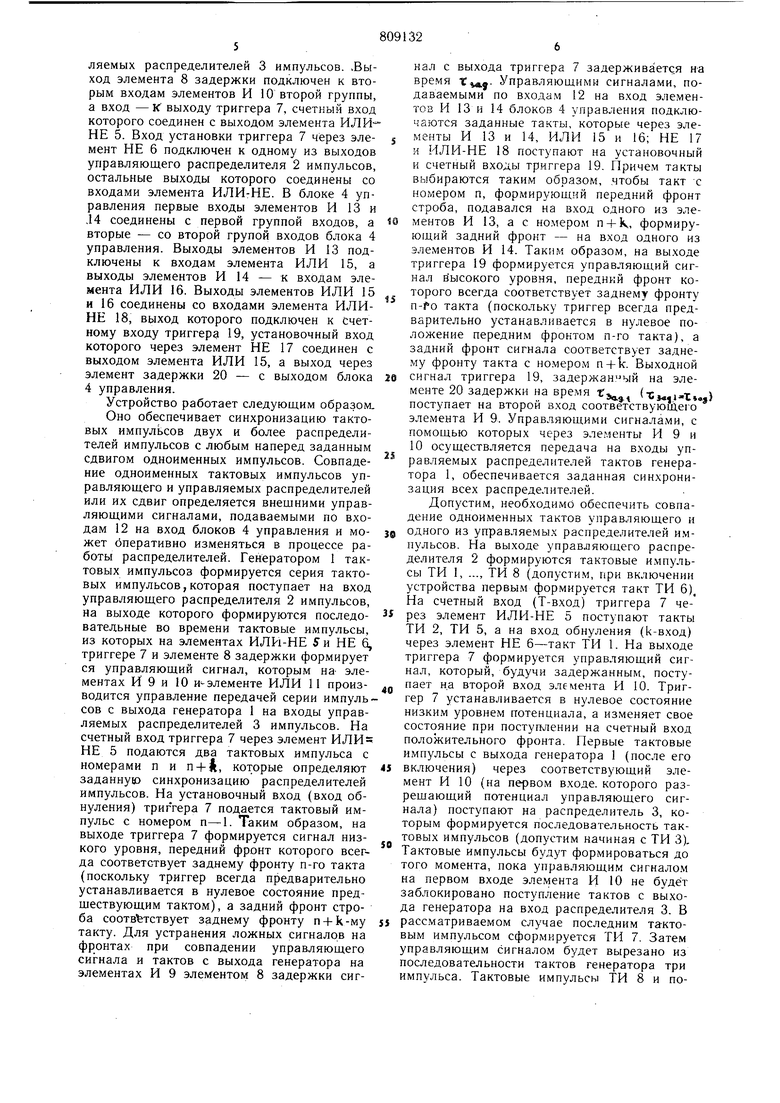

Блок управления содержит первую и вторую группу элементов И, первый и второй элементы ИЛИ, элементы ИЛИ-НЕ и НЕ, триггер и элемент задержки, причем первые входы элементов И первой и второй групп подсоединены к соответствующим входам

первой группы входов блока управления, вторые входы соединены с соответствующими входами второй группы входов блока управления, выходы элементов И первой группы подключены к входам первого элемента ИЛИ, а выходы элементов И второй группы - к входам второго элемента ИЛИ, выходы первого и второго элементов ИЛИ блока управления соединены с входами элемента ИЛИ-НЕ блока управления, выход которого подключен к счетному входу триггера, установочный вход триггера блока управления которого через элемент НЕ блока управления соединен с выходом первого элемента ИЛИ, а выход через элемент задержки - с выходом блока управления. На фиг. 1 приведена схема устройства

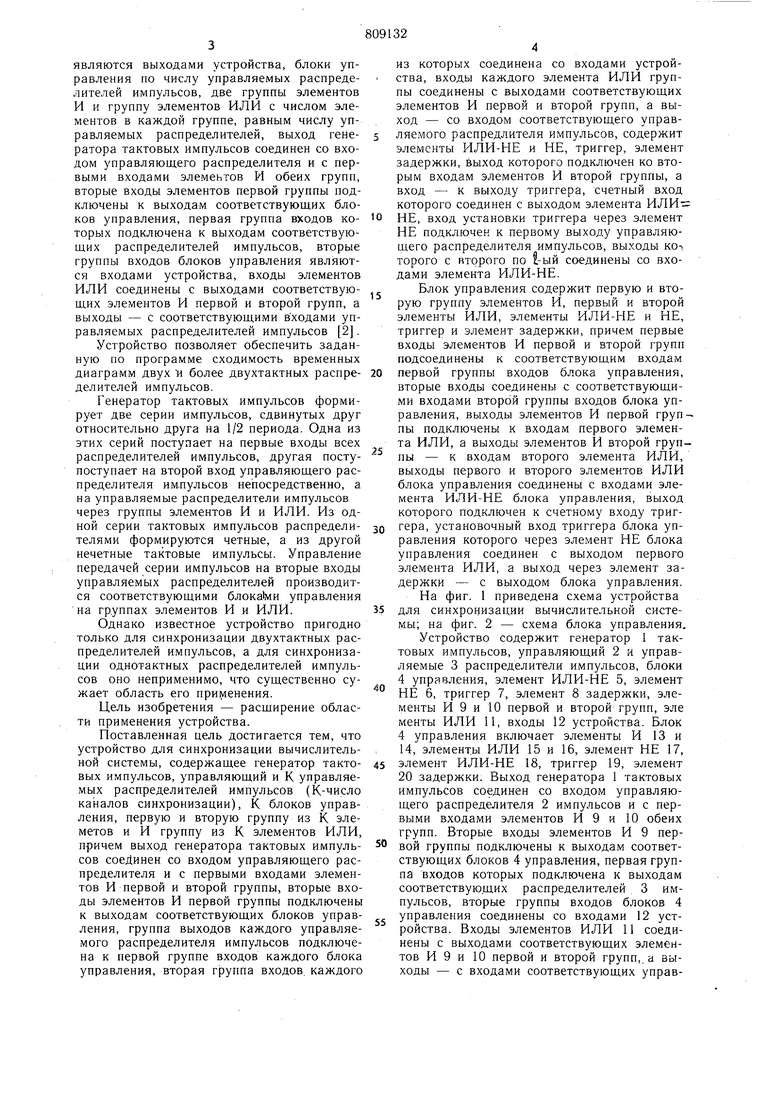

5 для синхронизации вычислительной системы; на фиг. 2 - схема блока управления. Устройство содержит генератор 1 тактовых импульсов, управляющий 2 и управляемые 3 распределители импульсов, блоки 4 управления, элемент ИЛИ-НЕ 5, элемент НЕ 6, триггер 7, элемент 8 задержки, элементы И 9 и 10 первой и второй групп, эле менты ИЛИ 11, входы 12 устройства. Блок 4 управления включает элементы И 13 и 14, элементы ИЛИ 15 и 16, элемент НЕ 17,

5 элемент ИЛИ-НЕ 18, триггер 19, элемент 20 задержки. Выход генератора 1 тактовых импульсов соединен со входом управляющего распределителя 2 импульсов и с первыми входами элементов И 9 и 10 обеих групп. Вторые входы элементов И 9 первой группы подключены к выходам соответствующих блоков 4 управления, первая группа входов которых подключена к выходам соответствующих распределителей 3 импульсов, вторые группы входов блоков 4 управления соединены со входами 12 устройства. Входы элементов ИЛИ 11 соединены с выходами соответствующих элементов И 9 и 10 первой и второй групп,, а выходы - с входами соответствующих управляемых распределителей 3 импульсов. -Выход элемента 8 задержки подключен к вторым входам элементов И 10 второй группы, а вход - К выходу триггера 7, счетный вход которого соединен с выходом элемента ИЛИ- НЕ 5. Вход установки триггера 7 через элемент НЕ 6 подключен к одному из выходов управляющего распределителя 2 импульсов, остальные выходы которого соединены со входами элемента ИЛИ-НЕ. В блоке 4 управления первые входы элементов И 13 и ,14 соединены с первой группой входов, а вторые - со второй групой входов блока 4 управления. Выходы элементов И 13 подключены к входам элемента ИЛИ 15, а выходы элементов И 14 - к входам элемента ИЛИ 16. Выходы элементов ИЛИ 15 и 16 соединены со входами элемента ИЛИНЕ 18, выход которого подключен к Счетному входу триггеру 19, установочный вход которого через элемент НЕ 17 соединен с выходом элемента ИЛИ 15, а выход через элемент задержки 20 - с выходом блока 4 управления. Устройство работает следующим образом. Оно обеспечивает синхронизацию тактовых импульсов двух и более распределителей импульсов с любым наперед заданным сдвигом одноименных импульсов. Совпадение одноименных тактовых импульсов управляющего и управляемых распределителей или их сдвиг определяется внещними управляющими сигналами, подаваемыми по входам 12 на вход блоков 4 управления и может оперативно изменяться в процессе работы распределителей. Генератором 1 тактовых импульсоз формируется серия тактовых импульсов,которая поступает на вход управляющего распределителя 2 импульсов, на выходе которого формируются последовательные во времени тактовые импульсы, из которых на элементах ИЛИ-НЕ 5 и НЕ 6, триггере 7 и элементе 8 задержки формирует ся управляющий сигнал, которым на- элементах И 9 и 10 и-элементе ИЛИ 11 производится управление передачей серии импульсов с выхода генератора 1 на входы управляемых распределителей 3 импульсов. На счетный вход триггера 7 через элемент ИЛИ НЕ 5 подаются два тактовых импульса с номерами п и п + |, которые определяют заданную синхронизацию распределителей импульсов. На установочный вход (вход обнуления) триггера 7 подается тактовый импульс с номером п-1. Таким образом, на выходе триггера 7 формируется сигнал низкого уровня, передний фронт которого всегда соответствует заднему фронту п-го такта (поскольку триггер всегда предварительно устанавливается в нулевое состояние предществующим тактом), а задний фронт строба соответствует заднему фронту n-fk-му такту. Для устранения ложных сигналов на фронтах при совпадении управляющего сигнала и тактов с выхода генератора на элементах И 9 элементом 8 задержки сигнал с выхода триггера 7 задерживается н-а время tie.- Управляющими сигналами, подаваемыми по входам 12 на вход элементов И 13 и 14 блоков 4 управления подключаются заданные такты, которые через элементы И 13 и 14, ИЛИ 15 и 16; НЕ 17 и ИЛИ-НЕ 18 поступают на установочный и счетный входы триггера 19. Причем такты выбираются таким образом, .чтобы такт т номером п, формирующий передний фронт строба, подавался на вход одного из элементов И 13, а с но.мером п + К, формирующий задний фронт - на вход одного из элементов И 14. Таким образом, на выходе триггера 19 формируется управляющий сигнал высокого уровня, передний фронт которого всегда соответствует заднему фронту n-fo такта (поскольку триггер всегда предварительно устанавливается в нулевое положение передним фронтом п-го такта), а задний фронт сигнала соответствует заднему фронту такта с номером n + k Выходной сигнал триггера 19, задержанный на элементе 20 задержки на время t (Cj«.i-t.j) поступает на второй вход соответствующего элемента И 9. Управляющими сигналами, с помощью которых через эле.ментьг И 9 и 10 осуществляется передача на входы управляемых распределителей тактов генератора 1, обеспечивается заданная синхронизация всех распределителей. Допустим, необходимо обеспечить совпадение одноименных тактов управляющего и одного из управляемых распределителей импульсов. На выходе управляющего распределителя 2 формируются тактовые и.мпульсы ТИ 1, ..., ТИ 8 (допустим, при включении устройства первым формируется такт ТИ 6), На счетный вход (Т-вход) триггера 7 через элемент ИЛИ-НЕ 5 поступают такты ТИ 2, ТИ 5, а на вход обнуления (k-вход) через элемент НЕ 6-такт ТИ 1. На выходе триггера 7 формируется управляющий сигнал, который, будучи задержанным, поступает на второй вход элемента И 10. Триггер 7 устанавливается в нулевое состояние низким уровнем потенциала, а изменяет свое состояние при поступчдении на счетный вход положительного фронта. Первые тактовые и.мпульсы с выхода генератора 1 (после его включения) через соответствующий элемент И 10 (на первом входе, которого разрешающий потенциал управляющего сигнала) поступают на распределитель 3, которым формируется последовательность тактовых импульсов (допустим начиная с ТИ 3). Тактовые импульсы будут формироваться до того момента, пока управляющим сигнало.м на первом входе элемента И 10 не будет заблокировано поступление тактов с выхода генератора на вход распределителя 3. В рассматриваемом случае пос.тедним тактовым импульсом сформируется ТИ 7. Затем управляющим сигналом будет вырезано из последовательности тактов генератора три импульса. Тактовые импульсы ТИ 8 и последующие будут сформированы, когда управляющим сигналом будет разрещена передача тактов с ге нератора 1 на распределитель 3. После формирования распределителем 3 импульса ТИ 2 на выходе блока 4 управления устанавливается положительный уровень сигнала, которым через элемент И 9 подключаются такты генератора 1 к входу распределителя 3. Происходит формирование тактовых импульсов до ТИ 5, после чего блокируется на элементах И 9 и 10 поступление двух тактов на вход распределителя 3. При блокировке тактов на вход управляемых распределителей происходит смещение тактовой сетки управляющего распределителя до их полного совпадения. Управляемые распределители импульсов могут одновременно функционировать с различным относительно управляющего распределителя сдвигом тактовых сеток в зависимости от режима работы вычислительной системы. Предлагаемое устройство обладает щирокой областью применения. Оно позволяет осуществить синхронизацию однотактных распределителей импульсов, а также црименимо для синхронизации двухтактных распределителей импульсов. При этом один из выходов генератора тактов подключается к первым входам всех распределителей импульсов, а второй выход - в соответствии со схемой (фигТ 2). Формула изобретения 1. Устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов, управляющий и К управляемых распределителей импульсов (Кчисло каналов синхронизации), К блоков управления, первую и вторую группу из К элементов И и группу из К элементов ИЛИ, причем выход генератора тактовых импульсов соединен со входом управляющего распределителя и с первыми входами элементов И первой и второй группы, вторые входы элементов И первой группы подключены к выходам соответствующих блоков управления, группа выходов каждого управляемого распределителя импульсов подключена к первой группе входов каждого блока управления, вторая группа входов каждого из которых соединена со входами устройства, входы каждого элемента ИЛИ соединены с выходами соответствующих элементов И первой и второй групп, а выход - со входом соответствующего управляемого распределителя импульсов, отличающееся тем, что, с целью расщирения области применения, оно содержит элементы ИЛИ-НЕ и НЕ, триггер, элемент задержки, выход которого подключен ко вторым входам элементов И второй группы, а вход - к выходу триггера, счетный вход которого соединен с выходом элемента ИЛИ-НЕ, вход установки триггера через элемент НЕ подключен к первому входу управляющего распределителя импульсов, выходы которого с второго по .-ый соединены со входами элемента ИЛИ-НЕ. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит первую и вторую группу элементов И, первый и второй элементы ИЛИ, элементы ИЛИ-НЕ, и НЕ, триггер и элемент задержки, причем первые входы элементов И первой и второй групп подсоединены к соответствующим входам первой группы входов блока управления, вторые входы соединены с соответствующими входами второй груцпы входов блока управления, выходы элементов И первой группы подключены к входам первого элемента ИЛИ, а выходы элементов И второй группы - к входам второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены с входами элеллента ИЛИ-НЕ, выход которого подключен к счетному входу триггера, установочный вход триггера блока управления через элемент НЕ соединен с выходом первого элемента ИЛИ, а выход через элемент задержки - с выходом блока управления, Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 458825, кл. G 06 F 15/16, 1975. 2. Авторское свидетельство СССР по заявке № 2409473/18-24, кл. G 06 F 15/16, 1976.

12

Фиг. 2

Авторы

Даты

1981-02-28—Публикация

1978-09-22—Подача