(ЗА) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации системыОбМЕНА иНфОРМАциЕй | 1979 |

|

SU847310A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство для сопряжения цифровой вычислительной машины с общей магистралью | 1980 |

|

SU907536A1 |

| Устройство для ввода информации | 1977 |

|

SU682888A1 |

| Резервированное процессорное устройство | 1987 |

|

SU1594545A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1980 |

|

SU907537A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1982 |

|

SU1062681A2 |

1

Изобретение относится к вычисли- тельной технике и может быть использовано при построении многомашинных (мультипроцессорных) вычислительных систем,работающих в реальном масштабе (фемени.

В многомашинных вычислительных системах повышение производительности достигается за счет распараллеливания по ЦВМ системы алгоритмов реша-, емых задач. Распараллеливание предусматривает в больитнстве случае необходимость организации обмена информацией и управляющими словами между ЦВМ вычислительной системы, при- 15 ЦВМ производительность всей системы в целом существенно зависит от быстродействия межмашинного обмена в системе.

При организации межмашинного об- 20 мена через канал прямого доступа ЦВМ быстродействие межмашинного обмена определяется временем реакции ЦВМ на внешний запрос типа приостановка.

Это время составляет один рабочий цикл.

Таким образом, время передачи одного слова информации между ОЗУ ЦВМ не может быть меньше двух рабочих циклов. Это время можно уменьшить до одного рабочего цикла, если тактовые сетки ЦВМ, участвующих в обмене, синхронизировать друг относительно друга таким образом, чтобы запрос, поступивший от ЦВМ-приемника в ЦВМ-датчик в каком-либо рабочем цикле, принимался и выполнялся в ЦВМ-датчике в этом же цикле. Такая синхро низация позволяет свести к минимуму время реакции ЦВМ на внешний запрос типа приостановка. Синхронизация распределителей импульсов вычислительной системы осуществляется специальными устройствами синхронизации.

Известно устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов, распределители тактовых импульсов

по числу процессоров в системе, cxe мы управления и элементы И по числу управляемых процессоров в системе, причем выход генератора тактовых импульсов соединен с первыми входами элементов И, выходы которых подключены к входам распределителей импульсов управляемых процессоров, группы выходов распределителей импульсов соединены с группами входов соответствующих схем управления и являются выходами устройства, вторые входы схем управления являются входами задания программного сдвига распределителей импульсов.

Распределители импульсов управляются импульсами, поступающими с генератора тактовых импульсов на вход распределителя импульсов управляющего процессора непосредственно, а на входы распределителей импульсов управляемых процессоров через элементы И. Разрешение {и запрет) на прохождение тактовых импульсов на распределители импульсов управляемых процессоров формируется по состоянию соответствующего распределителя импульсов 1.

Недостатком указанного устройства является его низкая надежность, которая обусловлена наличием в устройстве состязаний сигналов (гонок), что приводит к уменьшению длительности отдельных тактовых импульсов на выходах распределителей импульсов управляемых процессоров, а также к появлению ложных тактовых импульсов, которые не позволяют осуществить заданную синхронизацию распределителей импульсов. Причиной состязаний сигналов является различие во времени их прохождения по логическим цепям и через запоминающие элементы(триггеры).

Наиболее близким к предлагаемому по технической сущности является устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов, управляющий и управляемый распределители импульсов, блоки управления, две группы элементов И/ и группу элементов ИЛИ с числом элементов в каждой группе, равным числу управляемых процессоров причем выход генератора соединен с первыми выходами элементов И первой и второй групп, выходы которых подключены к входам соответствующих элементов ИЛИ, выходы элементов ИЛИ

соединены с входами управляемых распределителей импульсов, группы выходов которых подключены к первой группе входов соответствующих блоков управления и являются выходами устройства, к второй группе входов блоков управления подключена группа входов устройства.

Распределители импульсов запускаются импульсами, поступающими от общего генератора тактовых импульсов на вход распределителя импульсов управляющего процессора непосредственно, а на входы распределителей импульсов управляемых процессоров через элементы И и ИЛИ. Управление прохождением тактовых импульсов управляемых процессоров производится стробами управления, отражающими текущее состояние управляемых распределителей импульсов. Устранение ложных сигналов на фронтах при совпадении управляющего строба и тактов с выхода генератора обеспечивается соответствующей задержкой строба управления на элементах задержки. Устройство обеспечивает заданную заранее (или устанавливаемую по программе) сходимость временных диаграмм распределителей импульсов всех процессоров системы и поддержание синхронной работы распределителей в течение всего времени работы вычислительной системы 2.

Известное устройство предусматривает синхронную работу всех процессоров системы независимо от решаемых ими задач, причем предполагается, что длительность рабочих циклов всех процессоров равна в течение всего времени работы системы, т.е. в системе команд процессоров отсутствуют команды с переменным циклом.

В ряде процессоров длительность рабочего цикла в некоторых операциях является .переменной 13 и j.

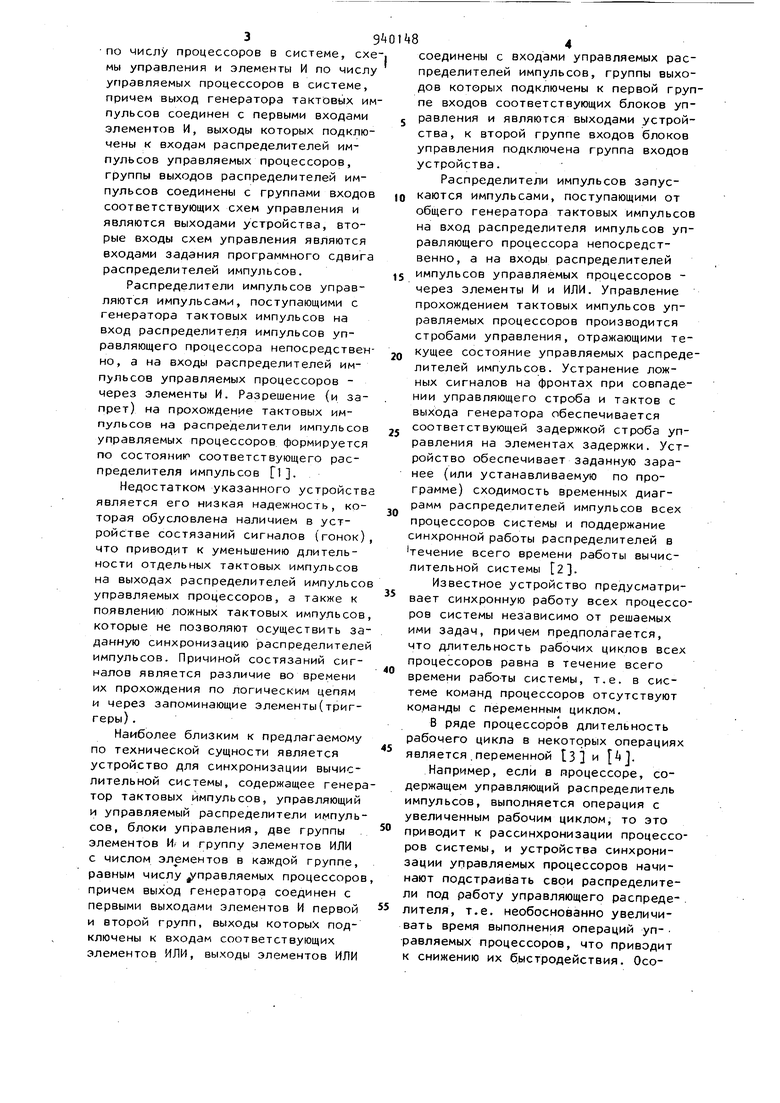

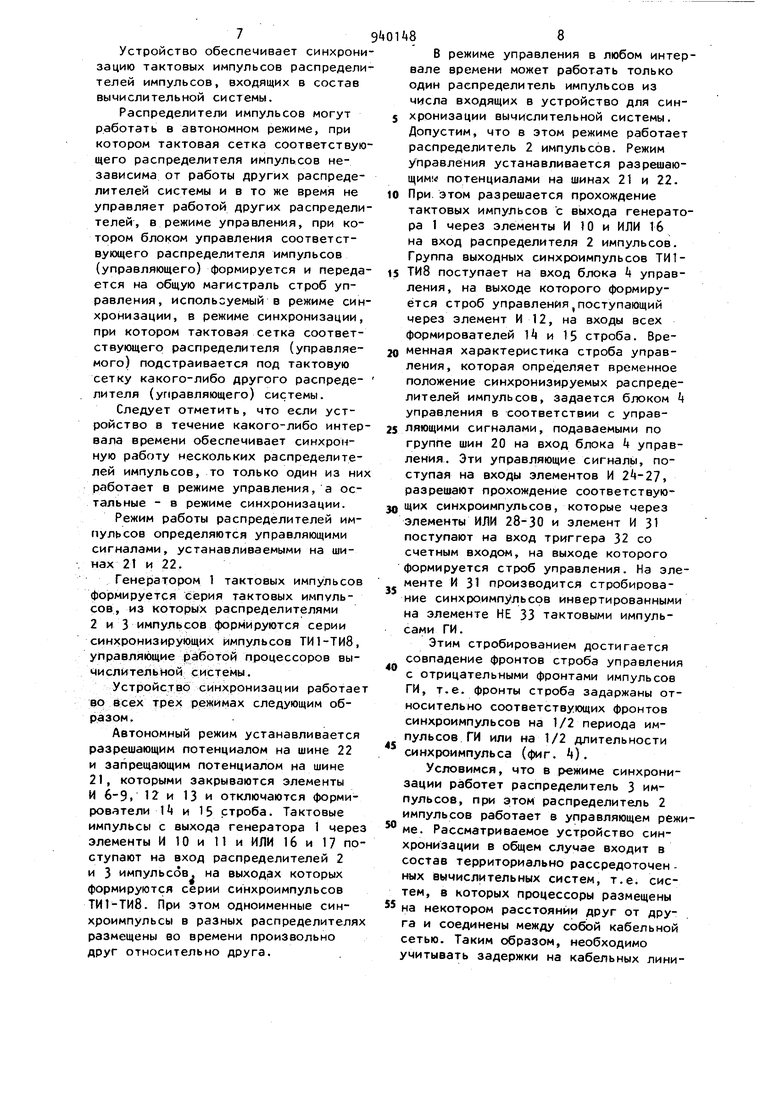

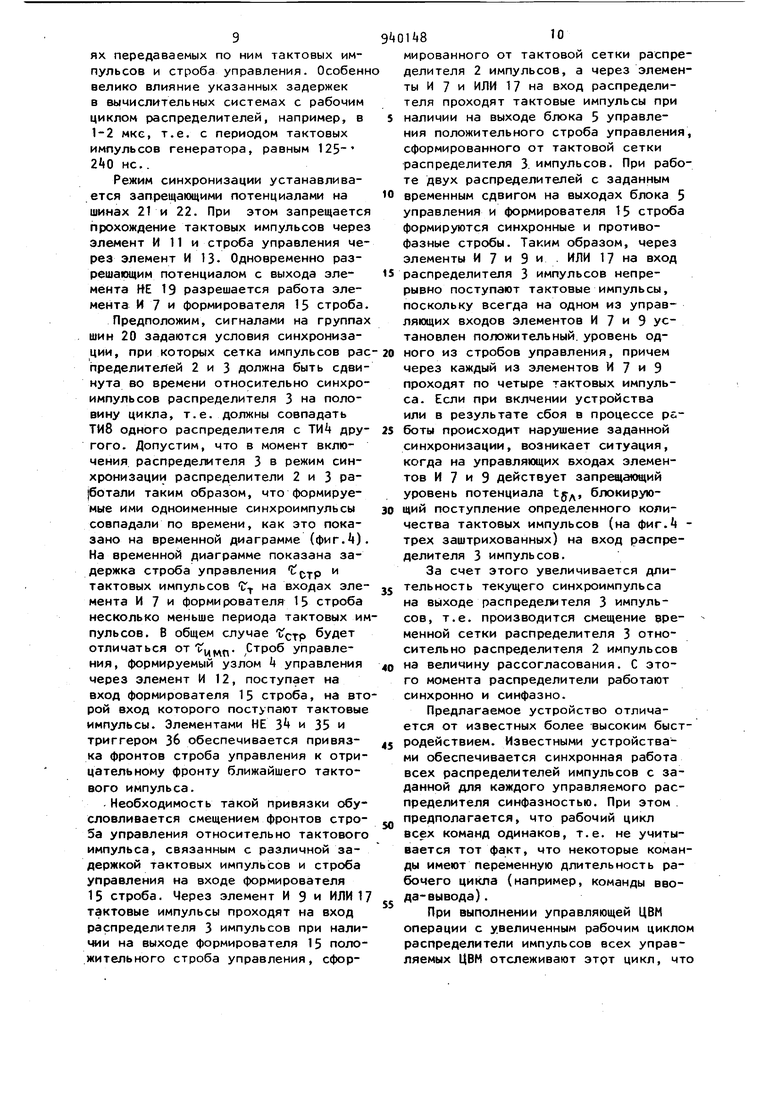

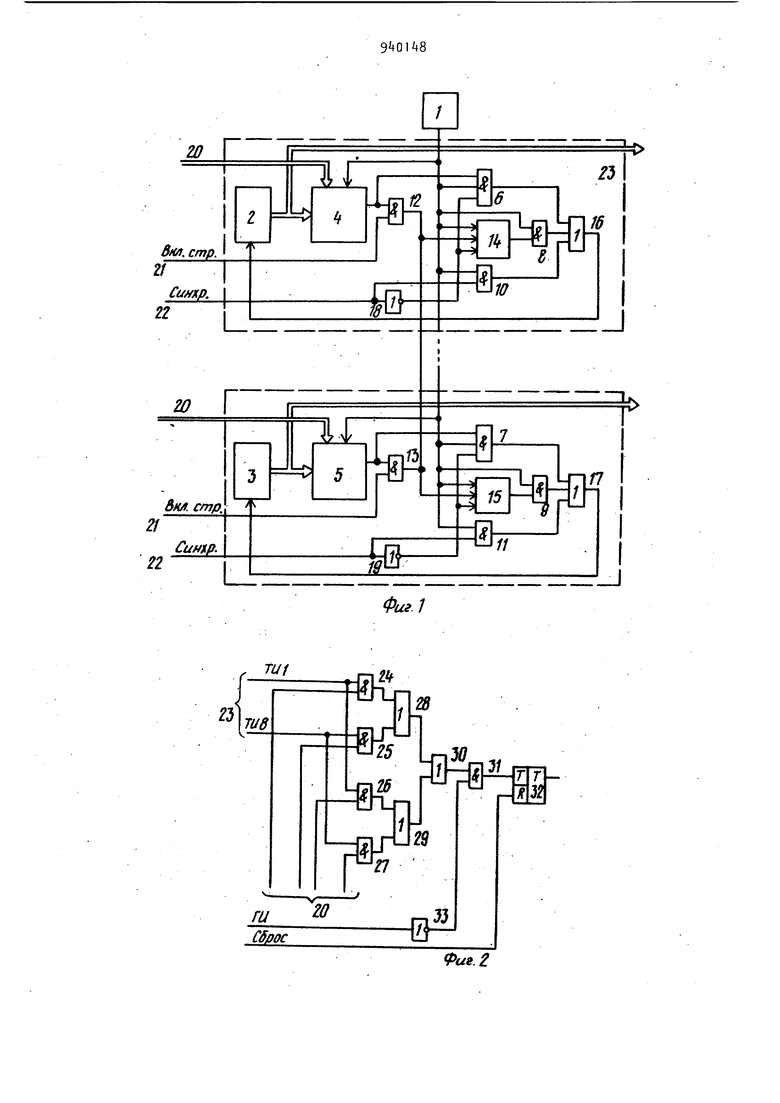

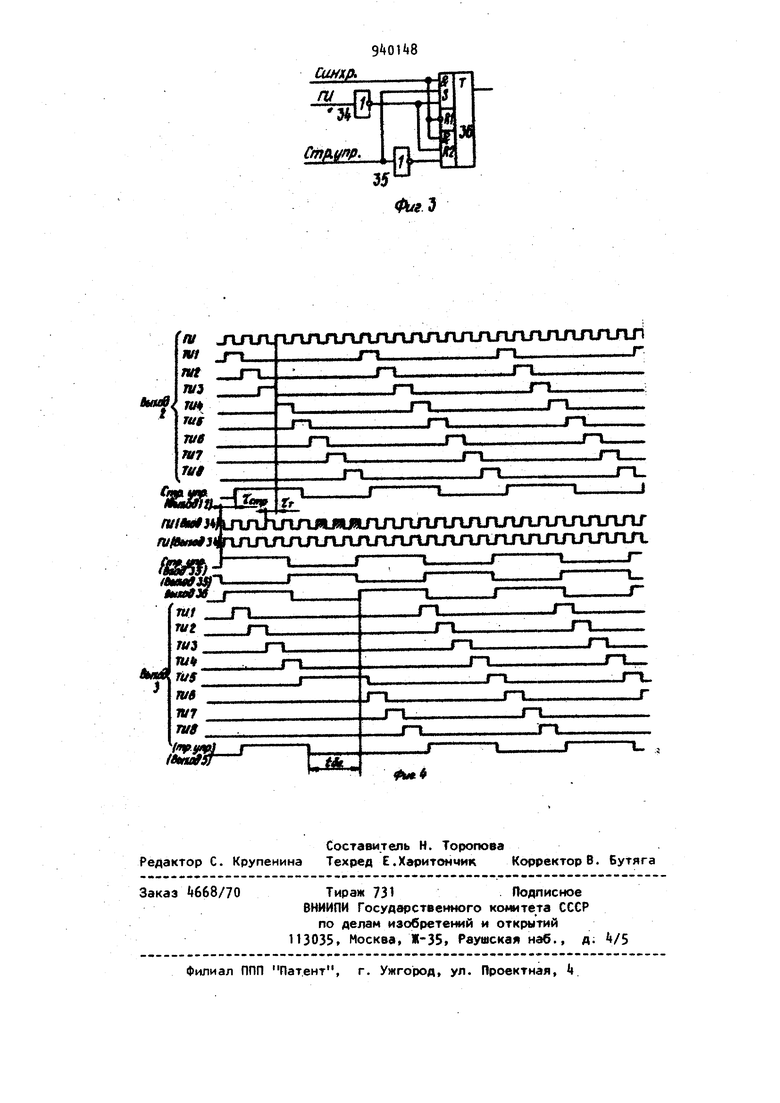

Например, если е процессоре, содержащем управляющий распределитель импульсов, выполняется операция с увеличенным рабочим циклом, то это приводит к рассинхронизации процессоров системы, и устройства синхронизации управляемых процессоров начинают подстраивать свои распределители под работу управляющего распределителя, т.е. необоснованно увеличивать время выполнения операций уп- равляемых процессоров, что приводит к снижению их быстродействия. Особенно существенно такое снижение быстродействия при передаче управляющим процессором массива информации (многократное повторение операций обмена с увеличенным рабочим циклом). Таким образом, применение из- вестных устройств синхронизации в вычислительных системах, содержащих процессоры, в составе которых имеют ся команды с переменным циклом, при водит к снижению быстродействия управляемых процессоров, и следовательно, всей системы в целом, что является недостатком известного уст ройства. Цель изобретения - повышение быс родействия вычислительной системы. Поставленная цель достигается те что в устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов, п бло . ков выработки .синхросигналов (п число процессоров), причем каждый блок выработки синхрюсигналов содер жит распределитель, узел управления два элемента И, элемент ИЛИ, причем выход генератора тактовых импульсов соединен в каждом блоке выработки синхросигналов с первым входом первого элемента И, с первым входом вто рого элемента И, с синхровходом узла управления, управляющие входы узлов управления являются группой управляющих входов устройства, выходы распределителей в каждом блоке выработки синхросигналов соединены соответственно с тактовыми входами узла управления и являются тактовыми выходами устройства, выход узла упра ления соединен в каждом блоке выработки синхросигналов с вторым входом первого элемента И, выход которого соединен в каждом блоке выработ ки синхросигналов с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемен,та И, введены в каждый блок выработки синхросигналов элемент НЕ, два элемента И и формирователь строба, выход которого соединен в каждом блоке выработки синхросигналов с вторым входом второго элемента И, третий вход элемента ИЛИ соединен с выходом третьего элемента И, первый вход которого соединен с выходом генератора тактовых импульсов и с синхровходом формирователя строба, второй вход третьего элемента И соединен с входом элемента НЕ, с входом управления режимом синхронизации каждого блока выработки синхросигналов и является входом управу1ения режимом синхронизации устройства, выход элемента НЕ в каждом блоке выработки синхросигналов соединен с третьим входом первого элемента И . и с входом режима синхронизации формирователя строба, вход управления стробом которого соединен в каждом блоке выработки синхросигналов с выходом четвертого элемента И, первый вход которого соединен с выходом узла управления в каждом блоке выработки синхросигналов, второй вход четвертого элемента И в каждом блоке выработки синхросигналов является входом запуска устройства. Формирователь строба содержит два элемента НЕ и триггер, выход которого является выходом формирователя, вход режима синхронизации которого соединен с первым установочным входом триггера, с первым и с вторым входами сброса триггера, третий вход сброса которого соединен с вторым установочным входом триггера и с выходом первого элемента НЕ, вход которого соединен с синхровходом формирователя, вход управления стробом которого соединен с входом второго элемента НЕ и с третьим установочным входом триггера, четвертый вход которого соединен с выходом второго элемента НЕ. На фиг. 1 приведена схема устройства для синхронизации вычислительной системы; на фиг. 2 - схема блока управления; на фиг. 3 схема формирователя строба; на фиг. временная диаграмма работы устройства. Устройство содержит генератор 1 тактовых импульсов, распределители 2 и 3 тактовых импульсов, узлы « и 5 правления, элементы И 6-13. формирователи 1 и 15 строба, элементы . ИЛИ 16 и 17, элементы НЕ 18 и 19, управляющие входы 20, вход 21 запуска, вход 22 управления режимом синхронизации, блоки 23 выработки синхросигналов. Узлы и 5 управления содержат элементы И , элементы ИЛИ 28-30, элемент И 31, триггер 32, элемент НЕ 33 Формирователи 1 и 15 содержат элементы НЕ 3 и 35 и тригrefi 36. 7 Устройство обеспечивает синхрони зацию тактовых импульсов распредели телей импульсов, входящих в состав вычислительной системы. Распределители импульсов могут работать в автономном режиме, при котором тактовая сетка соответствую щего распределителя импульсов независима от работы других распределителей системы и в то же время не управляет работой других распредели телей, в режиме управления, при котором блоком управления соответствующего распределителя импульсов (управляющего) формируется и переда ется на общую магистраль строб управления, испольсуемый в режиме син хронизации, в режиме синхронизации, при котором тактовая сетка соответствующего распределителя (управляемого) подстраивается под тактовую сетку какого-либо другого распределителя (управляющего) системы. Следует отметить, что если устройство в течение какого-либо интер вала времени обеспечивает синхронную работу нескольких распределителей импульсов, то только один из ни работает в режиме управления, а остальные - в режиме синхронизации. Режим работы распределителей импульсов определяются управляющими сигналами, устанавливаемыми на шинах 21 и 22. Генератором 1 тактовых импульсов формируется тактовых импульсов, из которых распределителями 2 и 3 импульсов формируются серии синхронизирующих импульсов ТИ1-ТИ8, управляющие работой процессоров вычислительной системы. Устррйствс синхронизации работае во всех трех режимах следующим образом. Автономный режим устанавливается разрешающим потенциалом на шине 22 и запрещающим потенциалом на шине 21, которыми закрываются элементы И 6-9. 12 и 13 и отключаются формирователи 1 и 15 строба. Тактовые импульсы с выхода генератора 1 чере элементы И 10 и 11 и ИЛИ 16 и 17 по ступают на вход распределителей 2 и 3 импульсов, на выходах которых формируются серии синхроимпульсов ТИ1-ТИ8. При этом одноименные синхроимпульсы в разных распределителя размещены во времени произвольно друг относительно друга. 8 В режиме управления в любом интервале времени может работать только один распределитель импульсов из числа входящих в устройство для синхронизации вычислительной системы. Допустим, что в этом режиме работает распределитель 2 импульсов. Режим управления устанавливается разрешающим потенциалами на шинах 21 и 22. При. этом разрешается прохождение тактовых импульсов с выхода генератора 1 через элементы И 10 и ИЛИ 16 на вход распределителя 2 импульсов. Группа выходных синхроимпульсов ТИ1ТИВ поступает на вход блока управления, на выходе которого формируется строб управления,поступающий через элемент И 12, на входы всех формирователей И и 15 строба. Временная характеристика строба управления, которая определяет временное положение синхронизируемых распределителей импульсов, задается блоком Ц управления в соответствии с управляющими сигналами, подаваемыми по группе шин 20 на вход блока k управления. Эти управляющие сигналь), поступая на входы элементов И разрешают прохождение соответствующих синхроимпульсов, которые через элементы ИЛИ 28-30 и элемент И 31 поступают на вход триггера 32 со счетным входом, на выходе которого формируется строб управления. На элементе И 31 производится стробирование синхроимпульсов инвертированными на элементе НЕ 33 тактовыми импульсами ГИ. Этим стробированием достигается совпадение фронтов строба управления с отрицательными фронтами импульсов ГИ, т.е. фронты строба задержаны относительно соответствующих фронтов синхроимпульсов на 1/2 периода импульсов ГИ или на 1/2 длительности синхроимпульса (фиг. . Условимся, что в режиме синхронизации работет распределитель 3 импульсов, при этом распределитель 2 импульсов работает в управляющем режиме. Рассматриваемое устройство синхронизации в общем случае входит в состав территориально рассредоточен ных вычислительных систем, т.е. систем, в которых процессоры размещены на некотором расстоянии друг от друга и соединены между собой кабельной сетью. Таким образом, необходимо учитывать задержки на кабельных линиях передаваемых по ним тактовых импульсов и строба управления. Особенн велико влияние указанных задержек в вычислительных системах с рабочим циклом распределителей, например, в 1-2 МКС, т.е. с периодом тактовых импульсов генератора, равным 1252kO НС.. Режим синхронизации устанавливается запрещающими потенциалами на шинах 21 и 22. При этом запрещается прохождение тактовых импульсов через элемент И 11 и строба управления через элемент И 13- Одновременно разрешающим потенциалом с выхода элемента WE 19 разрешается работа элемента И 7 и формирователя 15 строба Предположим, сигналами на группах шин 20 задаются условия синхронизации, при которых сетка импульсов рас пределителей 2 и 3 должна быть сдвинута во времени относительно синхроимпульсов распределителя 3 на половину цикла, т.е. должны совпадать ТИ8 одного распределителя с ТИ другого. Допустим, что в момент включения распреде/мтеля 3 в режим синхронизации распределители 2 и 3 ра|ботали таким образом, что формируемые ими одноименные синхроимпульсы совпадали по времени, как это показано на временной диаграмме (фиг.). На временной диаграмме показана задержка строба управления тактовых импульсов V-f на входах элемента И 7 и формирователя 15 строба несколько меньше периода тактовых им пульсов. В общем случае стр будет отличаться от управления, формируемый узлом Ц управления через элемент И 12, поступает на вход формирователя 15 строба, на вто рой вход которого поступают тактовые импульсы. Элементами НЕ З и 35 и триггером 36 обеспечивается привязка фронтов строба управления к отрицательному фронту ближайшего тактового импульса. Необходимость такой привязки обусловливается смещением фронтов строба управления относительно тактового импульса, связанным с различной задержкой тактовых импульсов и строба управления на входе формирователя 15 строба. Через элемент И 9 и ИЛИ 17 тактовые импульсы проходят на вход распределителя 3 импульсов при наличии на выходе формирователя 15 положительного строба управления, сфор1ii810мированного от тактовой сетки распределителя 2 импульсов, а через элементы И 7 и ИЛИ 17 на вход распределителя проходят тактовые импульсы при наличии на выходе блока 5 управления положительного строба управления, сформированного от тактовой сетки распределителя 3. импульсов. При работе двух распределителей с заданным временным сдвигом на выходах блока 5 управления и формирователя 15 строба формируются синхронные и противофазные стробы. Таким образом, через элементы И 7 и 9 и . ИЛИ 17 на вход распределителя 3 импульсов непрерывно поступают тактовые импульсы, поскольку всегда на одном из управляющих входов элементов И 7 и 9 установлен положительный, уровень одного из стробов управления, причем через каждый из элементов И 7 и 9 проходят по четыре тактовых импульса. Если при вклчении устройства или в результате сбоя в процессе psботы происходит нарушение заданной синхронизации, возникает ситуация, когда на управляющих входах элементов И 7 и 9 действует запрещающий уровень потенциала t5д, блокирующий поступление определенного количества тактовых импульсов (на фиг. трех заштрихованных) на вход распределителя 3 импульсов. За счет этого увеличивается длительность текущего синхроимпульса на выходе распределителя 3 импульсов, т.е. производится смещение эременной сетки распределителя 3 относительно распределителя 2 импульсов на величину рассогласования. С этого момента распределители работают синхронно и синфазно. Предлагаемое устройство отличается от известных более высоким быстродействием. Известными устройствами обеспечивается синхронная работа всех распределителей импульсов с заданной для каждого управляемого распределителя синфазностью. При этом предполагается, что рабочий цикл всех команд одинаков, т.е. не учитывается тот факт, что некоторые команды имеют переменную длительность рабочего цикла (например, команды ввода-вывода) . При выполнении управляющей ЦВМ операции с увеличенным рабочим циклом распределители импульсов всех управляемых ЦВМ отслеживают этот цикл, что li приводит к необоснованному снижению быстродействия выполнения операций с обычным циклом. В предлагаемом устройстве синхронизируются распределители импульсов только тех ЦВМ, между которыми осуществляется межмашинный обмен. Работа распределителей импульсов других ЦВМ не влияе на их синхронизацию. Кроме того, предлагаемое устройство обладает более высокой надежностью по сравнению с известными. Низкая надежность которых обусловле на возможностью уменьшения длитель ности отдельных синхроимпульсов на выходах РИ, а также появлен|1ем ложных тактовых импульсов. В предлагаемом устройстве этот недостаток уст ранен. Формула изобретения 1. Устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов, п бло ков выработки синхросигналов (п число процессоров), причем каждый блок выработки синхросигналов содер жит распределитель, узел .управления два элемента И, элемент ИЛИ, причем выход генератора тактовых импульсов соединен в каждом блоке выработки синхросигналов с первым входом первого элемента И, с первым входом второго элемента И, с синхровходом узла управления, управляющие входы узлов управления являются группой управляющих входов устройства, выходы распределителей в каждом блоке выработки синхросигналов соединены соответственно с тактовыми входами узла управления и являются тактовыми выходами устройства, выход узла управления соединен в каждом блоке выработки синхросигналов с вторым входом первого элемента И, выход которого соединен в каждом блоке в работки синхросигналов с первым вхо дом элемента ИЛИ, второй вход которого соединен с выходом второго эле мента И,отличающееся тем, что, с целью увеличения быстро действия, в каждый блок выработки синхросигналов введены элемент НЕ, два элемента И и формирователь стро ба, выход которого соединен в каждом блоке выработки синхросигналов,с вторым входом второго элемента И, 4812 , третий вход элемента ИЛИ соединен с выходом третьего элемента И, первый вход которого соединен, с выходом генератора тактовых импульсов и с синхровходом формирователя строба, второй вход третьего элемента И соединен с входом элемента НЕ, с входом управления режимом синхронизации каждого блока выработки синхросигналов и является входом управления режимом синхронизации устройства, выход элемента НЕ в каждом блоке выработки синхросигналов соединен с третьим входом первого элемента И и с входом режима синхронизации формчирователя строба, вход управления стробом которого соединен в каждом б.гюке выработки синхросигналов с выходом четвертого элемента И, первый вход которого соединен с выходом узла управления а каждом б.поке выработки синхросигналов, второй вход четвертого элемента И в каждом блоке выработки синхросигналов является входом запуска устройства. 2. Устройство по п. 1, о т л и чающееся тем, что формирователь строба содержит два элемента НЕ и триггер, выход которого является выходом формирователя, вход режима синхронизации которого соединен с первым установочным входом триггера, с первым и с вторым входами сброса триггера, третий вход сброса которого соединен с вторым установочным входом триггера и с выходом первого элемента НЕ, вход которого соединен с синхровходом формирователя, вход управления стробом которого соединен с входом второго элемента НЕ и с третьим установочным входом триггера, четвертый вход которого соединен с выходом второго элемента НЕ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 58829, кл. G Об F 15/16, опублик. 2.Авторское свидетельство СССР (f 809132, кл. G 06 F 1/04, 1981 (прототип). 3.Соучек Б. Мини-ЭВМ в системах обработки информации. М., Мир, 1976, с. 242,246. 4. Бауман В., Куртц Ц., Науман Г. Стандартные интерфейсы для цифровых змерительных систем. М., Мир 1977, с. 42. г

Фиг.1 f

uwxp.

Авторы

Даты

1982-06-30—Публикация

1980-12-29—Подача