1

Изобретение относится к запоминающим устройствам, и может быть использовано в качестве вычислительного устройства (процессора) в однопроцессорных или многопроцессорных вычислительных машинах, предназначенных для реализации алгоритмов, требующих выполнения как параллельных операций над группами данных, так и последовательных операций над отдельными данными.

Известно ассоциативное запоминающее устройство, содержащее блоки, предназначенные для выполнения последовательных операций, однотипных групповых операций, а также блок памяти, предназначенный для хранения обрабатываемой информации 1.

Недостатком этого устройства является низкая скорость выполнения последовательных операций, а также низкая скорость обмена информацией между памятью, предназначенной для хранения данных, и ассоциативной памятью, предназначенной для параллельной обработки информации.

Наиболее близким техиическим рещением к данному изобретению является ассоциативное запоминающее устройство, содержащее реверсивный сдвигающий регистр, усилители, ассоциативный накопитель, подключенный к входному регистру, регистру маски и блоку управления, соединенному с регистром совпадений 2.

Недостатками этого устройства являются низкая скорость выполнения последовательных операций типа умножения, деления и т. п., а также низкая скорость обмена информацией между реверсивным сдвигающим регистром и ассоциативным накопителем, и, следовательно, низкое быстродействие при выполнении алгоритмов, в которых эти операции часто используются.

Другим недостатком устройства является избыточность его аппаратуры, поскольку при выполнении указанных алгоритмов блоки устройства обычно не работают одновременно и, следовательно, некоторые общие части их аппаратуры (регистры, входные и выходные усилители и т. п.) можно было реализовать в единственном экземпляре.

Целью настоящего изобретения является увеличение быстродействия устройства.

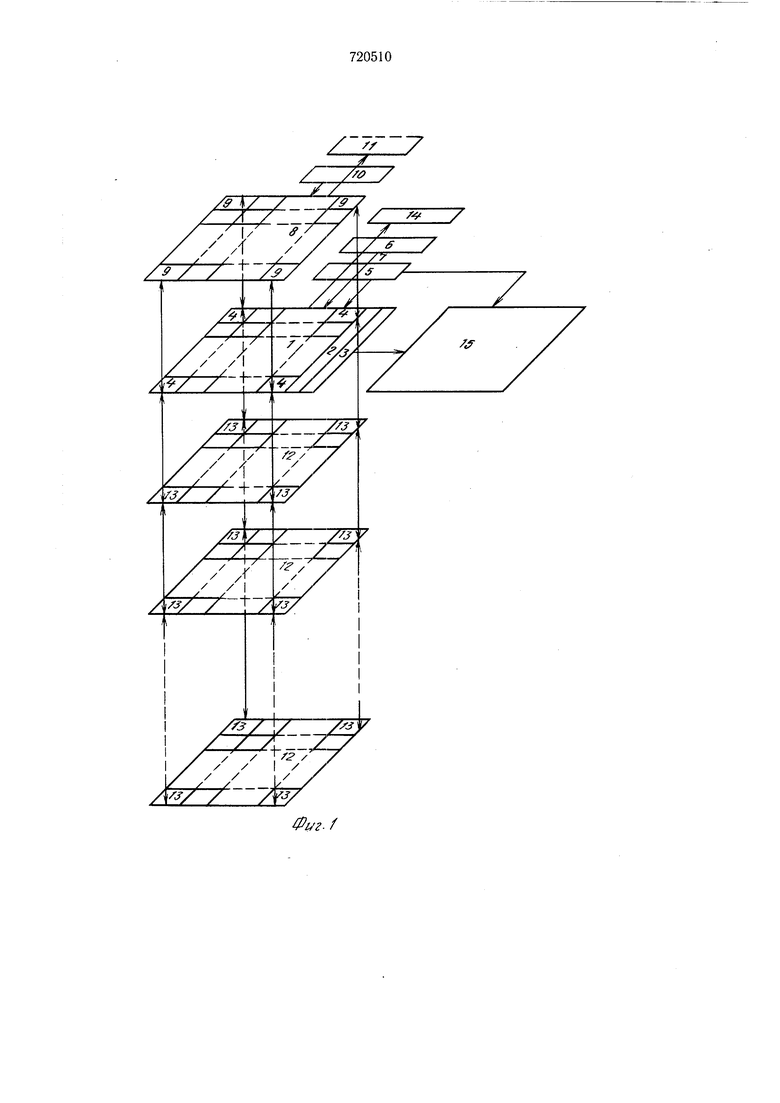

Поставленная цель достигается тем, что ассоциативное запоминающее устройство содержит адресные накопители, логический блок матричного типа и дополнительные регистры, причем входы и выходы запоминающих элементов одноименных разрядов одного из адресных накопителей подключены сооответственно к выходам первого и входам второго дополнительных регистров, входы записи и выходы считывания запоминающих элементов ассоциативного накопителя соединены соответственно с выходами и входами одноименных запоминающих элементов адресных накопителей, входы логического блока матричного типа подключены к выходам регистра совпадений и входного регистра, выходы считывания запоминающих элементов одноименных разрядов ассоциативного накопителя соединены со входами третьего дополнительного регистра. На фиг. 1 изображена структурная схема предложенного устройства, на фиг. 2 - структура устройства, реализованного на фиг. 3 - логическая структура части устройства, реализованной в одной интегральной схеме. Устройство (см. фиг. 1) содержит ассоциативный накопитель 1, соединенный с блоком управления 2 и регистром совпадений 3, состоящий из запоминающих элементов 4, входной регистр 5, регистр маски 6 с выходом 7, адресный накопитель 8, Состоящий из запоминающих элементов 9, пер)вый дополнительный регистр 10, служащий для ввода информации, второй дополнительный регистр 11, предназначенный для вывода информации, адресные накопители 12, состоящие из запоминающих элементов 13, третий дополнительный регистр 14, служащий для вывода данных, логический блок матричного типа 15. Запоминающие элементы 4, 9 и 13 соответственно накопителей 1, 8 и 12 образуют прямоугольные матрицы одинаковой размерности {с равным числом строк и столбцов соответственно). Входы и выходы запоминающих элементов 9 одноименных разрядов накопителя 8 подключены соответственно к выходам регистра 10 и входам регистра 11. Входы записи и выходы считывания запоминающих элементов 4 накопителя 1 соединены соответственно с выходами и входами одноименных запоминающих элементов 9 и 13 накопителей 8 и 12. Входы блока 15 подключены к выходам регистров 3 и 5. Выходы считывания запоминающих элементов 4 одноименных разрядов накопителя 1 соединены со входами регистра 14. Описанное устройство может быть использовано в качестве процессора в однопроцессорных или многопроцессорных вычислительных машинах для выполнения как пользовательских, так и системных программ. Рассмотрим каким образом в устройстве выполняются пользовательские программы. Устройство работает следующим образом. В начале работы в устройство вводится программа, подлежащая выполнению. Ввод программы осуществляется с помощью накопителя 8 последовательно по словам и параллельно по разрядам. После заполнения накопителя 8, его содержимое переписывается в соответствующий накопитель 12 за один такт работы устройства. После частичного или полного заполнения информацией накопителей 12 начинается выполнение программы. Для этого содержимое одного из накопителей 12 (например, первого сверху накопителя) переписывается в накопитель 1. При выполнении последовательного считывания команд программы из накопителя 1 в регистр 14 в нем производится декодирование некоторой части считанной команды с целью определения, является ли она параллельной операцией над группой данных или последовательной операцией над парой данных. В первом случае ее исполнение поручается накопителю 1, во втором - блоку 15. Обработка какой-либо части программы в устройстве совмещается во времени с вводом в него или выводом из него другой части программы с помощью накопителя 8. Пссле окончания вывода информации из накопителя 8 в какое-либо внешнее устройство, в накопитель 8 может быть переписано содержимое соответствующего накопителя 12. Выполнение параллельных операций в накопителе 1 осуществляется с помощью микрокоманд сравнения содержимого всех строк накопителя 1 с содержимым регистра 5 и микрокоманд записи в группы совпавших строк содержимого регистра 5 в разрядах, определяемых регистром маски 6. Результат сравнения фиксируется регистром совпадений 3. Реализация устройств, аналогичных описанному достаточно трудоемка. Однако матричная структура основных блоков устройства (15, накопителей 1, 8 и 12) облегчает его реализацию с помощью технологии интегральных схем. Матрицы основных блоков описанного устройства расчленяются на одинаковые подматрицы меньшей размерности, причем связанные между собой подматрицы разных блоков помещаются внутри одной интегральной схемы. Такой способ разбиения устройства на части позволяет повысить технологичность его изготовления на базе интегральных схем, поскольку удается построить основную часть его оборудования на одинаковых интегральных схемах и реализовать широкий канал связи между основными блоками устройства внутри кристаллов, методами технологии интегральных схем.

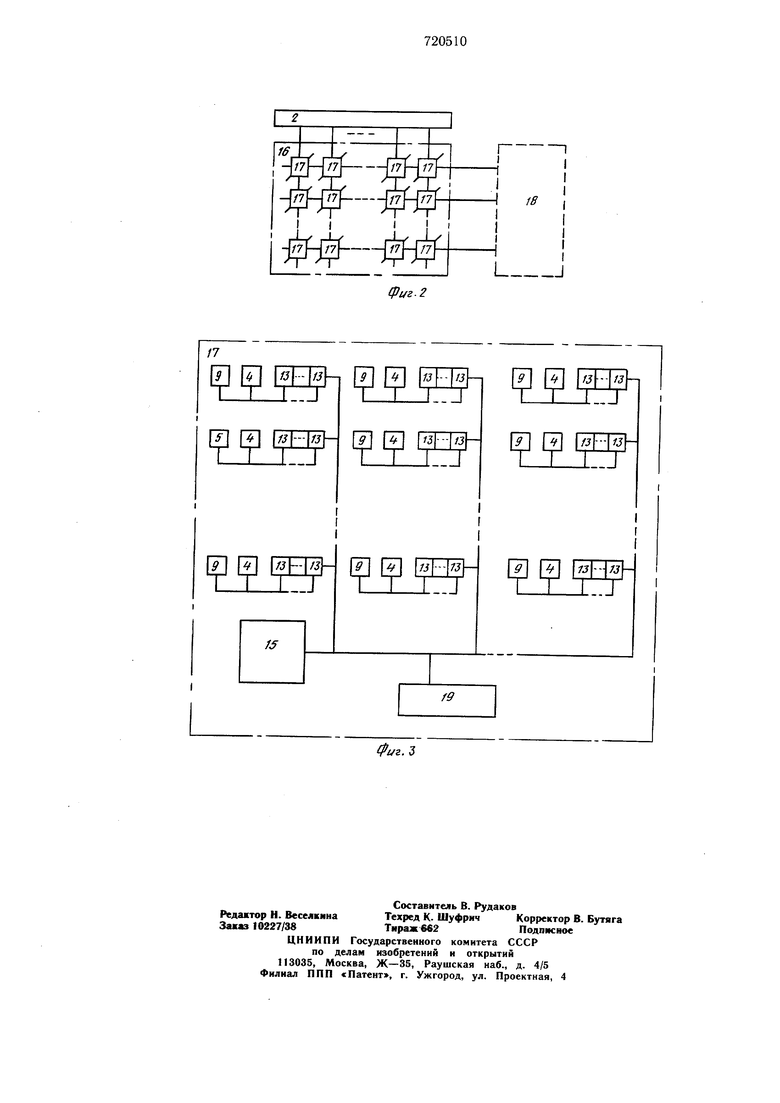

Кроме этого появляется возможность сократить общее количество внешних выводов с каждой интегральной схемы и реализовать некоторые логические схемы, общие для разных блоков, в единственном экземпляре. В результате этого устройство может быть реализовано в виде прямоугольной матрицы 16 (см. фиг. 2) из одинаковых интегральных схем 17, соединенных с блоком управления 2 и группой регистров 18, в состав которой входят регистры 5, 6, 10, 11 и 14,

Отдельная интегральная схема 17 (см. фиг. 3) содержит дешифратор адреса 19, часть блока 15, запоминающие элементы 4, 9, 13 накопителей 1, 8 и 12.

Максимальное количество запоминающих элементов, помещенных внутри отдельной интегральной схемы, определяется максимально допустимым на сегоднящний день уровнем интеграции и максимально допустимым количеством внешних выводов из интегральной схемы.

Таким образом описанное устройство обеспечивает более высокое по сравнению с известными быстродействие, которое достигается ускоренным выполнением последовательных операций типа умножение в блоке 15 за счет совмещения во времени процессов ввода-вывода программы и ее обработки в устройстве за счет ускорения переписи обрабатываемых массивов информации из адресных накопителей в ассоциативный.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее ассоциативный накопитель, подключенный к входному регистру, регистру маски и блоку управления, соединенному с регистром совпадений, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит адресные накопители, логический блок матричного типа и дополнительные регистры, причем входы

0 и выходы запоминающих элементов одноименных разрядов одного из адресных накопителей подключены соответственно к выходам первого и входам второго дополнительных регистров, входы записи и выходы считывания запоминающих элементов ассоциа5тивного накопителя соединены соответственно с выходами и входами одноименных запоминающих элементов адресных накопителей, входы логического блока матричного типа подключены к выходам регистра совпадений

0 и входного регистра, выходы считывания запоминающих элементов одноименных разрядов ассоциативного накопителя соединены со входами третьего дополнительного регистра.

5Источники информации,

принятые во внимание при экспертизе

1.Энслоу Ф. Г. Мультипроцессорные системы и параллельные вычисления. М., «Мир, с. 299 - 309.

2.Авторское свидетельство СССР

№ 524226, кл. G 11 С 15/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2025796C1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU928416A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1992 |

|

RU2025797C1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| ИЕРАРХИЧЕСКАЯ СИСТЕМА АССОЦИАТИВНОЙ ПАМЯТИ | 1992 |

|

RU2025795C1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU926717A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

Авторы

Даты

1980-03-05—Публикация

1977-08-23—Подача