(54) ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления пакета ошибок длины два | 1988 |

|

SU1578812A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство декодирования модифицированного кода БЧХ | 1990 |

|

SU1791961A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для автоматического контроля и коррекции ошибок | 1978 |

|

SU918947A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Устройство для коррекции ошибокС САМОКОНТРОлЕМ | 1977 |

|

SU796847A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

1

. Изобретение относится К радиотехнике и может использоваться в кодирующих и декодирующих устройствах.

Известно декодирующее устройство, содержащее объединенные по входу генератор синдрома, первый блок сумматоров по модулю два и блок контроля синдрома, к второму входу которого подключен выход генератора синдрома, а такЖе дешифратор коррекции ошибок, выход которого подключен к второму входу первого блока сумматоров по модулю два 1.

Однако известное устройство имеет недостаточную достоверность выдаваемой им информации.

Цель изобретения - повышение достоверности информации.

Для этого в декодирующее устройство, содержащее объединенные по входу генератор синдрома, первый блок сумматоров по модулю два и блок контроля синдрома, к второму входу которого подключен выход генератора синдрома, а также дещифратор коррекции ошибок, выход которого подключен к второму входу первого блока сумматоров по модулю два, введены последовательно соединенные анализатор ошибок синдро- ма и второй блок сумматоров по модулю два, выход которого подключен к входу дешифратора коррекции ошибок, а к второму входу второго блока сумматоров по модулю два подклЮчен выход генератора синдрома, при ,5том к входам анализатора ошибок синдрома подключены выходы блока контроля синдрома.

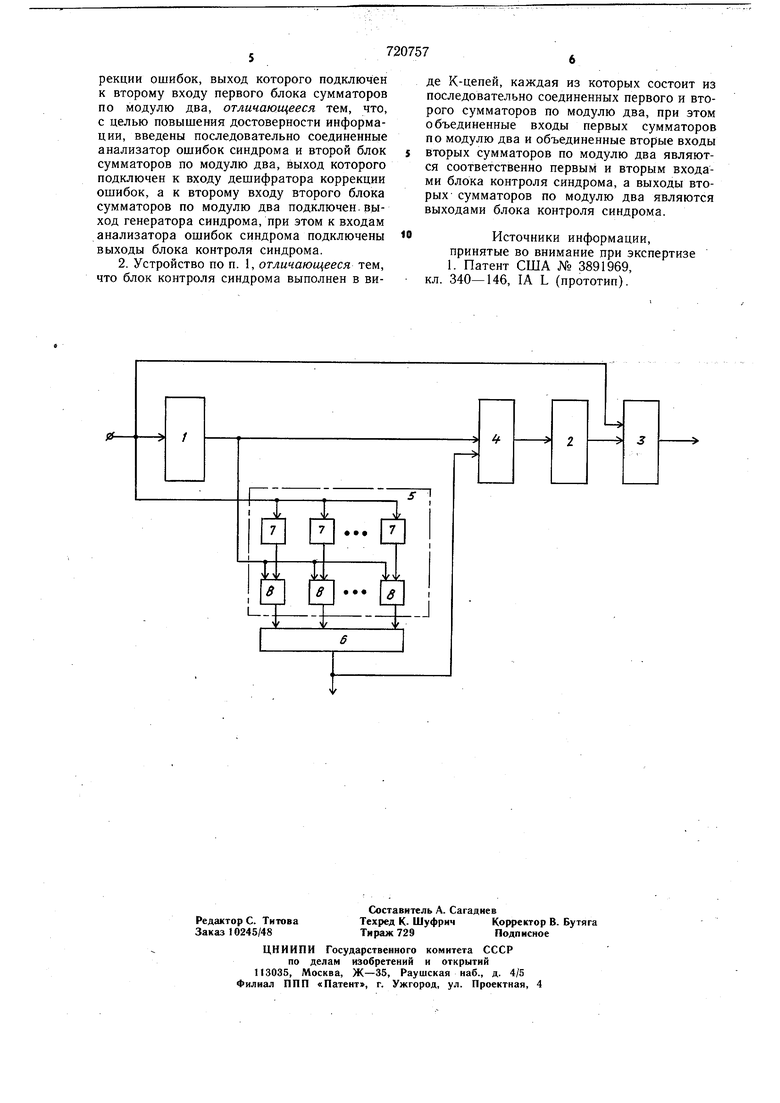

Блок контроля синдрома целесообразно выполнить в виде К цепей , каждая из которых состоит из последовательно соединенных первого и второго сумматоров по модулю два, при этом объединенные входы первых сумматоров по модулю два и объединенные вторые входы вторых сумматоров по модулю два являются соответственно первым и вторым входами блока контроля синдрома. а выходы вторых сумматоров по модулю два являются выходами блока контроля счндрома.

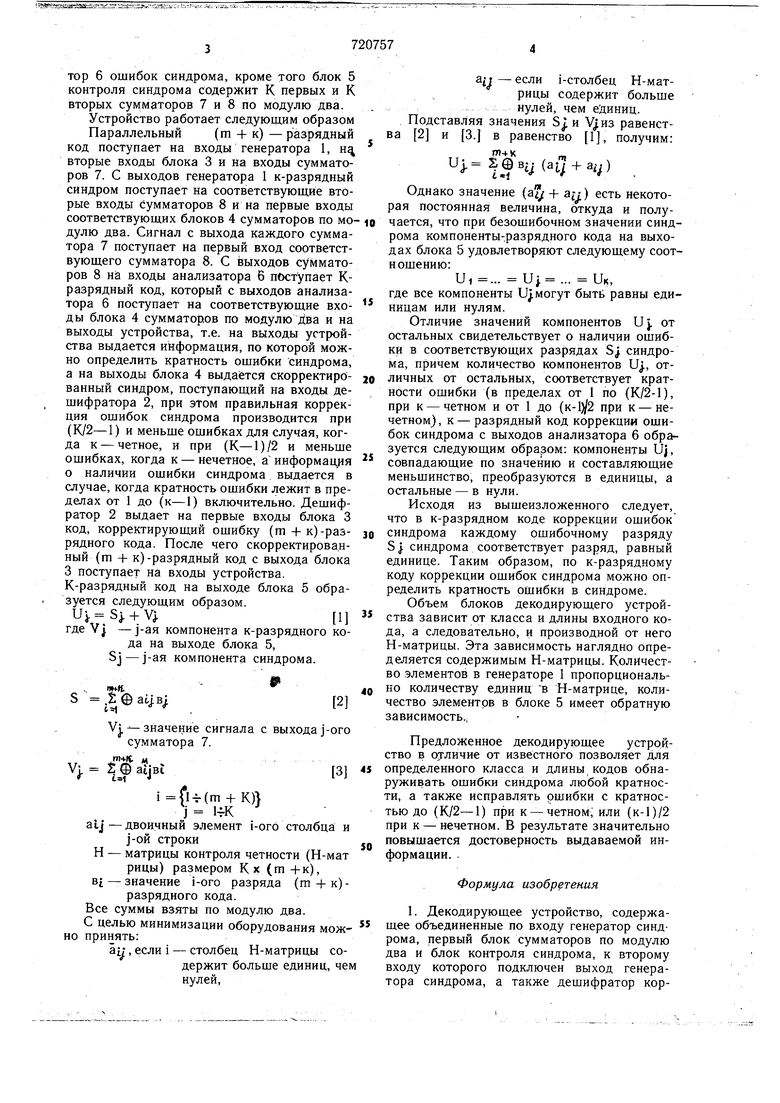

На чертеже приведена структурная схема предложенного устройства.

Декодирующее устройство содержит генератор 1 синдрома,дешифратор 2 коррекции ошибок, первый блок 3 сумматоров по модулю два, второй блок 4 сумматоров по модулю два, блок 5 контроля синдрома, анализатор б ошибок синдрома, кроме того блок 5 контроля синдрома содержит К первых и К вторых сумматоров 7 и 8 по модулю два. Устройство работает следующим образом Параллельный (т + к) - разрядный код поступает на входы генератора 1, н вторые входы блока 3 и на входы сумматоров 7. С выходов генератора 1 к-разрядный синдром поступает на соответствующие вторые входы сумматоров 8 и на первые входы соответствующих блоков 4 сумматоров по модулю два. Сигнал с выхода каждого сумматора 7 поступает на первый вход соответствующего сумматора 8. С Выходов сумматоров 8 на входы анализатора 6 поступает Кразрядный код, который с выходов анализатора 6 поступает на соответствующие входы блока 4 сумматоров по модулю Ива и на выходы устройства, т.е. на выходы устройства выдается информация, по которой можно определить кратность ошибки синдрома, а на выходы блока 4 выда1ется скорректированный синдром, поступающий на входы дешифратора 2, при этом правильная коррекция ошибок синдрома производится при (К/2-1) и меньше ошибках для случая, когда к - четное, и при (К-1)/2 и меньше ошибках, когда к - нечетное, а информация о наличии ошибки синдрома выдается в случае, когда кратность ошибки лежит в пределах от 1 до (к-1) включительно. Дешифратор 2 выдает на первые входы блока 3 код, корректирующий ошибку (п1 + к)-разрядного кода. После чего скорректированный (т + к)-разрядный код с выхода блока 3 поступает на входы устройства. К-разрядный код на выходе блока 5 образуется следующим образом. + где V j - j-ая компонента к-разрядного кода на выходе блока 5, Sj - j-ая компонента синдрома. Sl-ft S Дфаув; 1 -значение сигнала с выходаj-oro сумматора 7. . JK Vj. t,® atJBi 3 (m + K)} j alj-двоичный элемент i-ого столбца и j-ой строки Н - матрицы контроля четности (Н-мат рицы) размером Кх (т +к), в - значение i-oro разряда (т + к)разрядного кода. Все суммы взяты по модулю два. С целью минимизации оборудования можно принять: ail. если i - столбец Н-матрицы содержит больше единиц, че

720757 ац - если i-столбец Н-матрицы содержит больше нулей, чем единиц. Подставляя значения S и равенста 2 и 3. в равенство 1, получим: .t, Uj. |@Bij (а5 + а.у) Однако значение (а + an) есть некоторая постоянная величина, откуда и получается, что при безошибочном значении синдрома компоненты-.разрядного кода на выходах блока 5 удовлетворяют следующему соотношению:и,... Ui... UK, где все компоненты U могут быть равны единицам или нулям. Отличие значений компонентов Uj. от остальных свидетельствует о наличии ошибки в соответствующих разрядах S синдрома, причем количество компонентов U, отличных от остальных, соответствует кратности ошибки (в пределах от 1 по (К/2-1), при к - четном и от 1 до (к-1)/2 при к - нечетном), к - разрядный код коррекции ошибок синдрома с выходов анализатора 6 образуется следующим образом: компоненты Uj, совпадающие по значению и составляющие меньшинство, преобразуются в единицы, а остальные - в нули. Исходя из вышеизложенного следует, что в к-разрядном коде коррекции ошибок синдрома каждому ошибочному разряду S) синдрома соответствует разряд, равный единице. Таким образом, по к-разрядному коду коррекции ошибок синдрома можно определить кратность ошибки в синдроме. Объем блоков декодирующего устройства зависит от класса и длины входного кода, а следовательно, и производной от него Н-матрицы. Эта зависимость наглядно определяется содержимым Н-матрицы. Количество элементов в генераторе 1 пропорционально количеству единиц в Н-матрице, количество элементов в блоке 5 имеет обратную зависимость., Предложенное декодирующее устройство в отличие от известного позволяет для определенного класса и длины кодов обнаруживать ошибки синдрома любой кратности, а также исправлять ошибки с кратностью до (К/2-1) при к -четном; или (к-1)/2 при к - нечетном. В результате значительно повышается достоверность выдаваемой информации. . Формула изобретения 1. Декодирующее устройство, содержащее объединенные по входу генератор синдрома, первый блок сумматоров по модулю два и блок контроля синдрома, к второму входу которого подключен выход генератора синдрома, а также дешифратор коррекции ошибок, выход которого подключен к второму входу первого блока сумматоров по модулю два, отличающееся тем, что, с целью повышения достоверности информации, введены последовательно соединенные анализатор ошибок синдрома и второй блок сумматоров по модулю два, выход которого подключен к входу дешифратора коррекции ошибок, а к второму входу второго блока сумматоров по модулю два подключен, выход генератора синдрома, при этом к входам анализатора ошибок синдрома подключены выходы блока контроля синдрома.

Источники информации, принятые во внимание при экспертизе 1. Патент США № 3891969, кл. 340-146, IA L (прототип).

Авторы

Даты

1980-03-05—Публикация

1977-12-30—Подача