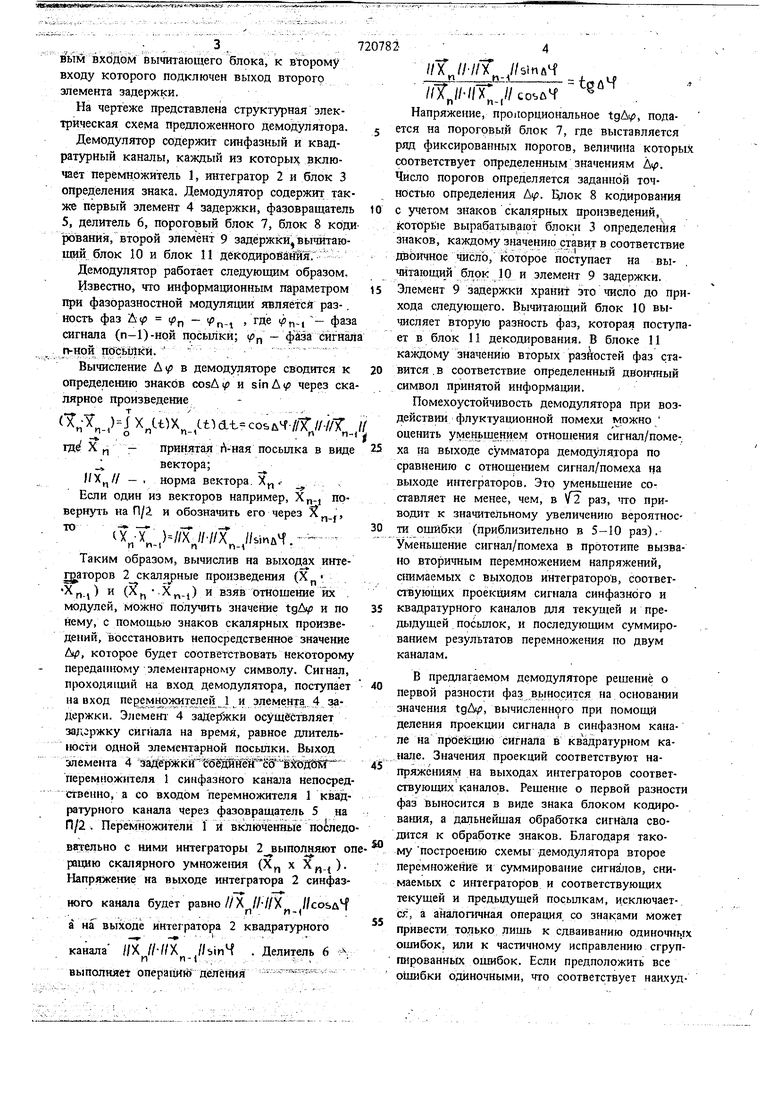

(54) ДЕМОДУЛЯТОР СИГНАЛОВ С ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ . ; 3 .,. ; .. вь1Й вхОдбм вычитающего блока, к второму входу которого подключен выход второго элемента задержки. На чертеже представлена структурная электрическая схема предложенного демодулятора. Демодулятор содержит синфазный и квадратурный каналы, каждый из которых вклю«иет перемнржитель 1, интегратор 2 и блок 3 определения знака. Демодулятор содержит; также первый элемент 4 задержки, фазовращатель 5, делитель 6, пороговый блок 7, блок 8 коди рования, второй элемент 9 задержки вычитающий блок 10 и блок 11 дёКодировйнЮ. Демодулятор работает следующим образом. Известно, что информационным параметром при фазоразностной модуляции являётсА раз-. кость фаз Л „ - Vn-i где Ф сигнала (п-1)-ной посылки; i/)p - фйэа ййгнал п-ной прсьШкй. - ; - Вычисление А tp в демодуляторе сводится к определению знаков cosAi и sinAi i через ска лярное произведение .-,1 .,tOdt cosA4.T/-//X,/ гд X тп Х„ - поиНятая Л-ная посылка в виде принятая Л-ная посылка в виде вектора; -. норма вектора. Х„ . Если один из векторов например, X.j повернуть на П/1 и обозначить его через J.j, ™ X.b/a//.//x,.//sm.4.--:- Таким образом, вычислив на выходах иктещаторов 2 cкaляJ)ныe произведения (X Х) и ( ) и взяв отношение их . модулей, Можнс получить значение tgl и по Нему, с помощью знаков скалярных произведений, восстановить непосредственное значение f, которое будет соответствовать Некоторому переда1пюму элементарному символу. Сигнал, проходящий на вход демодулятора, поступает на вход перемно а; телей элемента, 4 задержки. Элемент 4 заДерзккИ осуществляет заг1.сржку сигнала на время, равное длитель1юсти одной элементарной посылки. Выход элемента 4 т фкттШё 1 Ш0Ш перемножителя 1 синфазного канала непосредственно, а со входом перемножителя 1 квадратурного канала Через фазовращатель 5 на П/2 . Пер1емножители Т и вйллченные вггельно с ними интеграторы 2 выполняют on рацию скалярного умноже1шя (Х х Х). Напряжение на выходе интегратора 2 синфазного канала будет равно//X ////Х //соьдМ а на выходе интегратора 2 квадратурного //Х///Х //.1пЧ . Делитель 6 выполняет операций) деления ---- .//7,,//sinA4. //T //-//X,//cosu4 Напряжение, пропорциональное , подается на пороговый блок 7, где выставляется ряд фиксированных порогов, величина которых соответствует определенным значениям . Число порогов определяется заданной точностью определения Aip. Цлок 8 кодирования с учетом знаков скалярных произведений, которые вырабатывают блоки 3 определения знаков, каждому значению ставит в соответствие двоичное число, которое поступает на вычитающи й блок 10 и элемент 9 задержки, Элемент 9 задержки хранит это число до прихода следующего. Вычитающий блок 10 вычисляет вторую разность фаз, которая поступает в блок 11 декодирования. В блоке 11 каждому значению вторых разАостей фаз ставится . в соответствие определенный двошшый символ принятой информации. Помехоустойчивость демодулятора при воздействии флуктуационной помехи можно оценить уменьшением отношения сигнал/поме-, ха на выходе сумматора демодулятора по сравнению с отношетшем сигнал/помеха на выходе интеграторов. Это уменьшение составляет не менее, чем, в VT раз, что приводит к значительному увеличению вероятности ошибки (приблизительно в 5-10 раз). Уменьшение сигнал/помеха в прототипе вызвано вторичным перемножением напряжений, снимаемых с выходов интеграторов, соответаВующих проекциям сигнала синфазного и квадратурного каналов для текущей и предыдущей посылок, и последующим суммированием результатов перемножения по двум каналам. В предлагаемом демодуляторе решение о первой разности фаз вьтносдтся на основании значения , вычисленного при помощи деления проекции сигнала в синфазном канале на проекцию сигнала в квадратурном канале. Значения проекций соответствуют напряжениям на выходах интеграторов соответствующих каналов. Рещение о первой разности фаз выносится в виде знака блоком кодироваьшя, а дальнейшая обработка сигнала сводится к обработке знаков. Благодаря такому построению схемы -демодулятора второе перемножение и суммирование сигналов, снимаемых с интеграторов и соответствующих текущей и предыдущей посылкам, исключаетЬг, а аналогичная операция со знаками может привести только дищь к сдваиванию одиночнь.1х ошибок, или к частичному исправлению сгруппированных ошибок. Если предположить все о11шбки одиночными, что соответствует наихудшему варианту для данного демодулятора, то произойдет увеличение вероятности ошибочного приема в 2 раза. Но даже ив этбм маловероятном случае помехоустойчивость предлагаемого демодулятора в 2,5-5 раз будет выше, чем у известного.

Формула изобретения

Демодулятор сигналов с фазоразностной модуляцией, содержащий последовательно соединенные первый злемент задержки и фазовращатель, второй злемент задержки, а также синфазный и квадратурный каналы, каждый из которых состоит из последовательно соединенных перемножителя и интегратора, при этом первые входы перемножителей соединены с входом первого элемента задержки, выход которого подключен к второму входу перемножителя синфазного канала, а выход фазовращателя соединен с вторым входом перемножителя квадратурного канала, отличающий с я тем, что, с целью повтлшения помехоустоЙ1 ивости, введены последовательно соединенные делитель, пороговый блок и блок кодирования и последовательно соединенные вычитающий блок и блок декодирования, а в квадратурный и синфазный каналы введен блок определения знака, вход которого соединен с выходом интегратора и входом делителя, причем выходы блоков определения знака подключены к соответствующим входам блока кодирования , выход которого соединен с входом второго элемента задержки и первым входом вычитающего -блока, к второму входу которого подключен выход второго элемента

5 задержки/

Источники информации, принятые во внимание при экспертизе 1. Заездный А. М. и др. Фазоразностная модуз1яция. М., Связь, 1967, с. 284 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор сигналов с фазоразностной модуляцией | 1978 |

|

SU790361A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2000 |

|

RU2168869C1 |

| Когерентный демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU906023A1 |

| Демодулятор фазомодулированных сигналов | 1990 |

|

SU1748279A1 |

| Устройство приема сигналов с трехкратной фазоразностной модуляцией | 1989 |

|

SU1635276A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ С ПОМОЩЬЮ ШУМОПОДОБНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2007 |

|

RU2362273C2 |

| Автокорреляционный демодулятор сигналов с фазоразностной модуляцией первого порядка | 1987 |

|

SU1425869A1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| Автокорреляционный демодулятор псевдослучайных сигналов с относительной фазовой модуляцией второго порядка | 2017 |

|

RU2660594C1 |

&х

Bail

Авторы

Даты

1980-03-05—Публикация

1978-07-03—Подача