(54) ЦИФРОАН.4ЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2824647C1 |

| Функциональный генератор | 1979 |

|

SU822213A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1398099A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ УРОВНЯ ГРОМКОСТИ | 2014 |

|

RU2562371C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1095389A1 |

| Двоично-десятичный цифроаналоговый преобразователь | 1987 |

|

SU1575313A1 |

| Двоично-десятичный цифроаналоговый преобразователь | 1980 |

|

SU995307A1 |

| Преобразователь кода в напряжение | 1980 |

|

SU959273A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в аналого-цифровых вычислительных устройствах и системах автоматического управления.

Известен преобразователь кода в напряжение, содержащий резистивный делитель R-2R, источник эталонного напряжения, основной и дополнительный ключи на транзисторах в каждом разряде, суммирующий усилитель, причем коллектор транзистора дополнительного ключа через резистор 4R подключен к узловой точке резистивного делителя, а вход суммирующего усилителя подключен через дополнительный резистор 2R к общей точке основного резистора 2R и коллектора основного ключа. В старщих разрядах преобразователь содержит другой дополнительный ключ на транзисторе, база которого подключена к базе основного ключа, а эмиттер через дополнительный резистор R соединен с коллектором основного ключа и через другой дополнительный резистор R - с входом суммирующего усилителя 1.

Разрешающая способность и точность такого преобразователя определяются, в первую очередь, точностью формирования тока

старшего разряда, которая не может быть выше точности токозадающего резистора.

Известен также преобразователь цифрового кода в напряжение, содержащий ключи управляемые преобразуемым кодом, входы которых соединены с источником эта.юнного напряжения постоянного тока, а выходы через резисторы R. 2R, 4R и т. д. подключены к суммирующему усилителю 2. Разрешающая способность этого устройства непосредственно определяется точностью резистора старшего разряда.

Целью изобретения является повышение разрешающей способности цифроаналогового преобразователя.

Поставленная цель достигается тем, что в цифроаналоговый преобразователь, содержащий выходной сумматор и преобразователь двоичного кода в напряжение, вход которого подключен к источнику эталонного напряжения, а управляющие входы - к un-iнам младших разрядов п-разрядного прообразуе.мого кода, введен преобразователь двоичного кода в унитарный, в.ходы которого соединены с шипами старших разрядов преобразуемого кода, а выходы подключены к управляющим входам ключей, включенных между источником эталонного напряжения и входами выходного сумматора, при этом выход преобразователя двоичного кода в напряжение также подключен к входу выходного сумматора, коэффициенты передачи которого по всем входам одинаковы.

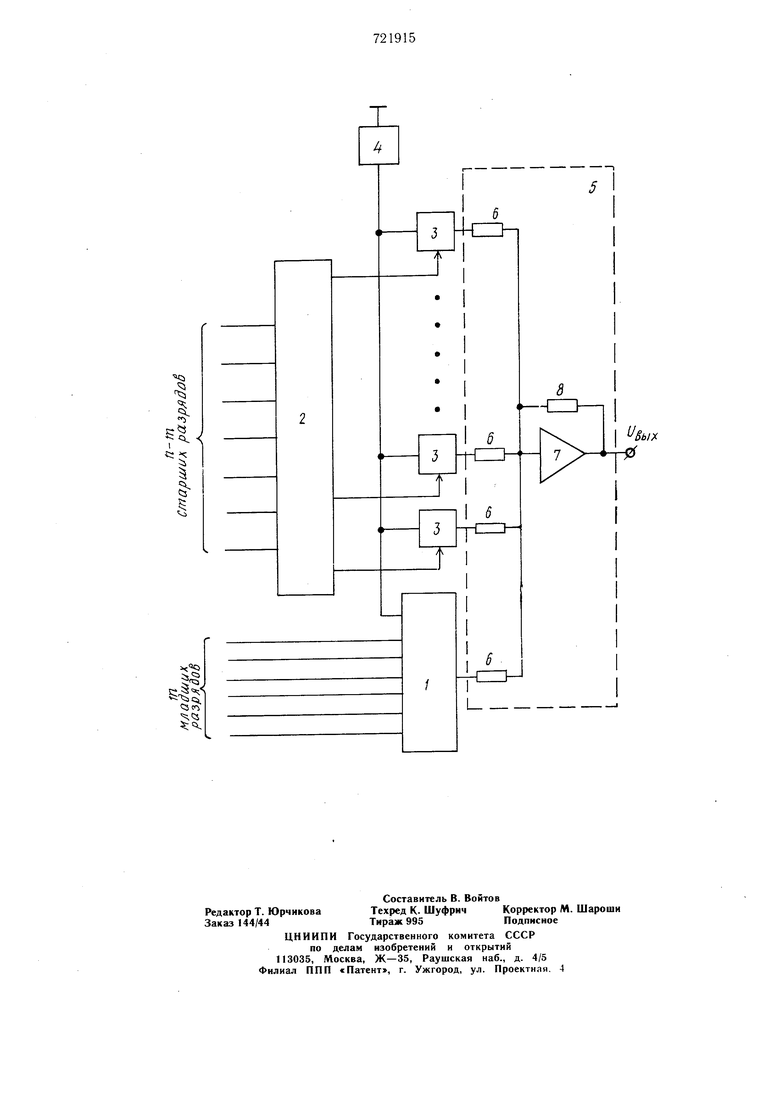

Структурная электрическая схема преобразователя показана на чертеже.

Управляющие входы преобразователя цифрового кода в напряжение 1, выполненного по известной схеме, подключены к шинам ш младших разрядов преобразуемого числа, шины п-ш старших разрядов подключены к входам преобразователя двоичного кода в унитарный 2. Выходы преобразов теля 2 подключены к управляюшим входам ключей 3. Входы ключей и вход преобразователя 1 соединены с источником эталонного напряжения 4. Выходы ключей и выход преобразователя 1 через одинаковых входных резисторов 6 выходного сумматора 5 подключены к суммирующей точке решающего усилителя 7, в цепи обратной связи которого включен резистор 8.

Работает цифроаналоговый преобразователь следующим образом.

По мере роста преобразуемого числа от нуля до 2 происходит заполнение преобразователя 1, напряжения на выходных шинах преобразователя 2 равны нулю и все ключи 3 разомкнуты. Напряжение с выхода преобразователя 1 поступает на вход выходного сумматора 5 с весовым коэффициентом, следовательно, и погрешность в этой ветви по отношению к максимальной величине выходного напряжения преобразователя уменьшается во столько же раз. По достижении входным кодом величины 2 преобразователь 1 обнуляется, на одной шине преобразователя 2 появляется напряжение, замыкается один из ключей 3 и на вход выходного сумматора 5 поступает напряжение эталонного источника 4 с весовым коэффициентом. При дальнейшем росте числа снова начинает заполняться преобразователь 1. При его переполнении замыкается еще один ключ и он вновь обнуляется. При дальнейшем росте входного числа преобразователь 2 работает аналогично, пока не замкнутся все ключи и не заполнится преобразователь 1, что соответствует максимальному числу на входе устройства.

Данное устройство выгодно отличается от прототипа тем, что при использовании элементов того же класса точности его более высокая разрешающая способность может служить основой повышения общей точности преобразования на несколько разрядов в тех практических случаях, когда по условиям работы возможна периодическая регулировка резистора обратной связи 8 в выходном, сумматоре 5.

Формула изобретения

Цифроаналоговый преобразователь, содержащий выходной сумматор и преобразователь двоичн.ого кода в напряжение, вход которого подключен к источнику эталонного напряжения, а управляющие входы - к щинам младщих разрядов п-разрядного преобразуемого кода, отличающийся тем, что,

с целью повышения его разрешающей способности, в него введен преобразователь двоичного кода в унитарный, входы которого соединены с шинами старших разрядов преобразуемого кода, а выходы подк тючены к управляющим входам ключей, включенных между источником эталонного напряжения и входами выходного сумматора, при этом выход преобразователя двоичного кода в напряжение также подключен к входу выходного сумматора, коэффициенты перадачи которого по всем входам одинакоВЫ.

Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР № 324704, кл. Н 03 К 13/04, 30.07.70. 2. Шило В. Л. Линейные интегральные схемы в радиоэлектронной аппаратуре. М., 1974, с. 266, рис. 8.14 (прототип).

§

s

fc: X 5i

§

a

«

EiJv

Cst 4Cs

Авторы

Даты

1980-03-15—Публикация

1977-07-27—Подача