Ч

t

I-

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах преобразования цифровой информации в анало- говук 3 а также в цифровых измерительных приборах.

Цель изобретения - повышение точности преобразования и уменьшение величины коммутационных в,ыбросов выходного сигнала.

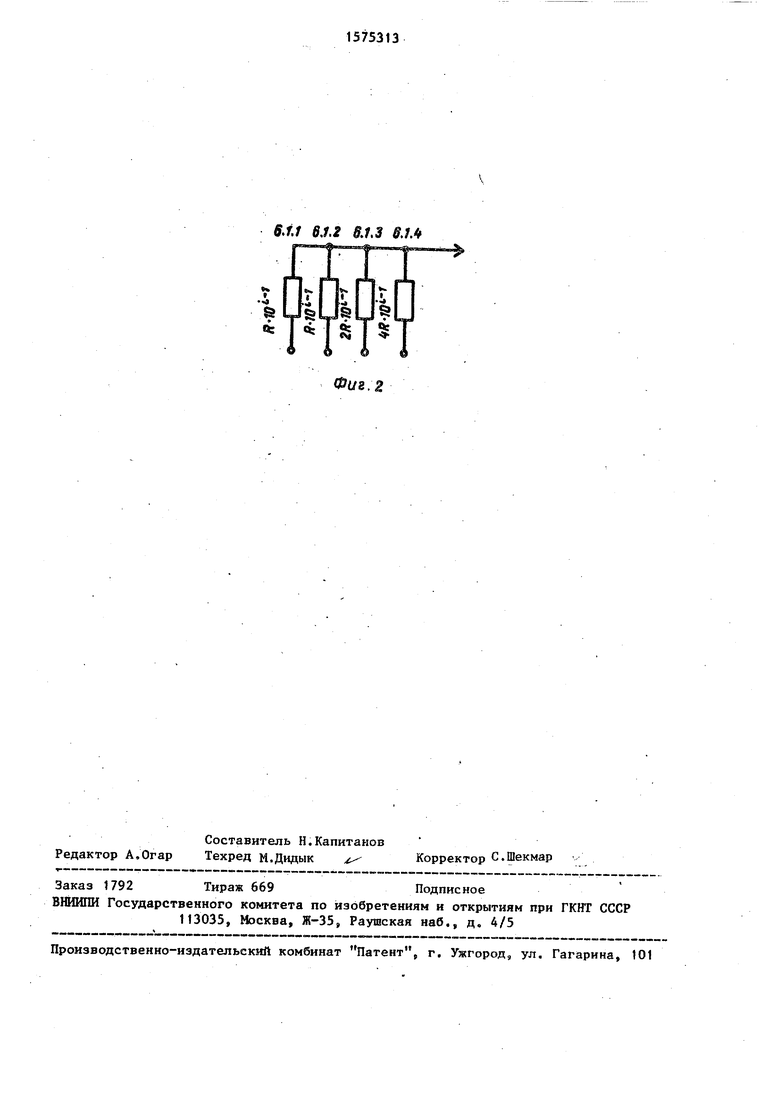

На фиг.1 представлена функциональная схема устройства; на фиг.2 - реализация резистивной матрицы.

Двоично-десятичный цифроаналого- вый преобразователь (фиг.1) содержит преобразователь т ток - напряжение, выходную шину 29 п декадных преобразователей 3 код - ток, выполненных виде четырехразрядного регистра 4-j блока 5 ключей, резистивной марицы 6 и преобразователя 7 код - код на элементе ИЛИ, входную шину 8 преобразуемого кода и входную шину 9 установки. Резистивная матрица 6 каждого преобразователя 3 выполнена на четырех резисторах, сопротивления которых относятся как целые числа 1:1:2:4.

Двоично-десятичный цифроаналого- вый преобразователь (фиг.1) работает следующим образом

После поступления команды занесения по шине 9 в регистры 4 заносится значение преобразуемого кода N6X, поступающего на входную шину 8. Преобразуемый код с выхода регистра преобразователя 3 код - ток поступает на управляющие входы блока 5.i .ключей, на информационный вход которого подается опорное напряжение, одинаковое для всех блоков 5 ключей. При этом сигналы с выходов первого (старшего), третьего и четвертого (младшего) разрядов регистра 4 поступают непосредственно на соответствующие управляющие входы блока 5 ключей, на второй вход которого поступает сигнал с выхода элемента ИЛИ 7, первый и второй входы которого соединены соответственно с выходами первого и второго разрядов регистра 4. При этом если на входе регистр 4 Присутствует код . в виде двоично-десятичного кода в системе счисления 8-4-2-1, то на управляющих входах блока 5 ключей формируется код а4() а3а4, где знак V обо- значет операцию логического сложения

o

5

0

5

В соответствии со значением полученного кода включаются соответствующие ключи блока 5 ключей, подавая на соответствующие входы резистивной Матрицы 6 напряжение Uon эталонного источника сигнала. Резистивная матрица каждого декадного преобразователя 3 код - ток выполнена на четырех резисторах (фиг.2), сопротивления которых соотносятся как R:2iKr R:4., где i 1, 2,..., п. Токи с резистивных матриц 6 поступают на преобразователь 1 ток - напряжение. На выходе преобразователя Т (последний реализуется на операционном усилителе с резистором в цепи отрицательной обратной связи) формируется напряжение, пропорциональное значению преобразуемого кода N0X.

Для пояснения достижения повышения точности преобразования входного кода предположим, что код младших декад () имеет нулевое значение. Тогда ток на выходе резистивной матрицы 6.1 старшего декадного преобразователя 3.1

чи

R

оп

(а, V а,)

U on

+ -, if . IT - UP (4a-+

+4(а, V аг)+2а,+а4).

I В соответствии с полученным выражением нетрудно убедиться что первые восемь входных комбинаций обеспечивают получение пропорциональных токов так же, как и в схеме известного преобразователя.

При поступлении входного кода а, 1000 срабатывают сразу два ключа блока 5.1, так как на управляющие входы этих ключей поступает единичный сигнал с выхода первого разряда регистра 4.1. В этом случае общий ток на выходе резистивной матрицы

Uon 4R

(4+4+0+0)

-Q и°п

-8

При поступлении кода 1001 срабатывает также и четвертый ключ блока 5.1, так как на его цифровом входе появляется сигнал 1, поэтому общий ток становится равным

Ч If- 4+4+0+1 - 9ff 15/5313

выброс, равный 4 ед. МЗР, т.е. я 2 раза меньший по величине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1979 |

|

SU964981A1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| Преобразователь цифрового кода в частоту следования импульсов | 1983 |

|

SU1169170A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1982 |

|

SU1112301A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ УРОВНЯ ГРОМКОСТИ | 2014 |

|

RU2562371C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах преобразования цифровой информации в аналоговую, а также в цифровых измерительных приборах. Цель изобретения - повышение точности и уменьшение коммутационных выбросов выходного сигнала. Двоично-десятичный цифроаналоговый преобразователь содержит преобразователь 1 код-напряжение, выходную шину 2, N декадных преобразователей 3.1-3.N код-ток, в состав каждого из которых входят четырехразрядный регистр 4, блок 5 ключей, резистивная матрица 6 и преобразователь 7 код-код на элементе ИЛИ, входные шины 8.1-8.N преобразуемого кода и входную шину 9 установки в нулевое состояние. Резистивная матрица 6 каждого преобразователя 3 выполнена на четырех резисторах, сопротивления которых относятся как целые числа 1:1:2:4. 1 з.п. ф-лы, 2 ил.

В преобразователе абсолютные погрешности для токов I,, Ife, 1, 1, протекающих соответственно через резисторы 6.1.1-6. 1.4. первой декады, при одинаковых для каждого тока относительных погрешностях V равны:

«Ь -fr1 r s &Jt У1.; j

2

Л1

jfi,; Ai4

-1 Jff

4 0ч

где I

U0n/2.

Следовательно, максимальная солютная погрешность выходного первой декады 4

А1гk i

к-f fl

f

Максимальное значение выходного тока при входном коде 1001

т 1т

2 макс 4 1

Таким образом, максимальная приведенная погрешность

.,-ayi.

-11 кч

О и 11

:/WCIKC 9 В известном устройстве при этом е значении $ получают

8

У

1

что в 1,36 раз больше, чем

в предлагаемом устройстве.

Коммутационные выбросы обусловлены различием во времени срабатывания ключевых элементов. Как правило, ключевые элементы в нулевое состояние переходят быстрее, чем в единичное. В связи с тем, что в известной и предлагаемой схемах первые восемь кодовых комбинаций совпадают, выброс в первых семи позициях не отличаются Отличие будет при изменении входного кода с кодовой комбинацией 0111 в кодовую комбинацию 1000. В известной схеме при этом на выходе появляется выброс, равный 8 ед. МЗР (в зависимости от соответствующего приращения тока «) . В предлагаемом устройстве при аналогичной ситуации появляется

0

5

0

5

0

5

0

5

0

Формула изобретения

с целью повышения точности преобразования и уменьшения величины коммутационных выбросов выходного сигнала, в каждый декадный преобразователь код - ток введен преобразователь код - код, выполненный на элементе ИЛИ, выход которого соединен с вторым входом управления блока ключей, а первый и второй входы соединены с выходами соответственно первого и второго разрядов четырехразрядного регистра.

Фиг. %

| Зангер К | |||

| Электронные системы | |||

| Теория и применение | |||

| М.: Мир, 1980 | |||

| Двоично-десятичный цифроаналоговый преобразователь | 1980 |

|

SU995307A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-06-30—Публикация

1987-12-28—Подача