Изобретение относится к вычислительной технике. Известно устройство .для контроля логических блоков, содержащее регис сдвига и последовательно соединенные блок ввода программы, генератор тес тов, дешифраторы, формирователь импульсов, элементы ИЛИ, И сумматор по модулю два 1. Недостатком данного устройства является то, что локализация неисправных элементов осуществляется без обнаружения их местоположения. Наиболее близким техническим реше нием к данному изобретению является устройство для контроля дискретных логических схем, содержащее двоичный счетчик, вход которого подключен к генератору импульсов, а выходы по соединены ко входам разделительных схем, выходы которых соединены с выходами устройства, триггер неисправности с индикаторными элементами на выходах и первым элементом И на нулевом входе, первый вход которого подключен через формирователь стробирующих импульсов к генератору импульсов, а второй вход соединен с выходом первого элемента ИЛИ, подключенного первым входом к выходу компаратора, входы которого подключены ко входам устройства через схему контроля уровней и преобразователь уровней, входы элементов ИЛИ-НЕ и элемента ИЛИ соединены с выходами соответствующих разделительных схем, а также второй элемент И, входы которого соединены с выходами второго элемента ИЛИ и элемента ИЛИ-НЕ а выход подключен ко второму входу первого элемента . Недостатком известного устройства является то, что оно не указывает местонахождение отказа. Цель изобретения - увеличение полноты контроля. Цель достигается тем, что в устройство для контроля логических блоков, содержащее триггер запуска, генератор импульсов, двоичный счетчик элементы ИЛИ, триггер неисправности, блок индикации, причем первый вход триггера запуска является входом устройства, вторюй вход триггера запуска подключен к выходу первого элемента ИЛИ, первый вход которого является управляющим входом устройства, к первому .входу двоичного счетчика и к первому входу триггера неисправности, второй вход которого

соединен е выходом второго элемента ИЛИ выход третьего -элемента ИЛИ соединен со входом блока индикации, в устройство введены трехвходовой элемент И, дешифратор и п-блоков анализа, каждый из которых содержит два элемента И и элемент НЕ, причем в каждом блоке анализа первый вход первого элемента и является входом устройства и подключен ко входу элемента НЕ, выход элемента НЕ подключен к первому входу второго элемента И, второй вход которого соединен со вторым входом первого элемента И и подсоединены к одному из п-выходов дешифратора, выходы первых элементов К подключены соответственно к входам третьего элемента ИЛИ, выходы вторых элементов И подключены соответственно к входам второго элемента ИЛИ, выход .триггера неисправности соединен с первым входом трехвходового элемента И, второй вход которого подключен к выходу генератора импульсов, а третий вход к выходу тригегра запуска, выход элемента И подключен ко второму входу двоичного счетчика и к первой группе входов дешифратора, вторая группа входов КОТОРОГО соединена с группой .выходов двоичного счетчика, (п.)-1)-й выход дешифратора подключен ко второму входу первого элемента ИЛИ.

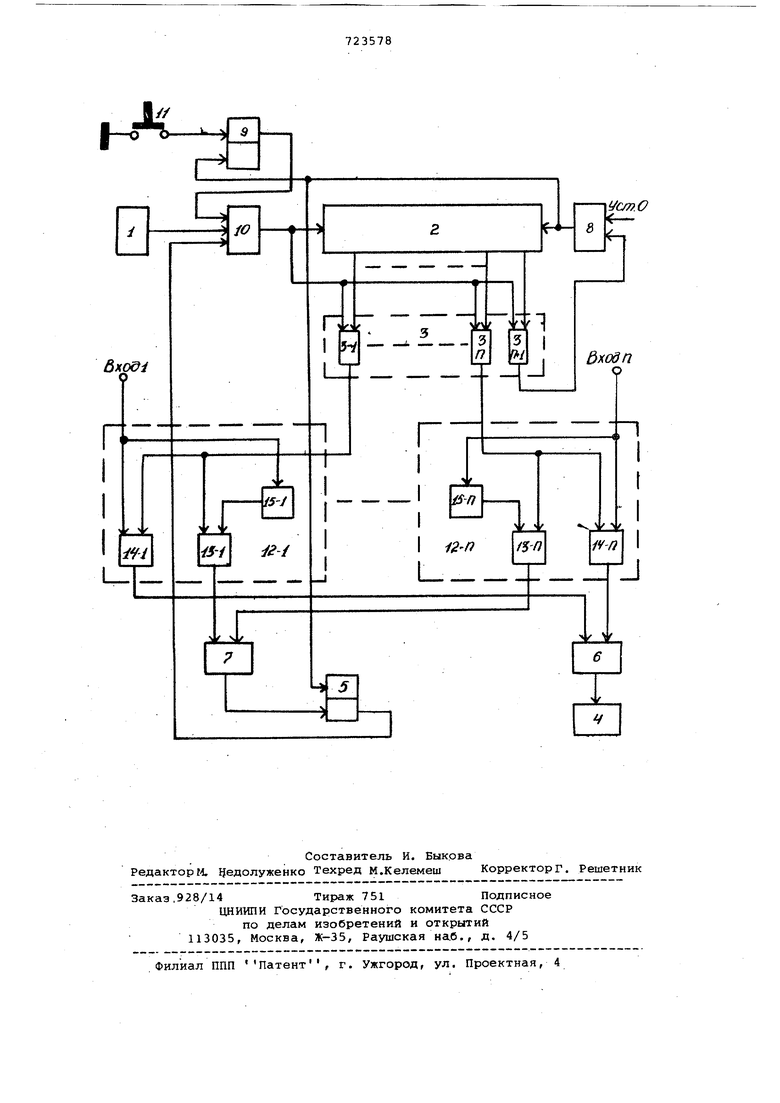

Предлагаемое устройство представлено на чертеже.

Устройство содержит генератор 1 импульсов, двоичный счетчик 2, выходы которого соединены с потенциальными, входами дешифратора 3, блок 4 индикации,триггер неисправности 5, элементы 6, 7, и 8 ИЛИ;триггер запуска 9, элемент 10 И, кнопку 11 пуск и блоков 12-п анализа. Каждый блок анализа состоит из элемента 13 И, элемента 14 И и элемента 15 НЕ.

Устройство работает следующим образом.

Сигналом.начальной установки устройство приводится в исходное состояние. На ; входах блоков анализа 12-1 и 12-п при условии исправности проверяемых приборов присутствует

1

котор лй подается

потенциал

на первые входы элементов 14 И. под.готавливая их к срабатыванию. Потенинвертируется элементом

циал

15 НЕ ив качестве потенциала запрета подается на первые входы элементов И 13.

При нажатии кнопки пуск 11 разрешающий потенциал i с триггера запуска 9 поступает на элемент 10 И, который при этом пропускает с генеfiaTopa 1 импульсы тактовой частоты на двоичный счетчик 2. Группа выходов двоичного счетчика соединена со второй входов дешифратора . п-выходов дешифратора последовательно опраши.вают по вторым входам элементы 13 И и 14 И блоков анализа.

На выходах элементов 14 И, подготовленных к срабатыванию, потенциалом , образуются сигналы, которые проходят через элемент ИЛИ б, отсчитываются блоком индикации 4.

На блоке 4 индикации высвечивается цифра, равная количеству проверяемых приборов. Это говорит о том, что, все приборы исправны.Сигнал с (п+1)-г выхода дешифратора 3 через элемент 8 ИЛИ устанавливает двоичный счетчик 2 и триггеры 5 и 9 в исходное состояние.

В случае неисправности одного из проверяемых приборов, например п-го, на блок анализа 12-п будет подаваться

О

запрещающий потенциал.

на первый вход элемента 14-п И и разрешающий - на первый вход элемента 13-п И. В этом случае на всех остальных блоках анализа 12 и на первые входы элементов 14-1 и 14-п И будет подаваться разрешающий, а на первые входы элементов 13-1 и 13-п И запрещающий потенциал. При нажатии кнопки пуск 11 происходит п ос ледов ат ель в€ый опрос блоков 12 анализа сигналом сдешифратора 3. Блок 4 индикации отсчитывает сигналы от исправных приборов до тех пор, пока дешифратор 3 не опросит блок 12-п анализа, на вход которого

О

от неисправноподан потенциал

го прибора. При этом срабатывает элемент 13-п И. Выходной сигнал с элег ента 13-п И через элемент 7 ИЛИ устанавливает триггер неисправности 5 в такое состояние, при котором закрывается элемент 10 И и прекращается поступление импульсов от генератора импульсов 1 на двоичный счетчик 2 и дальнейший опрос блоков анализа также прекращается.

При этом счетчик 2 сохранит состояние, при котором опрашивался дешифратором 3 элемент неисправности 13-п. На табло цифрового индикатора устанавливается цифра, которая является номером последнего исправного прибора (п-1) перед неисправным прибором п. После замены неисправного прибора, контроль повторяется.

Данное устройство позволяет также фиксировать короткое замыкание выходных цепей. В этом случае исправный прибор фиксируется как неисправный. После замены прибора и повторения проверки делается вывод о коротком замыкании входной цепи устройства.

Например, произошло замыкание входов {п-1) и п соответствующих блоков анализа, причем прибор п при этом является неисправным.

В этом слу:ае на выходе элемента 14 (п-1) И будет запрещающий потенциал несмотря на то, что прибор (ii-l) исправен, а на входе 13 (п-1)-разрешакидий. Сигнал с выхода элемента 13 (п-1) через элемент 7 ИЛИ устанав ливает триггер неисправности 5 в такое состояние, при котором сигнал с его выхода закроет элемент И lOj и счетчик остановится в таком состояни при котором выбран (пт1) блок анализ На цифровом индикаторе высвечена циф ра {п-2). При замене прибора (п-1) неисправность повторяется. При этом произошло замыкание входа (п-1) со входом п, который является неисправным. Устройство показывает аналогичную неисправность, если произошло короткое замыкание входа -(п-1) устройства на корпус. Таким образом, при всех исправных приборах на блоке индикации фиксируется общее количество проверяемых приборов; функциональные возможности устройства расширены, за счет того, что оно позволяет вести неисправного прибора. Формула изобретения Устрюйство длд контроля логичес них блоков, содержащее триггер запус ка, генератор импульсов, двоичный счетчик, элементы РШИ, триггер неисправности, блок индикации, причем пе вый вход триггера запуска является входом устройства, второй вход трих- гера запуска подключен к выходу первого элемента ИЛИ, первый вход которого является управляющим входом уст ройства, к первому входу двоичного счетчика и к первому входу триггера неисправности, второй вход которого соединен с выходом второго элемента ИЛИ, выход третьего элемента ИЛИ соединен со входом блока индикации, отличающееся тем, что, с целью увеличения полноты контроля, устройство содержит трехвходовой элемент и,ДешифраторИ п-блоков анализа, каждый из которых содержит два элемента И и элемент НЕ, причем в каждом блоке анализа первый вход первого элемента И является входом устройства и подключен ко входу элемента НЕ, выход элемента НЕ подключен к верному входу второго элемента И, второй вход которого соединен со вторым входом первого элемента И и подсоединены к одному из п-вккодов дешифратора, выходы первыхэлеме нтов и -подключены соответственно к входам третьего элемента ИЛИ, выходы вторых элементов И подключены соответственно ко входам второго элемента ИЛИ, выход триггера неисправности соединен с первЕлм входом трехвходового элемента И, второй вход которого подключен к выходу генератора импульсов, а третий вход - к выходу триггера запуска, выход элемента И подключен ко второму входу двоичного счетчика и к первой группе входов дешифратора, вторая группа входов которого соединена с группой выходов двоичного счетчика (п4-1)-й выход дешифратора подключен ко второму входу первого элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 558266, кл. G 06 F 11/04, 1975.. 2,Авторское свидетельство СССР № 451994, кл. G 06 F 11/00, 1973 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блокаСРАВНЕНия дВуХ чиСЕл | 1978 |

|

SU798843A1 |

| Устройство для автоматического контроля и поиска неисправностей | 1977 |

|

SU696463A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1988 |

|

SU1524084A1 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| МНОГОКАНАЛЬНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ С ЗАЩИТОЙ | 1990 |

|

RU2011258C1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1264186A1 |

| Устройство для автоматического контроля и поиска неисправностей | 1980 |

|

SU968817A1 |

| Устройство для контроля полупроводниковых диодов | 1982 |

|

SU1064243A1 |

| Устройство для контроля счетчиков | 1978 |

|

SU767971A1 |

Авторы

Даты

1980-03-25—Публикация

1978-03-17—Подача