1

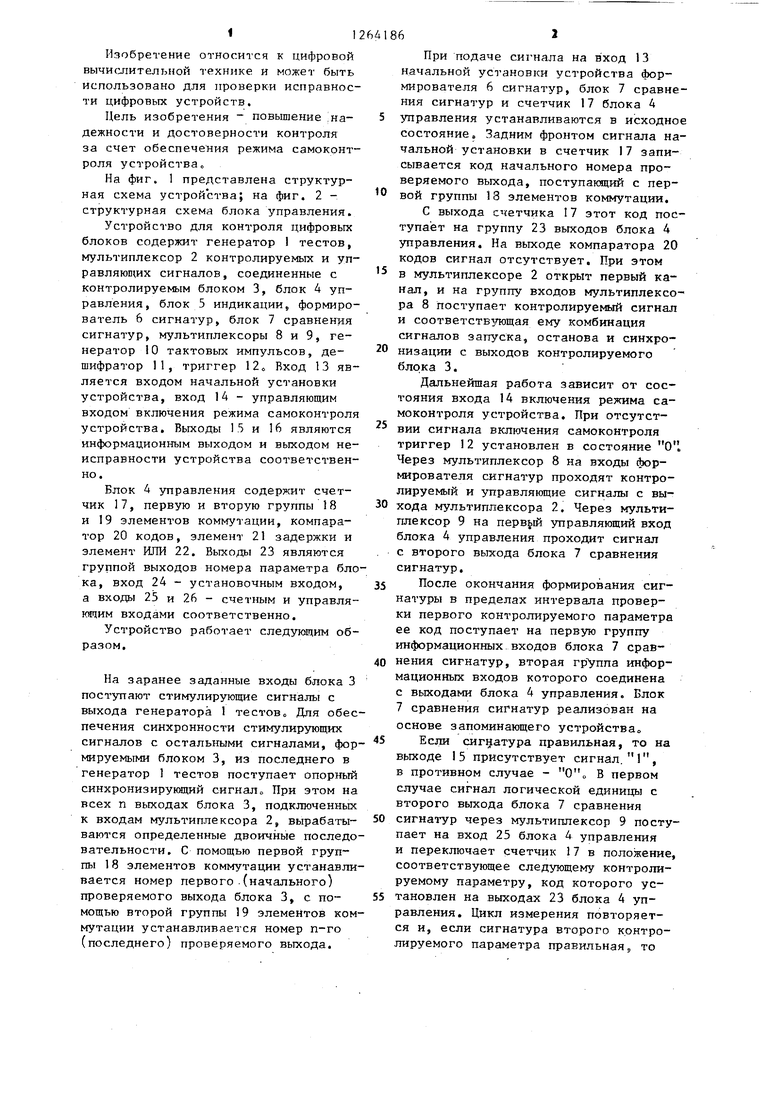

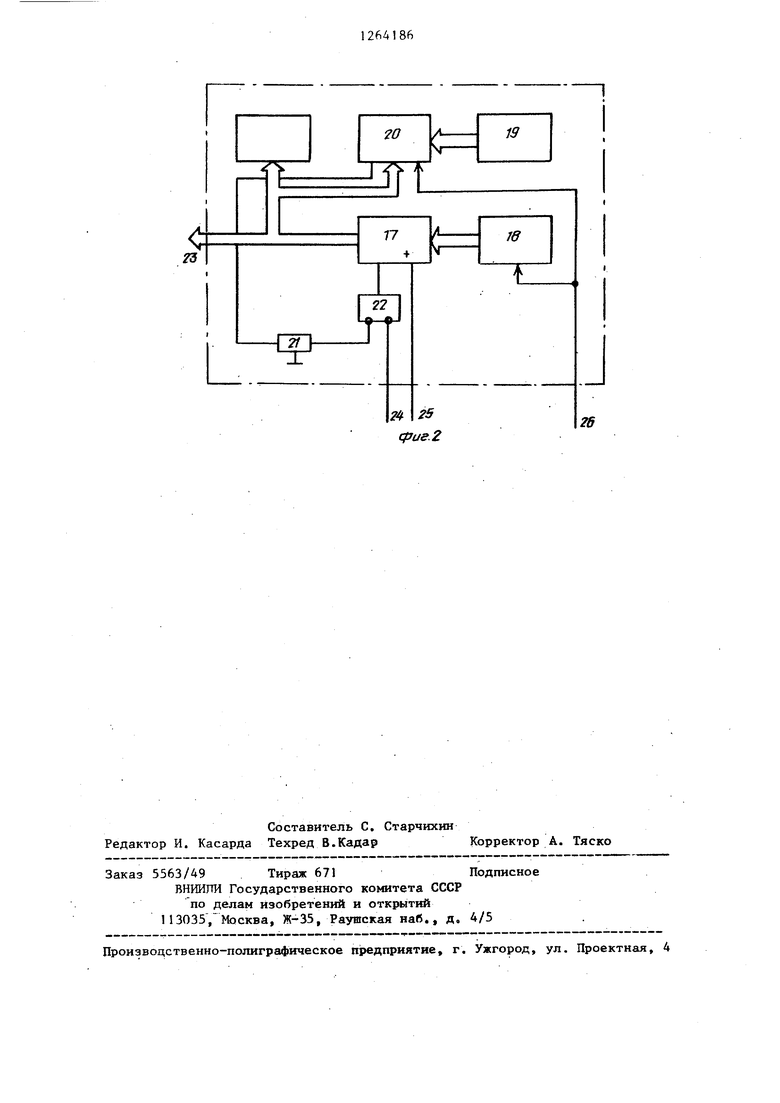

фие.1 Изобретение относится к цифровой вычислительной технике и может быть использовано для проверки исправности цифровых устройств. Цель изобретения повышение надежности и достоверности контроля за счет обеспечения режима самоконтроля устройства На фиг. 1 представлена структурная схема устройства; на фиг. 2 структурная схема блока управления. Устройство для контроля цифровых блоков содержит генератор 1 тестов, мультиплексор 2 контролируемых и управляющих сигналов, соединенные с контролируемым блоком 3, блок 4 управления, блок 5 индикации, формирователь 6 сигнатур, блок 7 сравнения сигнатур, мультиплексоры 8 и 9, генератор 10 тактовых импульсов, дешифратор 11, триггер 12о Вход 13 является входом начальной установки устройства, вход 1А - управляющим входом включения режима самоконтроля устройства. Выходы 15 и 16 являются информационным выходом и выходом неисправности устройства соответственно. Блок 4 управления содержит счетчик 17, первую и вторую группы 18 и 19 элементов коммутации, компаратор 20 кодов, элемент 21 задержки и элемент ИЛИ 22. Выходы 23 являются группой выходов номера параметра бло ка, вход 24 - установочным входом, а входы 25 и 26 - счетным и управля КШ1ИМ входами соответственно. Устройство работает следующим об разом. На заранее заданные входы блока 3 поступают стимулирующие сигналы с выхода генератора 1 тестов. Для обес печения синхронности стимулирующих сигналов с остальными сигналами, фор мируемыми блоком 3, из последнего в генератор 1 тестов поступает опорный синхронизирукщий сигнал При этом н всех п выходах блока 3, подключенных к входам мультиплексора 2, вырабатываются определенные двоичные последо вательности. С помощью первой группы 18 элементов коммутации устанавли вается номер первого.(начального) проверяемого выхода блока 3, с помощью второй группы 19 элементов ко мутации устанавливается номер п-го (последнего) проверяемого выхода. 62 При подаче сигнала на вход 13 начальной установки устройства формирователя 6 сигнатур, блок 7 сравнения сигнатур и счетчик 17 блока 4 управления устанавливаются в исходное состояние. Задним фронтом сигнала начальной установки в счетчик 17 записывается код начального номера проверяемого выхода, поступакяций с первой группы 18 элементов коммутации. С выхода счетчика I7 этот код поступает на группу 23 выходов блока 4 управления. На выходе компаратора 20 кодов сигнал отсутствует. При этом в мультиплексоре 2 открыт первый канал, и на группу входов мультиплексора 8 поступает контролируемый сигнал и соответствующая ему комбинация сигналов запуска, останова и синхронизации с выходов контролируемого блока 3. Дальнейшая работа зависит от состояния входа 14 включения самоконтроля устройства. При отсутствии сигнала включения самоконтроля триггер 12 установлен в состояние Ol Через мультиплексор 8 на входы формирователя сигнатур проходят контролируемый и управляющие сигналы с выхода мультиплексора 2. Через мультиплексор 9 на nepsjirfi управляющий вход блока 4 управления проходит сигнал с второго выхода блока 7 сравнения сигнатур, После окончания формирования сигнатуры в пределах интервала проверки первого контролируемого параметра ее код поступает на первую группу информационных входов блока 7 сравнения сигнатур, вторая группа информационных входов которого соединена с выходами блока 4 управления. Блок 7 сравнения сигнатур реализован на основе запоминающего устройства Если сигнатура правильная, то на выходе 15 присутствует сигнал., в противном случае - О В первом случае сигнал логической единицы с второго выхода блока 7 сравнения сигнатур через мультиплексор 9 поступает на вход 25 блока 4 управления и переключает счетчик 17 в положение, соответствующее следующему контролируемому параметру, код которого установлен на выходах 23 блока 4 управления. Цикл измерения повторяется и, если сигнатура второго контролируемого параметра правильная, то аналогичным образом устройство пере ходит к проверке следующего парамет ра и т.д. Если сигнатуры всех следующих па раметров правильные, то счетчик 17 блока 4 управления от начального со стояния последовательно проходит вс состояния до последнего п-го. После проверки сигнала на последнем (п-м) выходе блока 3, если сигнатура правильная, счетчик 17 переключается в ливается код, равный коду, установленному с помощью второй группы 19 элементов коммутации. При этом на выходе компаратора 20 кодов формируется сигнал, который через элемент 21 задержки и элемент ИЛИ 22 поступает на вход начальной установ ки счетчика 17, и цикл повторяется. Если же в процессе контроля сигн тура одного из параметров (i-ro) оказывается неправильной, то на выходе 15 устройства устанавливается запрещающий потенциал. При этом на выходе счетчика 17 остается код номера параметра, который классифицируется как неисправный. Этот код ин дицируется блоком 5 индикации и служит исходной информацией дпя ремонта блока 3. Если на вход 14 устройства поступает сигнал включения режима самоконтроля , то мультиплексоры 8 и 9 переключаются. С R-входа .триггера 12 снимается сигнал, удерживающий его в состоянии О. В блоке 4 управления сигналом с входа 26 отключаются .первая группа 18 элементов коммутации и компаратор 20 кодов, не оказывающие в этом режиме влияния на работу блока 4. В результате на вход 25 блока 4 управления проходят импульсы с. выхот да генератора 10 тактовых импульсов и счетчик 17 работает в режиме делителя, частоты, формируя на информационном выходе 23 напряжения формь. меандр с частотами, равными , , 1 где fr - частота импульсов генератора 10, 1 - разрядность счетчика 17, обусловленная количеством I контролируемых параметров . К второй группе входов мультиплексора 8 подключены выход генератора 10, используемый для синхронизации, и два или три выхода из группы выходов 23 блока управления, используемые в качестве контролируемого сигнала (например, с выхода первого разряда счетчика 17) и сигналов запуска и останова (например, с выхода 1-го разряда счетчика 17), Очевидно, что эти сигналы синхронны с сигналами генератора 10. Сигналы с второй группы входов мультиплексора 8 проходят на соответствующие входы формирователя 6 сигнатур. Обычным образом формируется сигнатура, которая с его выхода подается на блок 7 сравнения сигнатур и на дешифратор 11, Если сигнатура в режиме самоконтроля соответствует эталонной, на выходе ,15 устройства появляется 1 - сигнал, свидетельствующий о том, что формирователь 6 сигнатур, блок 7 сравнения сигнатур и блок 4 управления полностью рабо- оспособны. Если сигнал на выходе 15 устройства в режиме самоконтроля равен О, fo имеется возможность частичной локализации неисправности. Дешифратор 11 настроен на эталонную сигнатуру. В момент конца измерения он стробируется сигналом с выхода формирователя сигнатур и переключает в 1 триггер 12, выход которого 16 является выходом неисправности устройства Если сигнатура отличается от эталонной, то триггер 12 остается в состоянии О. Единичный сигнал на выходе 16 устройства свидетельствует о том, что Формирователь 6 сигнатур и блок 4 управления работоспособны и неисправность возможна только в блоке 7 сравнения сигнатур. Нулевой сигнал на выходе 16 устройства говорит о том, что неисправность следует искать в блоках 6, 4, Таким образом, за счет многофункционального использования блока 4 управления, формирователь 6 сигнатур и блока 7 сравнения сигнатур при минимальных дополнительных аппаратурных затратах (5%), без снижения быстродействия обеспечивается повышение надежности и достоверности контроля цифровых узлов за счет обеспечения режима самоконтроля и частичной локализации неисправности. Ускоряются также поиск и устранение неисправности.

51 2

Формула изобретения

Устройство для контроля цифровых блоков, содержащее генератор тестов, мультиплексор контролируемых и управляющих сигналов, формирователь сигнатур, блок сравнения сигнатур, блок управления и блок индикации, при этом группа выходов номера параметра блока управления соединена с группой управляющих входов мультиплексора контролируемых и управляющи сигналов, группой входов блока индикации и первой группой информационных входов блока сравнения сигнатур, вход начальной установки устройства соединен с установочными входами формирователя сигнатур, блока сравнения сигнатур и блока управления, группа информационных выходов и синхровход генератора тестов соединены соответственно с группой информационных входов и синхровыходом контролируемого цифрового блока, информационные выходы, выходы Пуск, Стоп и Синхро контролируемого цифрового блока соединены с соответствующими информационными входами мультиплексора контролируемых и управляющих сигналов, группа информационных выходов и выход стробирования формирователя сигнатур соединены соответственно с второй группой информационных входов и входом стробирования блока сравнения сигнатур, информационный выход которого является информационным выходом устройства, отличающееся тем, что, с целью повыщения достоверности коктро86«

ля за счет обеспечения режима самоконтроля устройства, оно содержит два мультиплексора, генератор тактовых импульсов, дешифратор и триггер, выход которого является выходом неисправности устройства, причем первая группа информационных входов первого мультиплексора подключена к группе выходов мультиплексора контролируемь1х и управляющих сигналов, вторая группа информационных входов первого мультиплексора подключена к группе выходов номера контролируемого параметра блока управления и к выходу генератора тактовых импульсов выходы первого мультиплексора подключены к информационному входу, входам Пуск, Стоп и Синхро формирователя сигнатур, первый и второй информационные входы второго мультиплексора подключены соответственно к синхровыходу блока сравнения сигнатур и к выходу генератора тактовых импульсов, выход второго мультиплексора соединен со счетным входом блока управления, информацион- ные входы и вход стробирования дешифратора соединены соответственно, с информационными выходами и выходом стробирования формирователя сигнатур, выход дешифратора соединен с S-входом триггера, управляющие входы первого и второго мультиплексоров, вход разрешения блока сравнения сигнатур, управляющий вход блока управления и R-вход триггера объединены и являются входом включения режима самоконтроля устройства .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

Изобретение относится к цифровой вычислительной технике и может /77 быть использовано для проверки исправности цифровых устройств. Целью изобретения является повышение надежности и достоверности контроля за счет обеспечения режима самоконтроля устройства. Устройство содержит генератор 1 тестов, мультиплексор 2 конт ролируемых и управляклцих сигналов с контролируеИ)1м блоком 3, блок 4 управления, блок 5 индикации, формирователь 6 сигнатур, блок 7 сравнения сигнатур. Два мультиплексора 9 и 8, генератор 10 тактовых импульсов, дешифратор 11 и триггер 12. 2 ил. (Л

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1984-07-25—Подача