(54) ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-аналоговый преобразователь | 1982 |

|

SU1018226A1 |

| Устройство для компенсации различий в чувствительности элементов матрицы фотоприемников | 1987 |

|

SU1571793A1 |

| МОЩНЫЙ ИСТОЧНИК ПИТАНИЯ ПОСТОЯННОГО ТОКА | 2000 |

|

RU2172058C1 |

| Преобразователь постоянного напряжения в переменное напряжение заданной формы | 1986 |

|

SU1379925A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ МНОГОЭЛЕМЕНТНОГО ПРИЕМНИКА | 1992 |

|

RU2025905C1 |

| УСТРОЙСТВО для МОДЕЛИРОВАНИЯ УСИЛИЙ в ТРАНСПОРТНЫХ СООРУЖЕНИЯХ | 1972 |

|

SU331408A1 |

| Инвертор со ступенчатым квазисинусоидальным выходным напряжением | 1982 |

|

SU1035758A1 |

| Калибратор переменного напряжения | 1983 |

|

SU1115031A1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

Изобретение относится к области вычислительной техники и, в частности, к преобразователям формы представления информации и может быть использовано для вывода аналоговой информации, представленной напряжением или током, из цифровой вычислительной машины, а также для создания сигнала обратной связи в преобразователях напряжений в код. Известно устройство, содержащее, токозадаюшуго цепь, суммирующую цепь, чувствительный элемент, коммутаторы и схему управления, кроме того, содержащее в каждом разряде токорегулируемый элемент, запоминающую ячейку и ключ, причем выходы токозадающей цепи подключень к входам соответствующих токорегулирующих элементов, выход каждого токорегулирующего элемента подключен ко входу соответствующего ключа, выходы ключей подключены к входам суммирующей цепи, щина опорного напряжения соединена с вторым входом чувствительного элемента, выход чувствительного элемента подключен к входу второго коммутатора, а выходы данного коммутатора подключены к входам соответствующих запоминающих ячеек, выходы которых соединены с управляющими входами токорегулирующих элементов, выходы схемы управления подключены к управляющим входам коммутаторов, управляющие входы ключей являются кодовыми входами преобразователя, а выход суммирующей цепи является выходом преобразователя 1 . Однако быстродействие известного технического рещения ограничено, так как в нем нельзя проводить коррекцию погрещности преобразования без прерывания режима преобразования входного кода. Цель изобретения - повыщение бь1стродействия устройства. Поставленная цель достигается тем, что в цифроаналоговом преобразователе, содержащем токозадающую цепь, суммирующую цепь, чувствительный элемент, два коммутатора и схему управления, кроме того,содержащем в каждом разряде токорегулирующий элемент, запоминующую ячейку и ключ, причем выходы токозадающей цепи подключены к входам соответствующих токорегулирующих элементов, выход каждого токорегулирующего элемента подключен к входу соответствующего ключа, выходы ключей подключены к входам суммирующей цепи, шина опорного напряжения соединена с вторым входом чувствительного элемента, ВЪ1ХОД чувствительного элемента подключен к входу второго коммутатора, а выходы данного коммутатора подключены к входам соответствующих запоминающих ячеек, вйходъг которых соединены с управляющими входами токорегулирующих элементов, выходы схемы управления подключены к управляющим входам коммутаторов, управляющие входы ключей являются кодовыми входами преобразователя, а выход суммирующей цепи является выходом преобразователя, входы первого коммутатора подключены к выходам токозадающей цепи, а выход первого коммутатора подключен к первому входу чувствительного элемента.

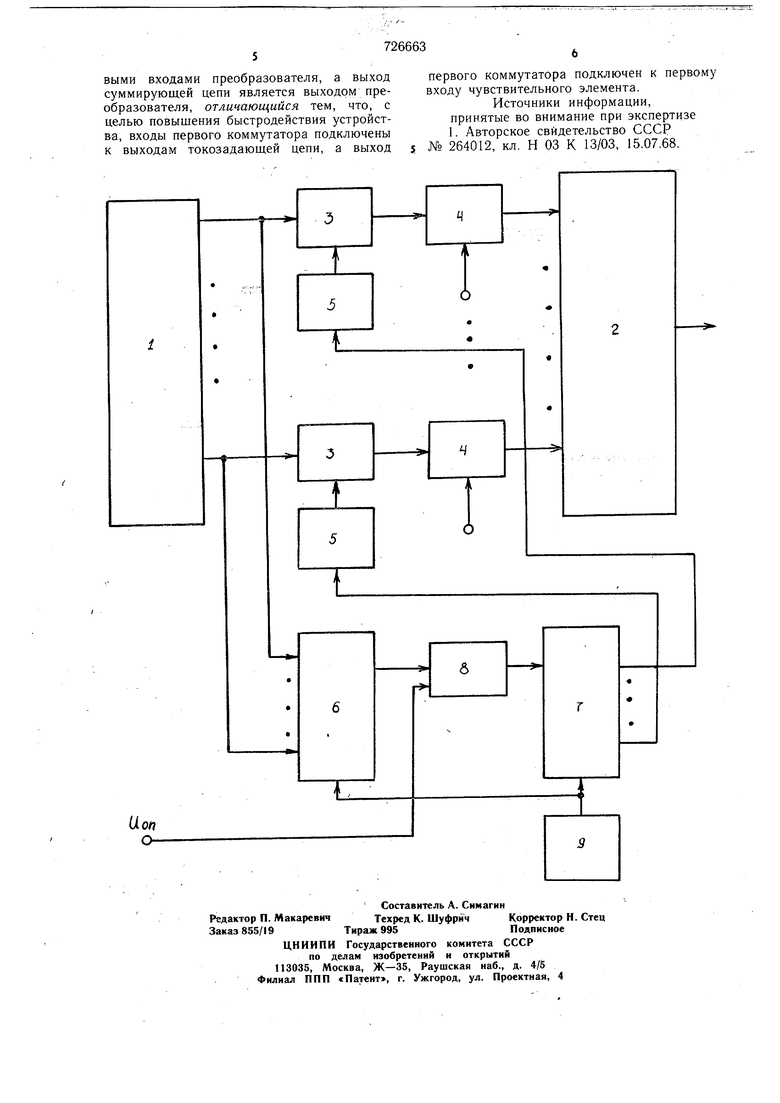

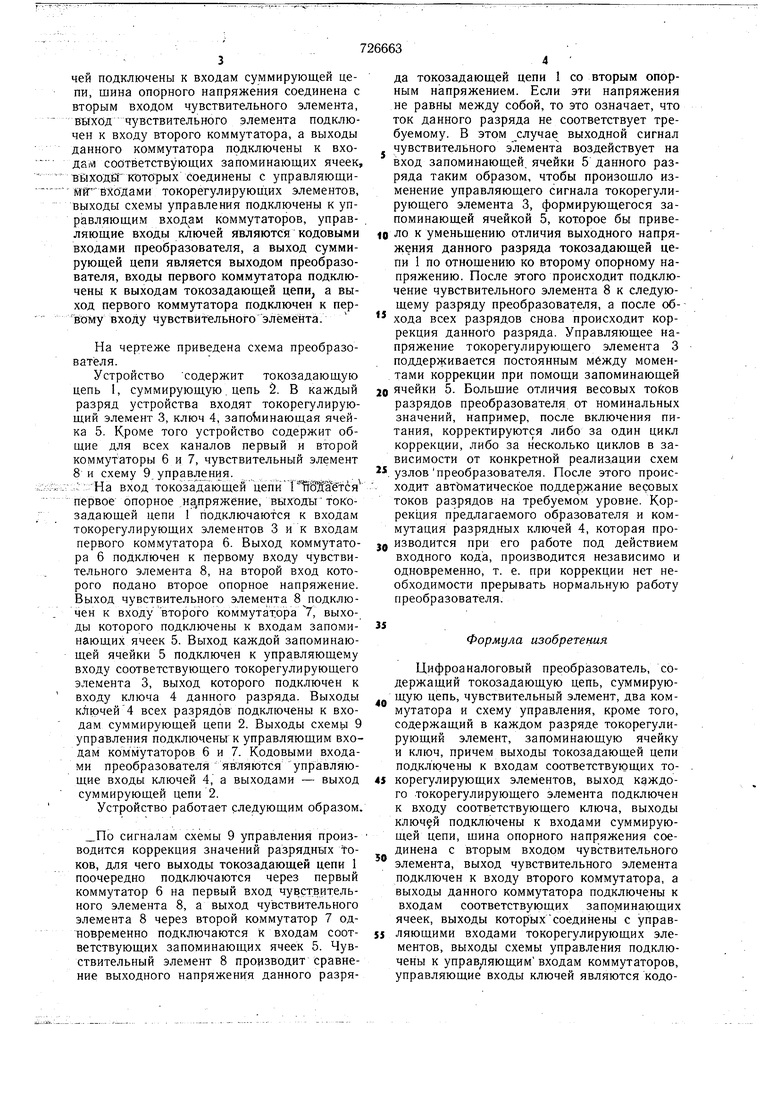

На чертеже приведена схема преобразователя.

Устройство содержит токозадающую цепь I, суммирующую цепь И. В каждый разряд устройства входят токорегулирующий элемент 3, ключ 4, запоминающая ячейка 5. Кроме того устройство содержит общие для всех каналов первый и второй коммутаторы 6 и 7, чувствительный элемент 8 и схему 9 управления. .. вход токозадающей цепи Р З Щется первое опорное на,пряжение, выходы токозадающей цепи 1 подключаются к входам токорегулирующих элементов 3 и к входам первого коммутатора 6. Выход коммутатора 6 подключен к первому входу чувствительного элемента 8, на второй вход которого подано второе опорное напряжение. Выход чувствительного элемента В подключен к входу второго коммутатора 7, выходы которого подключены к входам запоминающих ячеек 5. Выход каждой запоминающей ячейки 5 подключен к управляющему входу соответствующего токорегулирующего элемента 3, выход которого подключен к входу ключа 4 данного разряда. Выходы ключей Ч всех разрядов подключены к входам суммирующей цепи 2. Выходы схемь 9 управления подключены к управляющим входам коммутаторов 6 и 7. Кодовыми входами преобразователя являются управляющие входы ключей 4, а выходами - выход суммирующей цепи 2.

Устройство работает следующим образом.

По сигналам схемы 9 управления производится коррекция значений разрядных toков, для чего выходы токозадающей цепи 1 поочередно подключаются через первый коммутатор 6 на первый вход чувствительного элемента 8, а выход чувствительного элемента 8 через второй коммутатор 7 одновременно подключаются к входам соответствующих запоминающих ячеек 5. Чувствительный элемент 8 производит сравнение выходного напряжения данного разряда токозадающей цепи 1 со вторым опорным напряжением. Если эти напряжения не равны между собой, то это означает, что ток данного разряда не соответствует требуемому. В этом случае выходной сигнал чувствительного элемента воздействует на вход запоминающей, ячейки 5 данного разряда таким образом, чтобы произошло изменение управляющего сигнала токорегулирующего элемента 3, формирующегося запоминающей ячейкой 5, которое бы привео ло к уменьщению отличия выходного напряжения данного разряда токозадающей цепи 1 по отнощению ко второму опорному напряжению. После этого происходит подключение чувствительного элемента 8 к следующему разряду преобразователя, а после обхода всех разрядов снова происходит коррекция данного разряда. Управляющее напряжение токорегулирующего элемента 3 поддерживается постоянным между моментами коррекции при помощи запоминающей J) ячейки 5. Больщие отличия весовых то(ов разрядов преобразователя от номинальных значений, например, после включения питания, корректируются либо за один цикл коррекции, либо за несколько циклов в зависимости от конкретной реализации схем узловпреобразователя. После этого происходит автЪматическое поддержание весовых токов разрядов на требуемом уровне. Коррекция предлагаемого образователя и коммутация разрядных ключей 4, которая производится при его работе под действием входного кода, производится независимо и одновременно, т. е. при коррекции нет необходимости прерывать нормальную работу преобразователя.

Формула изобретения

Цифроаналоговый преобразователь, содержащий токозадающую цепь, суммирующую цепь, чувствительный элемент, два коммутатора и схему управления, кроме того, содержащий в каждом разряде токорегулирующий элемент, запоминающую ячейку и ключ, причем выходы токозадающей цепи подключены к входам соответствующих токорегулирующих элементов, выход каждого токорегулирующего элемента подключен к входу соответствующего ключа, выходы ключей подключены к входами суммирующей цепи, щина опорного напряжения соединена с вторым входом чувствительного элемента, выход чувствительного элемента подключен к входу второго коммутатора, а выходы данного коммутатора подключены к входам соответствующих запоминающих ячеек, выходы которых соединены с управляющими входами токорегулирующих элементов, выходы схемы управления подключены к управляющим входам коммутаторов, управляющие входы ключей являются кодо

Авторы

Даты

1980-04-05—Публикация

1977-12-12—Подача