i (Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода Фибоначчи в двоичный код | 1986 |

|

SU1432789A1 |

| Преобразователь кодов | 1987 |

|

SU1450112A1 |

| Устройство для классификации нестационарных случайных процессов | 1987 |

|

SU1462358A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

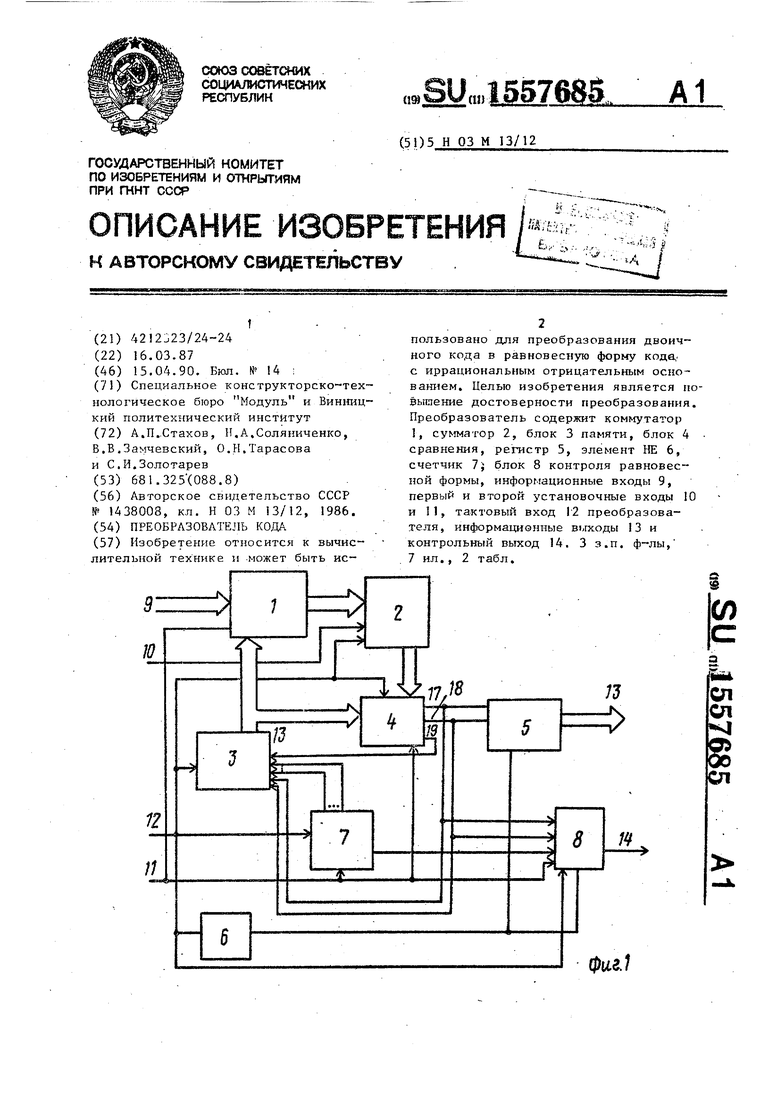

Изобретение относится к вычислительной технике и может быть использовано для преобразования двоичного кода в равновесную форму кода с иррациональным отрицательным основанием. Целью изобретения является повышение достоверности преобразования. Преобразователь содержит коммутатор 1, сумматор 2, блок 3 памяти, блок 4 сравнения, регистр 5, элемент НЕ 6, счетчик 7, блок 8 контроля равновесной формы, информационные входы 9, первый и второй установочные входы 10 и 11, тактовый вход 12 преобразователя, информационные выходы 13 и контрольный выход 14. 3 з.п. ф-лы, 7 ил., 2 табл.

СП СП ч|

Изобретение относится к вычислительной технике и может быть использовано для преобразования двоичного кода в равновесную форму кода с ирра- цнопальным отрицательным основанием.

Целью изобретения является повышение достоверности преобразования.

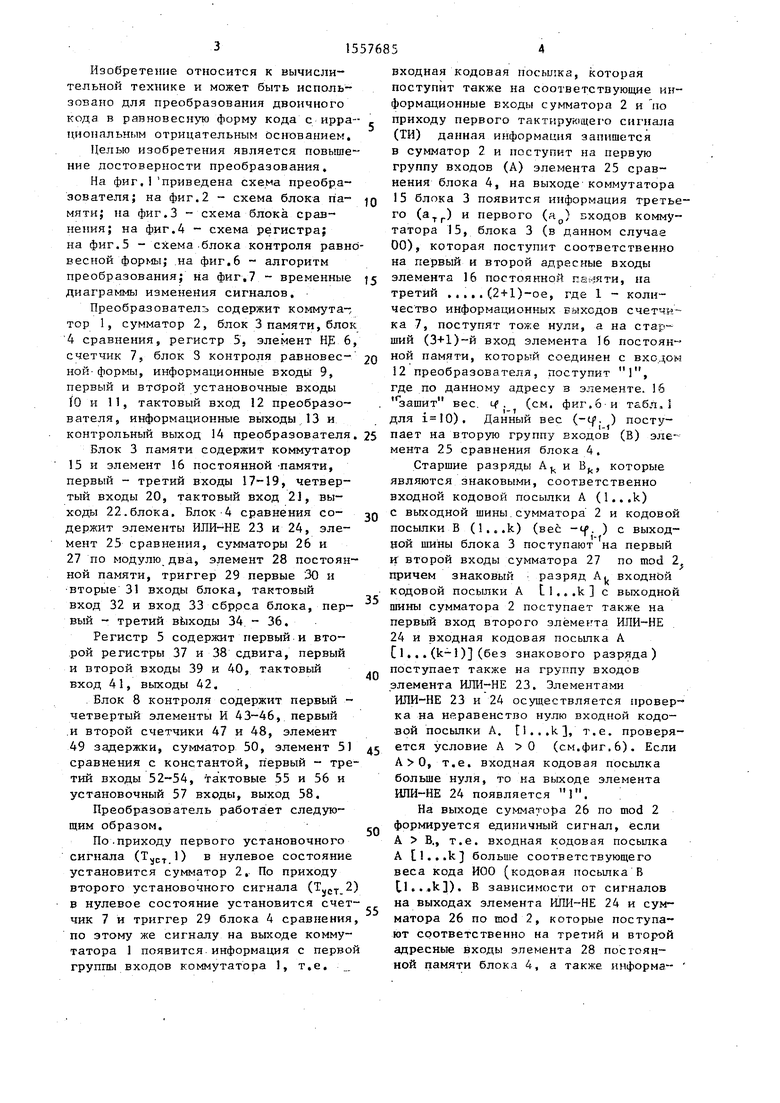

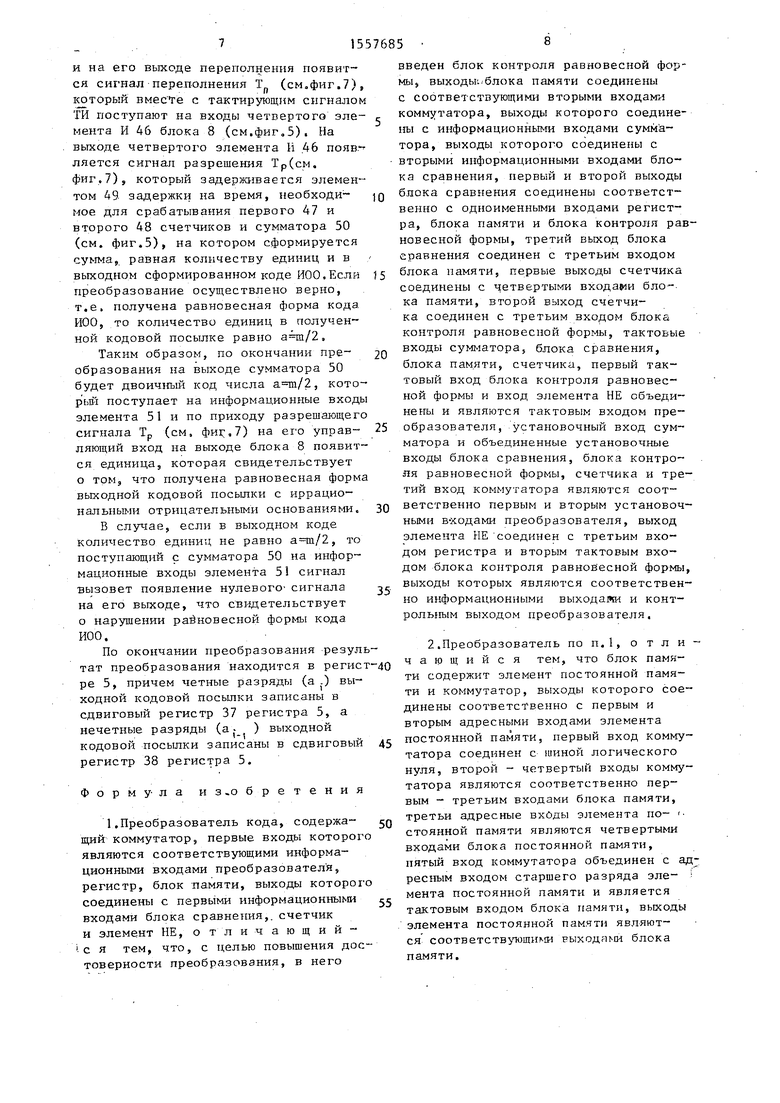

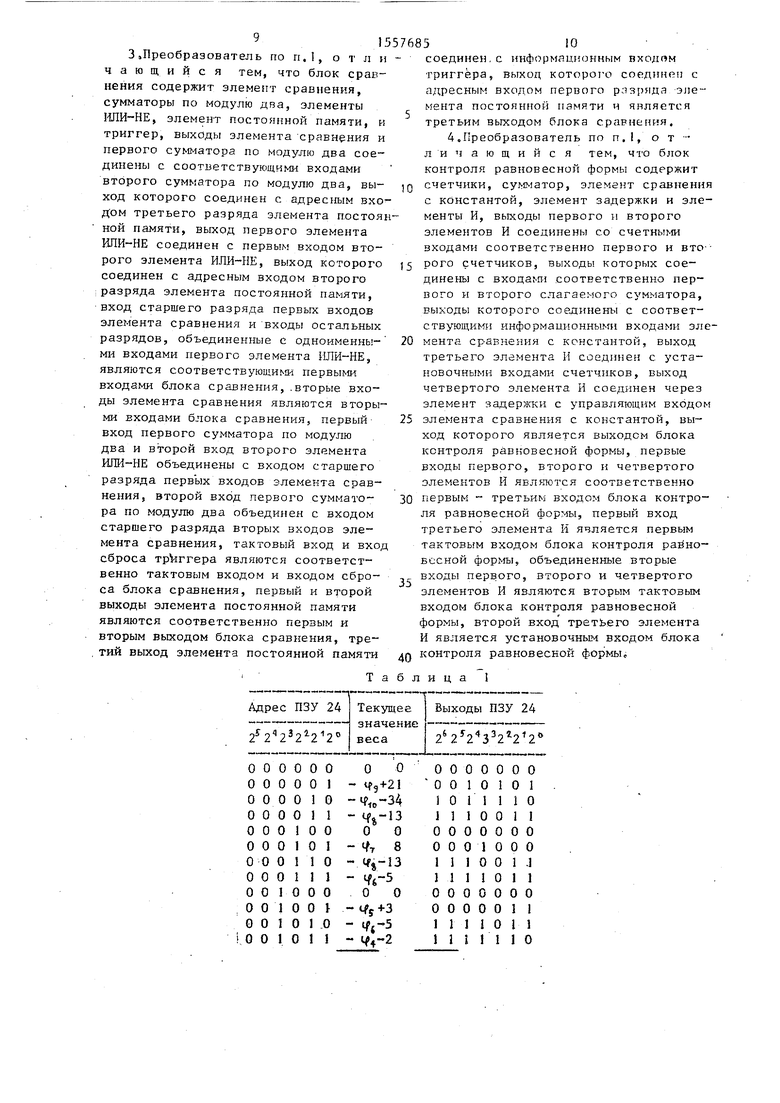

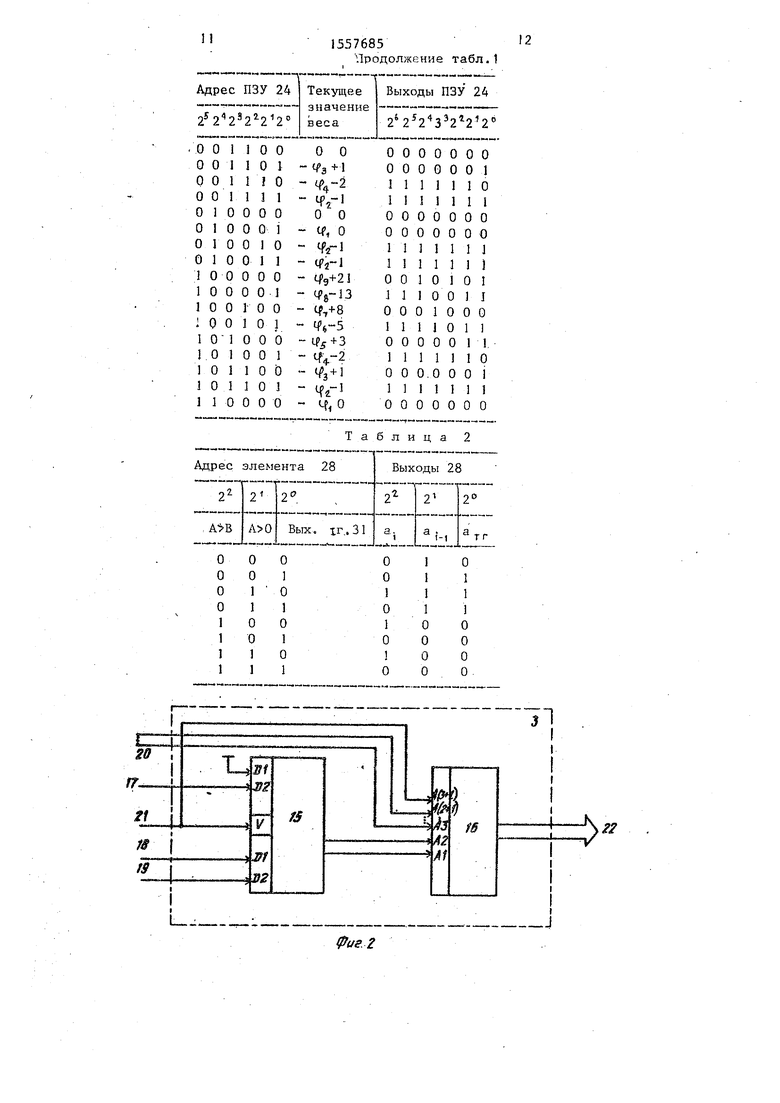

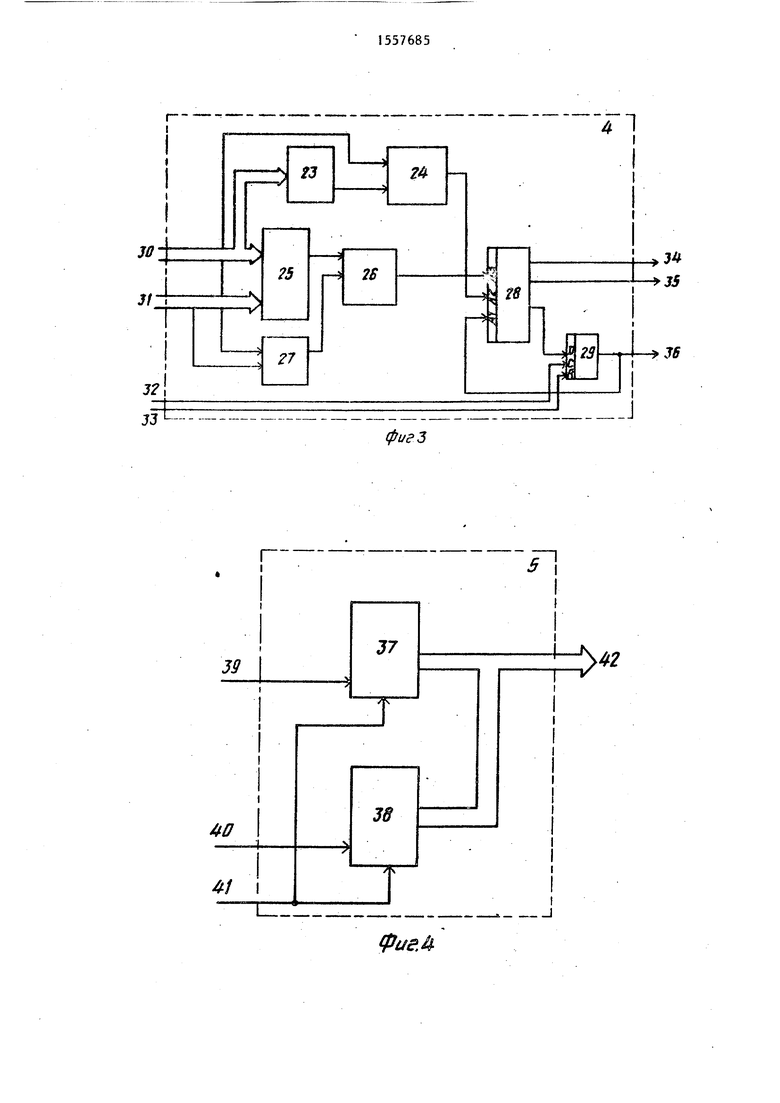

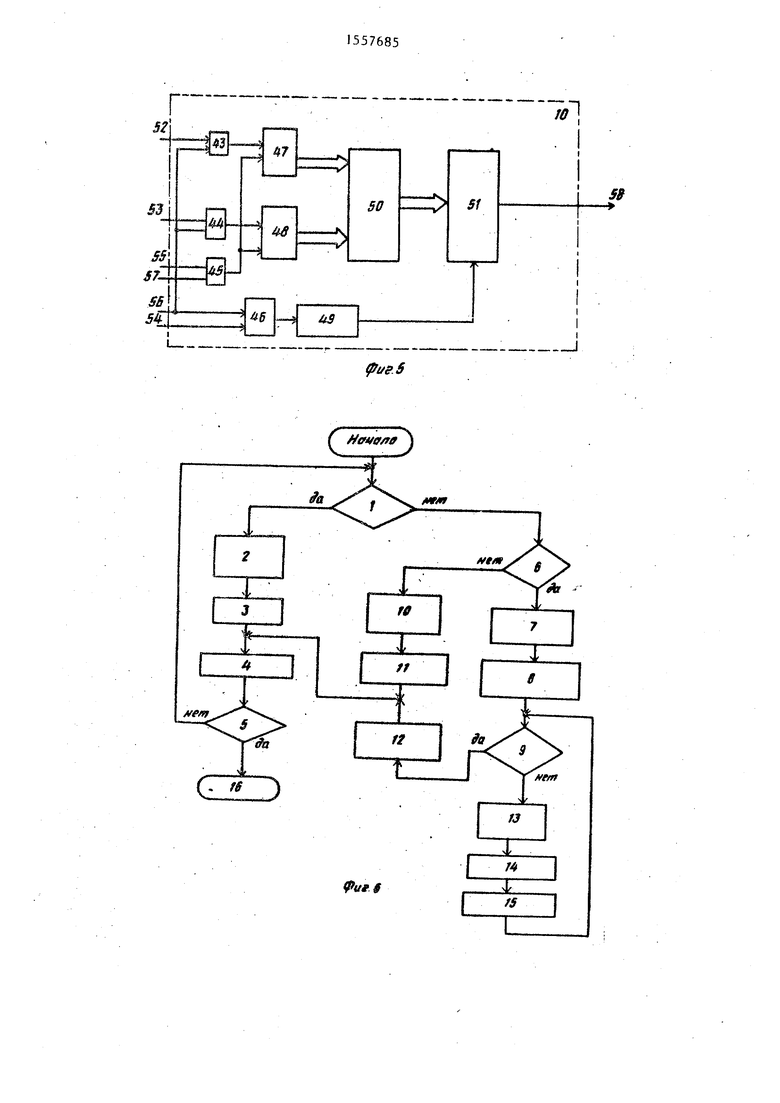

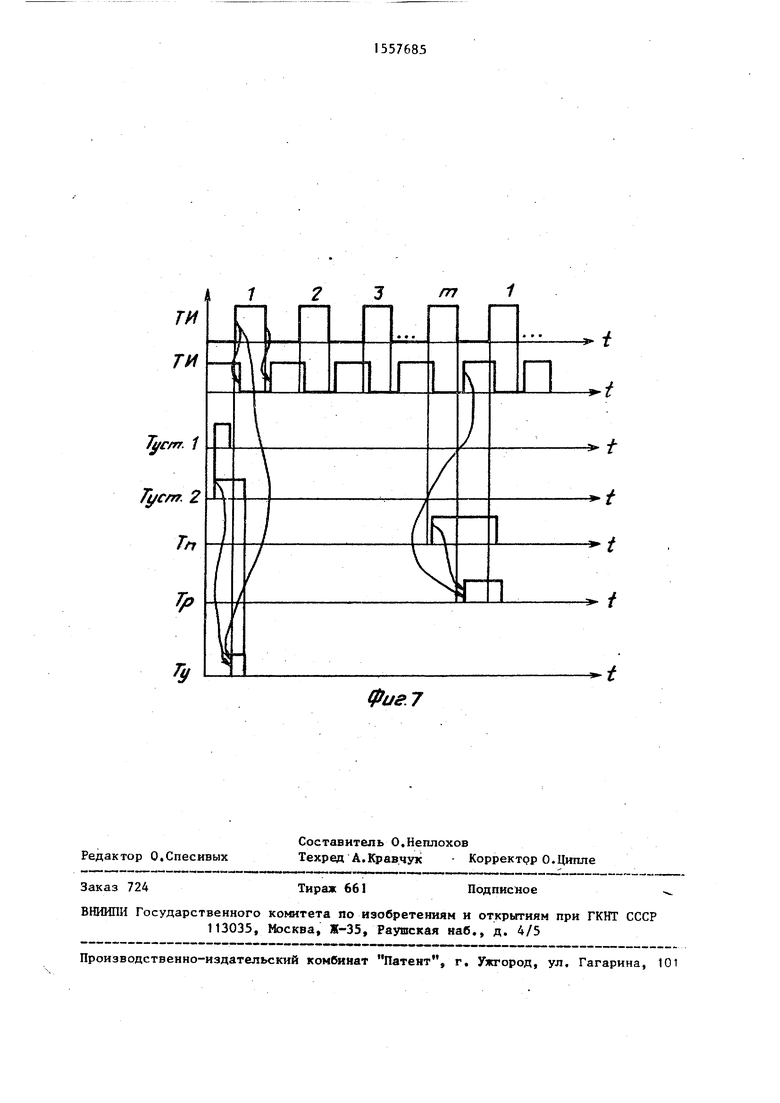

На фиг.1 приведена схема преобразователя; на фиг.2 - схема блока па- мяти; на фиг.З - схема блока сравнения; на фиг.4 - схема регистра; на фиг.5 - схема блока контроля равновесной формы; на фиг.6 - алгоритм преобразования; на фиг.7 - временные диаграммы изменения сигналов,

Преобразователе содержит коммута-, тор 1, сумматор 2, блок 3 памяти, блок 4 сравнения, регистр 5, элемент НЕ 6, счетчик 7, блок 3 контроля равновес- ной формы, информационные входы 9, первый и второй установочные входы fO и 11, тактовый вход 12 преобразователя, информационные выходы 13 и контрольный выход 14 преобразователя.

Блок 3 памяти содержит коммутатор 15 и элемент 16 постоянной памяти, первый - третий входы 17-19, четвертый входы 20, тактовый вход 21, выходы 22.блока. Блок 4 сравнения со- держит элементы ИЛИ-НЕ 23 и 24, элемент 25 сравнения, сумматоры 26 и 27 по модулю два, элемент 28 постоянной памяти, триггер 29 первые 30 и вторые 31 входы блока, тактовый вход 32 и вход 33 сбррса блока, первый - третий выходы 34 - 36.

Регистр 5 содержит первый и второй регистры 37 и 38 сдвига, первый и второй входы 39 и 40, тактовый

вход 41, выходы 42.

Блок 8 контроля содержит первый - четвертый элементы И 43-46, первый и второй счетчики 47 и 48, элемент 49 задержки, сумматор 50, элемент 51 сравнения с константой, первый - третий входы 52-54, тактовые 55 и 56 и установочный 57 входы, выход 58.

Преобразователь работает следующим образом.

По.приходу первого установочного сигнала (Тзст 1) в нулевое состояние установится сумматор 2, По приходу второго установочного сигнала (Т;() в нулевое состояние установится счет- чик 7 и триггер 29 блока 4 сравнения, по этому же сигналу на выходе коммутатора 1 появится информация с первой группы входов коммутатора 1, т.е.

g 5

0 5

о

.

5

Q

5

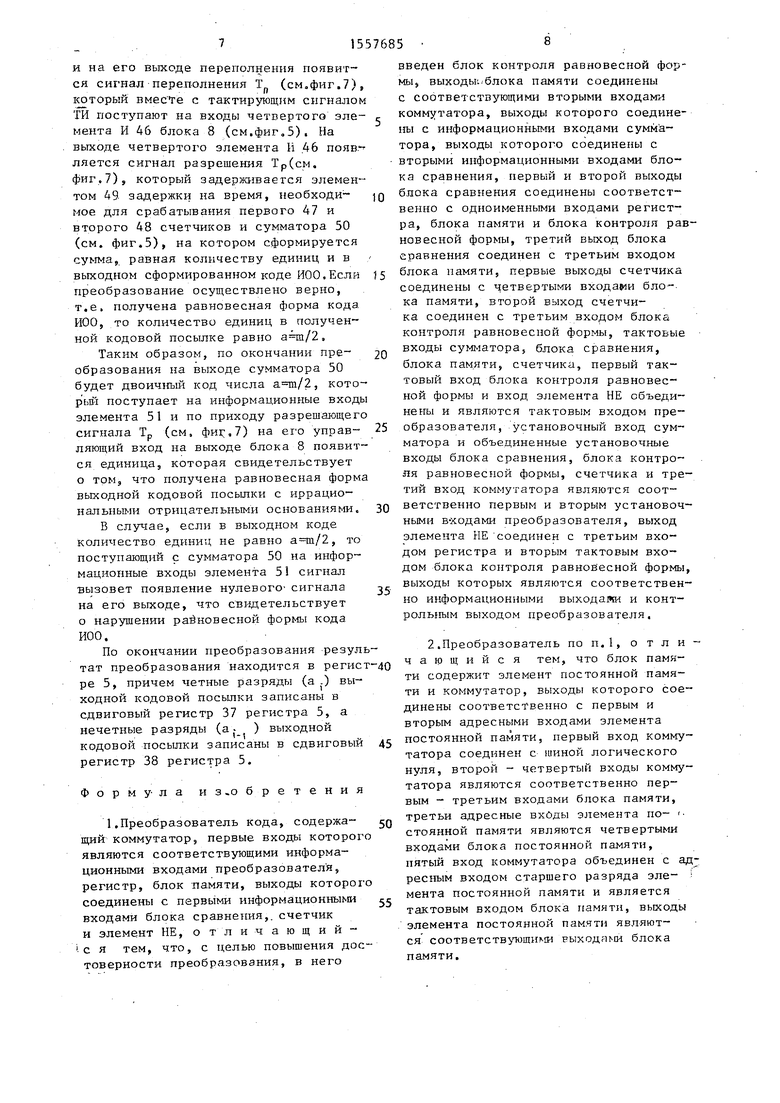

входная кодовая посылка, которая поступит также на соответствующие информационные входы сумматора 2 и по приходу первого тактирующего сигнала (Тй) данная информация запишется в сумматор 2 и поступит на первую группу входов (А) элемента 25 сравнения блока 4, на выходе коммутатора 15 блока 3 появится информация третьего (атг) и первого (ftQ) входов коммутатора 15, блока 3 (в данном случаг 00), которая поступит соответственно на первый и второй адресные входы элемента 16 постоянной пьзяти, на третий .. .. . (2 + 1)-ое, где 1 - количество информационных выходов счетчика 7, поступят тоже нули, а на старший (3+1)-й вход элемента 16 постоянной памяти, который соединен с входом 12 преобразователя, поступит 1, где по данному адресу з элементе. 16 зашит вес ц . (см. фиг.6 и табл. 1 для ). Данный вес (-if. ) поступает на вторую группу входов (В) элемента 25 сравнения блока 4.

Старшие разряды Ak и Bk, которые являются знаковыми, соответственно входной кодовой посылки A (l...k) с выходной шины сумматора 2 и кодовой посылки В (l...k) (вес -if. ) с выходной шины блока 3 поступают на первый и второй входы сумматора 27 по mod 2f причем знаковый разряд А входной кодовой посылки А I1..,k с выходной шины сумматора 2 поступает также на первый вход второго элемента ИПИ-НЕ 24 и входная кодовая посылка А 1...(k-1)(без знакового разряда) поступает также на группу входов элемента ИЛИ-НЕ 23. Элементами ИЛИ-НЕ 23 и 24 осуществляется проверка на неравенство нулю входной кодовой посылки А, П...К,, т.е. проверяется условие А 0 (см.фиг.6). Если , т.е. входная кодовая посыпка больше нуля, то на выходе элемента ИЛИ-НЕ 24 появляется 1.

На выходе сумматора 26 по mod 2 формируется единичный сигнал, если А В., т.е. входная кодовая посылка A l...k больше соответствующего веса кода ИОО (кодовая посылка В ). В зависимости от сигналов на выходах элемента ИЛИ-НЕ 24 и сумматора 26 по mod 2, которые поступают соответственно на третий и второй адресные входы элемента 28 постоянной памяти блока 4, а также информа-

ции на выходе триггера 29 блока 4, которая поступает на первый адресный вход элемента 28 постоянной памяти блока 4, на выходе элемента 28 формируется трехразрядный код, соответствующий двум разрядам выходного кода aj и а ;., сигнал атп, устанавливающий триггер 29 в нулевое или единичное состояние в зависимости от того, в какой ветви алгоритма находится преобразователь на данном шаге преобразования (см. фиг.6 и табл.2 принятых решений),

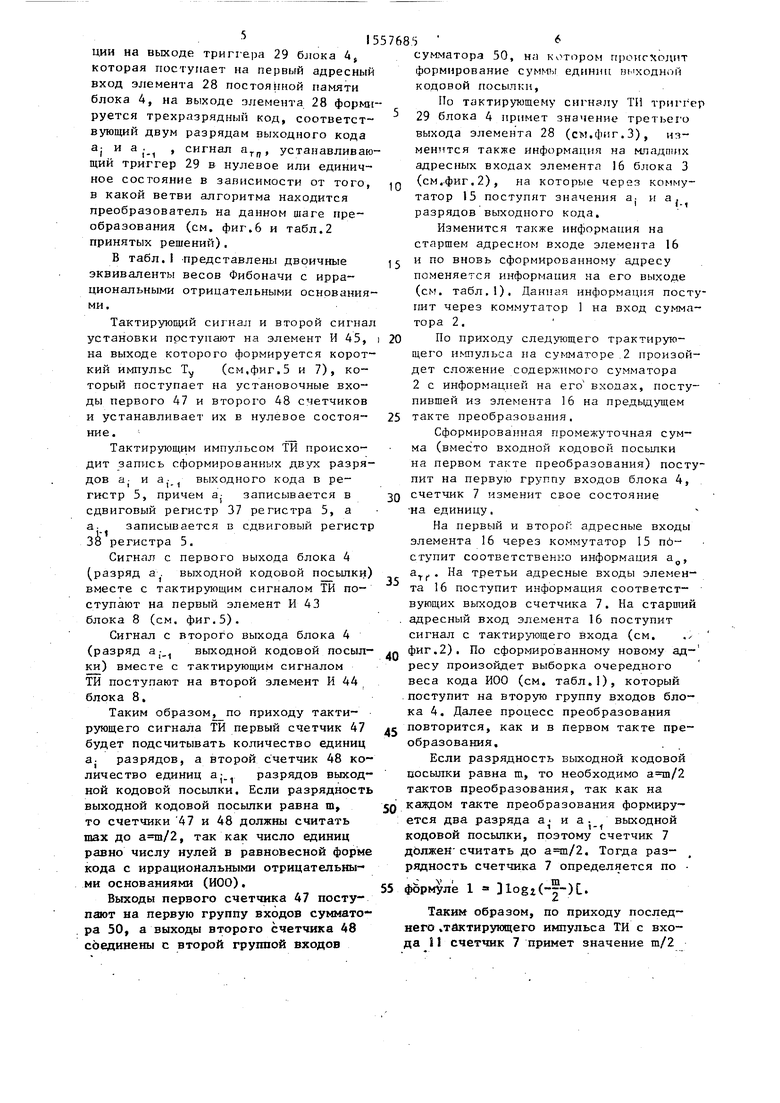

В табл.I представлены двоичные эквиваленты весов Фибоначи с иррациональными отрицательными основаниями.

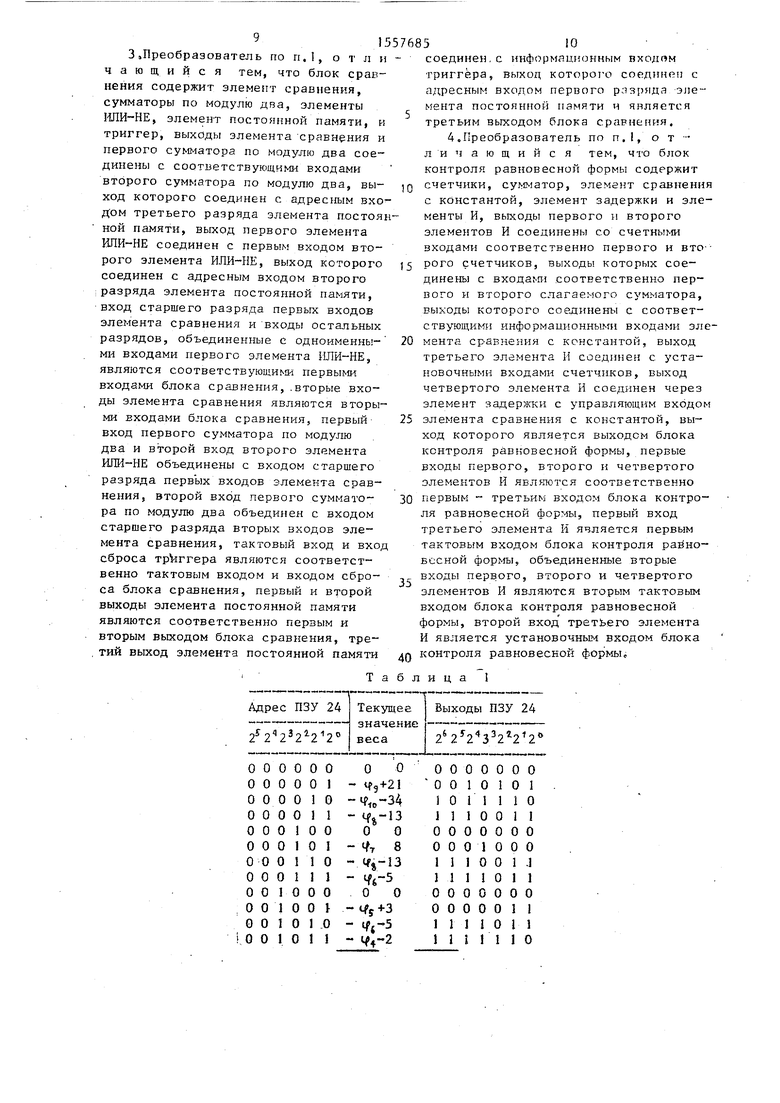

Тактирующий сигнал и второй сигнал установки поступают на элемент И 45, на выходе которого формируется короткий импульс TV (см,фиг.5 и 7), который поступает на установочные входы первого 47 и второго 48 счетчиков и устанавливает их в нулевое состояние.

Тактирующим импульсом ТИ происходит запись сформированных двух разрядов at и выходного кода в регистр 5, причем at записывается в сдвиговый регистр 37 регистра 5, а а записывается в сдвиговый регистр 38 регистра 5.

Сигнал с первого выхода блока 4 (разряд а выходной кодовой посылки) вместе с тактирующим сигналом ТИ поступают на первый элемент И 43 блока 8 (см. фиг.5).

Сигнал с второго выхода блока 4 (разряд а) выходной кодовой посылки) вместе с тактирующим сигналом ТИ поступают на второй элемент И 44 блока 8.

Таким образом, по приходу тактирующего сигнала ТИ первый счетчик 47 будет подсчитывать количество единиц а. разрядов, а второй счетчик 48 количество единиц а,-. 1 разрядов выходной кодовой посылки. Если разрядность выходной кодовой посылки равна т, то счетчики 47 и 48 должны считать шах до , так как число единиц равно числу нулей в равновесной форме кода с иррациональными отрицательными основаниями (ИОО).

Выходы первого счетчика 47 поступают на первую группу входов сумматора 50, а выходы второго счетчика 48 сЬединены с второй группой входов

0

5

0

5

0

5

0

5

сумматора 50, на котором происходит формирование суммы единиц впходнчй кодовой посылки,

Но тактирующему сигналу ТИ триггер 29 блока 4 примет значение третьего выхода элемента 28 (см.фиг.3), изменится также информация на младших адресных входах элемента 16 блока 3 (см.фиг.2), на которые через коммутатор 15 поступят значения 3j и а разрядов выходного кода.

Изменится также информация на старшем адресном входе элемента 16 и по вновь сформированному адресу поменяется информация на его выходе (см. табл.1). Данная информация поступит через коммутатор 1 на вход сумматора 2.

По приходу следующего трактирую- щего импульса на сумматоре 2 произойдет сложение содержимого сумматора 2 с информацией на его входах, поступившей из элемента 16 на предыдущем такте преобразования.

Сформированная промежуточная сумма (вместо входной кодовой посылки на первом такте преобразования) поступит на первую группу входов блока 4, счетчик 7 изменит свое состояние на единицу,

На первый и второГ адресные входы элемента 16 через коммутатор 15 пб ступит соответственно информация а0, aTf, . На третьи адресные входы элемента 16 поступит информация соответствующих выходов счетчика 7. На старший адресный вход элемента 16 поступит сигнал с тактирующего входа (см. фиг.2). По сформированному новому ад- ресу произойдет выборка очередного веса кода ИОО (см. табл.), который поступит на вторую группу входов блока 4. Далее процесс преобразования повторится, как и в первом такте преобразования.

Если разрядность выходной кодовой иосылки равна т, то необходимо тактов преобразования, так как на Q каждом такте преобразования формируется два разряда а и а . выходной кодовой посыпки, поэтому счетчик 7 должей считать до . Тогда раз- , рядность счетчика 7 определяется по

формуле 1 logz()C.

Таким образом, по приходу последнего .тактирующего импульса ТИ с входа I1 счетчик 7 примет значение т/2

и на его выходе переполнения появится сигнал переполнения Т (см„фиг.7), который вместе с тактирующим сигналом ТИ поступают на входы четвертого элемента И 46 блока 8 (см.фиг.5). На выходе четвертого элемента И 46 появляется сигнал разрешения Тр(см, фиг,7)s который задерживается элементом 49 задержки на время, необходи- мое для срабатывания первого 47 и второго 48 счетчиков и сумматора 50 (см. фиг.5), на котором сформируется сумма, равная количеству единиц и в выходном сформированном коде ИОО,Если преобразование осуществлено верно, т.е. получена равновесная форма кода ИОО, то количество единиц в полученной кодовой посылке равно ,

Таким образом, по окончании пре образования на выходе сумматора 50 будет двоичный код числа , который поступает на информационные входы элемента 51 и по приходу разрешающего сигнала Тр (см, фиг, ,7) на его управ- ляющий вход на выходе блока 8 появится единица, которая свидетельствует о том, что получена равновесная форма выходной кодовой посылки с иррациональными отрицательными основаниями.

В случае, если в выходном коде количество единиц не равно , то поступающий с сумматора 50 на информационные входы элемента 51 сигнал вызовет появление нулевого сигнала на его выходе, что свидетельствует о нарушении равновесной формы кода ИОО.

По окончании преобразования результат преобразования находится в регист ре 5, причем четные разряды (а.) выходной кодовой посылки записаны в сдвиговый регистр 37 регистра 5, а нечетные разряды (а (- ) выходной кодовой посылки записаны в сдвиговый регистр 38 регистра 5.

Формула из.обретения

введен блок контроля равновесной формы, выходы , блока памяти соединены с соответствующими вторыми входами коммутатора, выходы которого соединены с информационными входами сумматора, выходы которого соединены с вторыми информационными входами блока сравнения, первый и второй выходы блока сравнения соединены соответственно с одноименными входами регистра, блока памяти и блока контроля равновесной формы, третий выход блока сравнения соединен с третьим входом блока памяти, первые выходы счетчика соединены с четвертыми входами блока памяти, второй выход счетчика соединен с третьим входом блока контроля равновесной формы, тактовые входы сумматора, блока сравнения, блока памяти, счетчика, первый тактовый вход блока контроля равновесной формы и вход элемента НЕ объединены и являются тактовым входом преобразователя, установочный вход сумматора и объединенные установочные входы блока сравнения, блока контроля равновесной формы, счетчика и третий вход коммутатора являются соответственно первым и вторым установочными в-ходами преобразователя, выход элемента НЕ соединен с третьим входом регистра и вторым тактовым входом блока контроля равновесной формы, выходы которых являются соответственно информационными выходами и контрольным выходом преобразователя.

10

0

5

0

соединен с информационным входом триггера, выход которого соединен с адресным вхолом первого разряда элемента постоянной памяти и является третьим выходом блока сравнения.

0

5

Таблица 2

рие.2

Я

1

и

ot

W0MffJ

J

S89«gi

Туст. 1

Густ. 2

t

Фиа7

| Преобразователь кодов | 1986 |

|

SU1438008A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-04-15—Публикация

1987-03-16—Подача