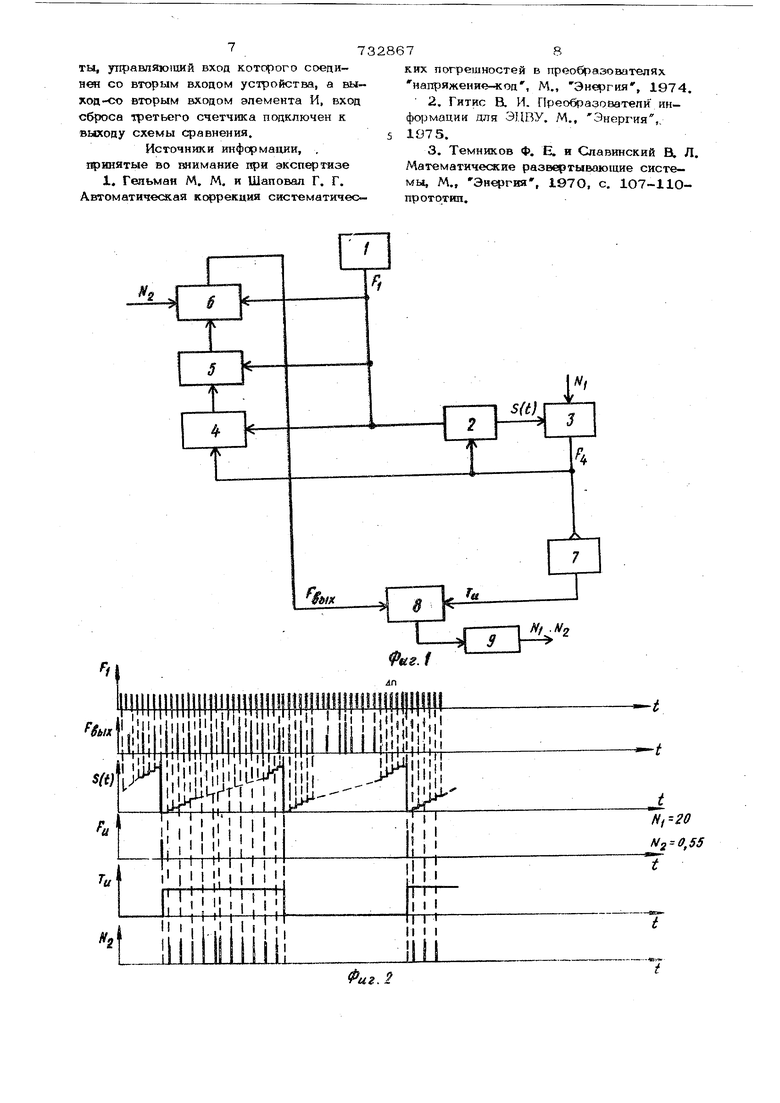

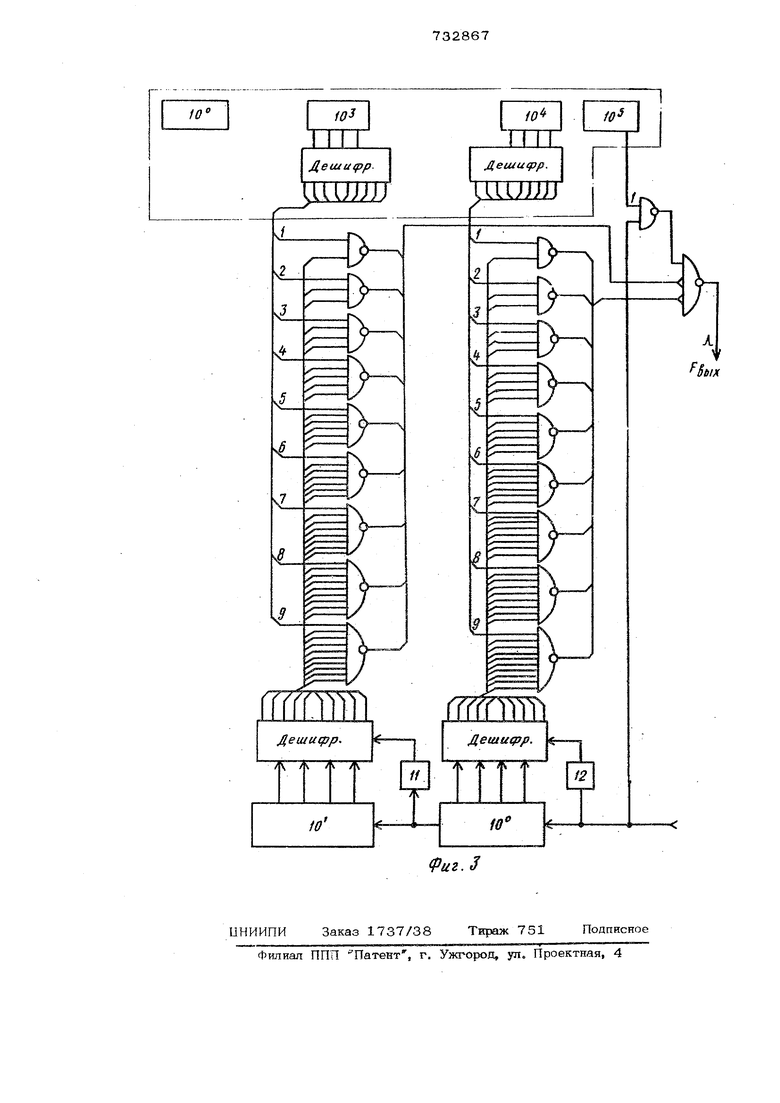

Изобретение относится к области вычислительной техники и предназначено, в частности, для использования в интегрируюищх цифровых вольтметрах, для автокоррекции, различных погрешностей. Используемые в цифровых во ьтметрах цифровые методы автокоррекции обыч но предусматривают использование ЦВМ в частности микропроцессоры lj iJ(2J. Недостатком таких устройств явлйется значительная избыточность таких устройств, которая приводит как к усложне нию устройств, так и к понижению их быст родействия. , Известно устройство для умножения, испбльзуемое для перемнмкения целого и дробнодёсятичного чисел в устройстве авггсжоррекции крутизны характеристики преобразования в интегрирующем цифровом вольтметре LSJ . Это устройство содержит счетчики, из которых соединен со входом схемы сравнения, генератор сшорной частоты, триггер, вход которого подключен к выходу схемы сравнения, а выход - с первым входом элемента И, выход которого через делитель частоты подключен ко входу второго счетчика. Выход схемы сравнения подключен ко входу сброса первого счетчика, вход которого соединен через другой делитель частоты с выходом генератора опорной частоты, выход которого подключен также ко входу другого эпемента , другие входы которо;го соединены со входом первого счетчика и выходом другой схемы сравнения, а выход - ко входу третьего счетчика, выход которого подключен ко входу другой схемой сравнения, выход подключен ко входу сброса третьего счетчика. Вход третьего счетчика соединен с другим входом пфвого элемента И fSj . В таком устройстве для обеспечения цифрового метода автокоррекшш, основанного на решении уравнения, H.vf:-N. - соответственно идеальное: и реальное значения кода напряжения; N - код номинального напряжения;й,| - разность идеального и ном нального кодов; производится перемножение двух целых чисец NjtHAH с последующим делением (сдвигом) на Ыц « 1,10,100 и т.д. При этом число NP преобразуется в пачки импульсов, а в результате последующего ,сдвига может появиться -погрешность до единицы младшего разряда. Общее время умножения Нр-лНц и сдвига на Н выражается формулой о ртак - частота генератора опорной частоты. Недостатками такого устройства являются недостаточная точн.ость и невысокое быстродействие. Для устранения указанных недостатков устройство для умножения, содержащее генератор опорной частоты, счетчики схему сравнения, счетный триггер и элемент И, причем выход первого счетчика подключен к пфвому входу схемы сравне ния, другой вход которой подключен к пе вому входу устройства, а выход к счет ному входу счетного триггера и входу сброса первого счетчика, выход счетного триггера подключен к пе эвпму входу элемента И, вЬссод Которого подключен к входу второго счетчика, выход которого соединен с выходом усзройства, содержит дюично-десятичный дешифратор и блок умножения частоты, причем выход генератора опорной частоты подключён к входам первого и третьего счетчиков, к управпйющему входу двоично-десятичного дешифратора к к одному входу блока умн же1йш частоты, выход третьего счетчика йодключен к входу двоично-десятичного яёшифратс оа, выход которого подключен к другому входу блока умножения частоты, управляющий вход которого соединен со &ХОДРМ устройства, а выход - со вторым входом элемента И, вход сброса третьего счетчика -подключен к выходу схемы сравнения. На фиг. 1 представлена функциональ. кая схема устройства; на фиг. 2 - временные диаграммы его работьц на фиг. 3ан пример выполнения блока умножения частоты. Устройство содержит генератор 1 опорой частоты, счетчик 2, схему 3 сравнения, счетчик 4, двоично-десятичный дешифратор 5, блок б умножения частоты, счетнЫй триггер 7, элемент 8 И,счетчик 9. На первый и второй входы устройства подаются числа. Н -лМниМ,, . Работает устройство следующий обре... зом. Импульсы опорной частоты F. пос-тупают с выхода генератсра 1 на входы счетчиков 2 и 4, на дешифратор 5 и на дин из входов блока 6 умножения частоты. Схема сравнения 3 выдает импульс когда значение содержимого счетчика достигает значения Нд , Эти импульсы с частотойР, поступают на вход счетного триггера 7 и входа сброса счетчиков 2 и 4, устанавливая счетчики 2 и 4 в исходные состояния. На счетного триггера 7 будут импульсы длительностью Т , которые поступают на один из входов элемента 8 И. Число 2. преобразуется в эквивалентную квазиравномерную (равномерную в пределах каждого десятичного paзpядa частоту следования импульсов Febix vNi. Производится это следующим образом, На вход цифрового счетчика 4 посту пают в течение Т и импулЕЛы с частоВыходы счетчика 4 соединег у со входами двоично-десятичного дешифр-а.тора 5, -на импульсный вход котфого поступают импульсы с частотой F/(, .На выходах декады дешифратора 5, соединенной с младшей декадой счетчика 4, будет равномерная последовательность импульсов с Частотой Рд , на выходах следующей декады.импульсы с частотой F и т.д. Импульсы с выходов дешифратора S поступают на входы блока б умножения частоты. Этот блок разделен на подблоки ,, входы кая4дого из которых соединены с определенной декадой дешифратора 5. Упрй. ляющие входы блока 6 подключены к дэ™сятйчному датчику числа М„ {в цифровы/ вольтметрах, например, датчиком чиагт.-: N,j. являются непосредственно декады дешис атора счетного блока прибора). Число K/j мгокно представить разряцаглн . единиц, десятых, сотых и т.п. Тогда вь ходы декады Датчика Н , соответстгг тоолйе десятым, подключаются к тому подблоку блока 6, который соединен с самой младшей декадой дешифратора 5, выходы декады датчика N,, соответс вующие сотым, подключаются к следующему подблоку блока 6 и т.д. Выход декадь датчика , соответствующей единице,, подключается к подблоку блока 6, на который поступаю импульсы с частотой F с выхода генератора 1 опорной частоты. Для пояснения работы блока 6 на фиг. Э приведена его конкретная схема, .где датчиком N,, являются декады памяти с дешифратором счетного блока 10 Элементы 11 и 12 задержки нужны для устранения возможного перекрытия импульсов. Декады дешифратора 5 имеют по 10 выходов, а каждый подблок блока 6 сос ит из элементов И-НЕ. На выходе J элемента И-НЕ в подблоке, соответству щем десятых числа N , надо получить равномерно следуюишх импульсов на каждые 10 импульсов с час тотой Рд , а в подблоке сотых -. импульсов на каждые 100 импульсов с частотой F , и т. д. Для обеспечения этого О -тый элемент И-НЕ каждого подблока должен быть соединен с вьь ходами соответствующей декады дешифр тора 5. Номера 6 этих выходов декады дешифратора определяются для каждого разряда числа Мл по формуле П-0,5. n-0,S 0 -у- , где п 1,2..., V - порядковый но мер импульса в последовательности выходных импульсов -того элемента И-НЕ соответствующего подблока блока 6, На выходе блока 6 имеем квазиравно мерную (в пределах каждого разряда) последовательность импульсов, с частотой .. Этиимпульсь поступают на другой вход элемента 8 И, на выходе которого в течение ФА- будут импульсы с частотой Fgy. . Число импульсов (в пачке длительностью Тп ) . Импульсы с выхода элемента 8 И подсчитываются счетчиком 0. Диапазон чисел N/j, , которые можно умножать с помощью устройства, от О до 1,999.... Это соответствует в наиболее распространенном случае двукратному перекрытию динамического диапазон счртного блока Ю. При использовании устройства в устройстве автокоррекции одновременно с ук ножением будет производиться операция вычитания, поскольку по мере фор мир ования числа N g импульсы с выхода эл мента 8 И будут поступать на счетчик, корректируя тем самым результат измерений. Заметим, что округление результата осуществляется автоматически в процессе преобразования числа N,fe ЙЫА Таким образом в данном устройстве дробно-десятичное число, каким является , непосредственно преобразуется в квазиравномерную последовательность импульсов с частотой g j получения результата умножения {без дополнительного округления) числа Й- на целое число л NU последовательность импульсов с частотой РВЫХ пропускается через элемент 8 И на вход счет о;. чика 9 в течение времени щее время умножения при этом будет -равно Tjj , а точность соответствует обычной точности цифровых устройств t 0,5 единицы младшего . Таким образом обеспечивается по сравнению с прототипом выигрыш в быст родействии 6 NpmrtiPss при повышении точности вдвое формула изобретения Устройство для умножения, содержащее генератор опорной частоты, счетчики, схему сравнения, счетный триггер и элемент И, причем выход первого счетчика подключен.к первому входу схемы сравнения, другой вход- которой подключен к первому входу устройства, а выход - к счетному входу счетного триггера и входу сброса первого счетчика, выход счетного триггера подключен к первому входу элемента И, выход которого подключен к входу второго счетчика, выход которсч о. соединен с выходом устройства, отличающееся тем, что, с целью повышения быстродействия и точности устройство содержит двоично-десятичный дешифратор и блок умножения частоты, причем выход генератора опорной частоты подключен к входам первого и третьего счетчиков, к управляю - щему входу двоично- десятичного дешифатора и к одному входу блока умнож&ния частоты, выход третьего счетчика одключен к входу двоично-десятичного ешифратора, выход которого подключен другому входу блока умножен1Ш частоты, управляющий вход котсрого соединен со вторым влодом устройства, а выход-со вторым входом элемента И, вход сброса -фетьего счетчика подключен к выходу схемы сравнения.

Источники информации, принятые во 1эдимание при экспертазе 1. Гельман М. М, и Шаповал Г. Г. Автоматическая кс рекция систематических погрешностей в преобразователях напряжение-код, М,, Энергия, 1974.

2,Гитис В. И. Преобразователи информации для ЭиВУ. М,, Энергия, 1975. .

3.Темников Ф. Е. и Славинский В. Л. Математические развертывающие системы, М., , 197О, с. 107-110прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель отношения временных интервалов | 1986 |

|

SU1322223A1 |

| Пересчетное устройство | 1982 |

|

SU1051698A1 |

| Цифровой частотомер | 1982 |

|

SU1190285A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Цифровой частотомер | 1985 |

|

SU1275314A2 |

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2043648C1 |

| Устройство цифрового времени | 1986 |

|

SU1377816A2 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1985 |

|

SU1396280A2 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

Фиг. 2

10

Авторы

Даты

1980-05-05—Публикация

1977-11-17—Подача