15

Изобретение относится к автоматике и цифровой вычислительной технике, может быть использовано при построении преобразователей в измерительных и управляющих системах и яв- ляется дополнительным к авт. св. № 970354.

Цель изобретения - повышение быстродействия преобразователя. jg

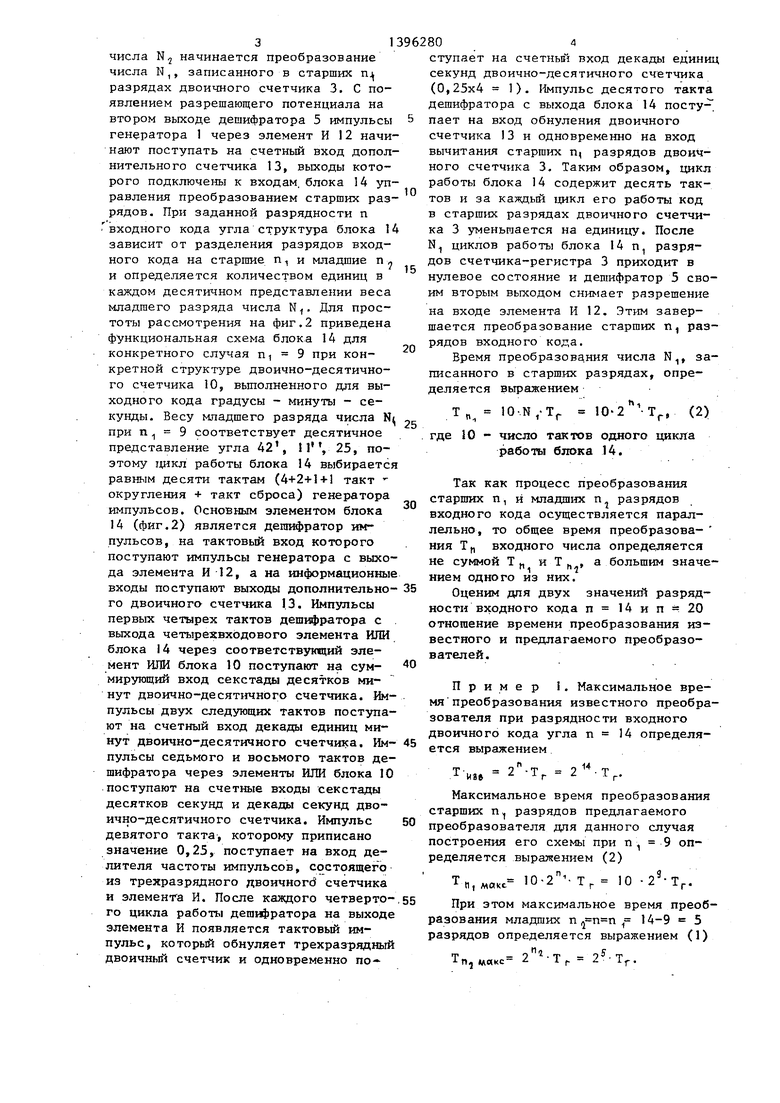

На фиг.1 приведена.структурная- схема преобразователя; на фиг.2 - пример исполнения фукнциональных схем блоков 14 и 10.

Преобразователь содержит (фиг.1) генератор 1 импульсов, первый элемент И 2, двоичный счетчик 3, информационный вход 4, дешифратор 5, сумматор 6, регистр 7, вход 8 задания константы, второй элемент И 9, двоич-2д но-десятичный счетчик 10, выход П, третий элемент И 12, дополнительный двоичный счетчик 13, блок 14 управ- .ления преобразованием старших разрядов входного кода.

Функциональные схемы блоков 14 и 10 для одного варианта исполнения (фиг.2)- содержат дешифратор 15 импульсов, двух- и четырех входовые элементы ИЛИ 16 и 17, делитель 18 частоты импульсов, содержащий элемент И 19 и трехразрядный двоичный счетчик 20, а также блок 10 - четыре двоично-десятичных 21, два двоично- шестеричных 22 и один двоичный 23 счетчика импульсов и четыре двухвхо- 35 довых элемента ИЛИ 24.

Преобразователь работает следующим образом.

В начале цикла преобразования производится обнуление регистра 7, дво- ично-десятичного счетчика 10, дополнительного двоичного счетчика 13 (эти цепи не показаны) и по информационному входу 4 в двоичньй счетчик-ре25

30

дешифратора 5 поступает разрешающ потенциал на второй вход элемента и импульсы генератора 1, поступаю на первый вход элемента И 2, проп каются через элемент И 2 и поступ ют на вход вычитания младших разр дов двоичного счетчика 3, на перв вход элемента И 9 и на тактовый в регистра 7.

Замкнутые в кольцо сумматор 6 регистр 7 представляют собой нака ливающийся сумматор, который на к дьй тактовый импульс добавляет к писанному в регистре 7 двоичному лу целочисленную константу С, сфо рованную на входе 8. Значение кон танты С (двоичного эквивалента ве младшего разряда входного кода Nj выбрано из условия исключения наб гающей ошибки и обеспечивает форм рование переноса на выходе суммат 6 в моменты времени, когда частич сумма дробньк частот кода N-j равн целой угловой единице - весу млад го разряда кода выходного двоично сятичного счетчика 10. Сигнал пер са, возникающий на выходе суммато 6, через некоторое число тактов з полнения сумматора 6 разрешает пр хождение импульсов через элемент на суммирующий вход двоично-десят ного счетчика 10.

В то же время, с поступлением к дого импульса генератора с выхода элемента И 2 на вход вычитания мл ших разрядов двоичного счетчика 3 код на выходе младших разрядов сч чика 3 уменьшается на единицу. По прохождения импульсов младшие раз ды регистра-счетчика 3 приходят в левое состояние и первым выходом шифратора 5 снимается разрешение входе и элементе.И 2. Ятим заверш

гистр 3 записывается входное число N 45 ется преобразование кода младших

в виде п-разрядного двоичного кода угла. Старшие п разрядов двоичного счетчика 3, имеющие преимущественно веса, соответствующие целым градусам, минутам и секундам части N,, входно - 50 го кода N, и младшие N,j разрядов этого же счетчика 3, имеющие веса с дробными частями секунд и образующие остальную часть N входного числа N, имеют раздельные счетные входы. При 55 этом К Ы + П1 + п-1.

Если код младших п разрядов отличается от нуля, то с первого выхода

д

5

5

0

дешифратора 5 поступает разрешающий потенциал на второй вход элемента И 2 и импульсы генератора 1, поступающие на первый вход элемента И 2, пропускаются через элемент И 2 и поступают на вход вычитания младших разрядов двоичного счетчика 3, на первый вход элемента И 9 и на тактовый вход регистра 7.

Замкнутые в кольцо сумматор 6 и регистр 7 представляют собой накапливающийся сумматор, который на каж- дьй тактовый импульс добавляет к записанному в регистре 7 двоичному числу целочисленную константу С, сформированную на входе 8. Значение константы С (двоичного эквивалента веса младшего разряда входного кода Nj) выбрано из условия исключения набегающей ошибки и обеспечивает формирование переноса на выходе сумматора 6 в моменты времени, когда частичная сумма дробньк частот кода N-j равна целой угловой единице - весу младшего разряда кода выходного двоично-десятичного счетчика 10. Сигнал переноса, возникающий на выходе сумматора 6, через некоторое число тактов заполнения сумматора 6 разрешает прохождение импульсов через элемент И 9 на суммирующий вход двоично-десятичного счетчика 10.

В то же время, с поступлением каждого импульса генератора с выхода элемента И 2 на вход вычитания младших разрядов двоичного счетчика 3 код на выходе младших разрядов счетчика 3 уменьшается на единицу. После прохождения импульсов младшие разряды регистра-счетчика 3 приходят в нулевое состояние и первым выходом дешифратора 5 снимается разрешение на входе и элементе.И 2. Ятим завершается преобразование кода младших

разрядов входного числа в унитарный код - число импульсов N, умножение его на константу С и преобразование целой части этого произведения в выходной двоично-десятичньй код угла. Время преобразования числа N, записанного в младших разрядах, определя- .ется выражением

Т sN-T ГП li-l Z r

где Т ,. - период повторения импульсов

генератора 1.

Одновременно с началом преобразования младших разрядов кода входного

числа Nj начинается преобразование числа N,, записанного в старших п разрядах двоичного счетчика 3. С появлением разрешающего потенциала на втором выходе дешифратора 5 импульсы генератора 1 через элемент И 12 начинают поступать на счетный вход дополнительного счетчика 13, выходы которого подключены к входам, блока 14 управления преобразованием старших разрядов. При заданной разрядности п входного кода угла структура блока 14 зависит от разделения разрядов входного кода на старшие п и младшие п и определяется количеством единиц в каждом десятичном представлении веса младшего разряда числа N , Для простоты рассмотрения на фиг,2 приведена функциональная схема блока 14 для конкретного случая п, 9 при конкретной структуре двоично-десятичного счетчика 10, выполненного для выходного кода градусы - минуты - секунды. Весу младшего разряда числа N при п 9 соответствует десятичное представление угла 42, II , 25, поэтому работы блока 14 выбирается равным десяти тактам (4+2+1+1 такт округления + такт сброса) генератора импульсов. Основным элементом блока 14 (фиг.2) является дешифратор импульсов, на тактовый вход которого поступают импульсы генератора с выхода элемента И 12, а на информационные входы поступают выходы дополнительно- го двоичнога счетчика 13. Импульсы первых че-пярех тактов дешифратора с выхода четырехвходового элемента ИЛИ блока i 4 через соответствуотций элемент ИЛИ блока 10 поступают на сум- мирующий вход секстады десятков минут двоично-десятичного счетчика. Им- пульсы двух следующих тактов поступают на счетный вход декады единиц минут двоично-десятичного счетчика. Им- пульсы седьмого и восьмого тактов дешифратора через элементы ИЛИ блока 10 поступают на счетные входы секстады десятков секунд и декады секунд двоично-десятичного счетчика. Импульс девятого такта, которому приписано значение 0,25, постзшает на вход делителя частоты импульсов, состоящего из трехразрядного двоичногб счетчика и элеменга И. После каждого четвертого цикла работы дешифратора на выходе элемента И появляется тактовый импульс, который обнуляет трехразрядный двоичньй счетчик и одновременно по

0

0

5 35 О . 45 50 55

ступает на счетньй вход декады единиц секунд двоично-десятичного счетчика (0,25x4 1). FiMnynbc десятого такта дешифратора с выхода блока 14 посту- пает на вход обнуления двоичного счетчика 3 и одновременно на вход вычитания старших П( разрядов двоичного счетчика 3, Таким образом, цикл работы блока 14 содержит десять тактов и за каждый цикл его работы код в старших разрядах двоичного счетчика 3 уменьшается на единицу. После N циклов работы блока 14 п, разрядов счетчика-регистра 3 приходит в нулевое состояние и дешифратор 5 своим вторым выходом снимает разрешение на входе элемента И 12. Этим завершается преобразование старших п, разрядов входного кода.

Время преобразования числа N, записанного в старших разрядах, определяется вьфажением

Т„ 10..N,-Tr

п, 10-2 -Т

г. (2)

где JO - число тактов одного цикла работы блока 14.

Так как процесс преобразования старших п, и младших п разрядов входного кода осуществляется параллельно, то общее время преобразова- ния Т входного числа определяется не суммой Т f, и Т , а большим значением одного из них.

Оценим для двух значений разрядности входного кода п 14 и п 20 отношение времени преобразования известного и предлагаемого преобразователей.

Пример i. Максимальное время преобразования известного преобразователя при разрядности входного двоичного кода угла п 14 определяется выражением

иге

2 -Т,

214

1 ,

Максимальное время преобразования старших п разрядов предлагаемого преобразователя для данного случая построения его схемы при п ;, 9 определяется выралгением (2)

т in п, макс г Г

При этом максимальное время преобразования младших п 14-9 5 разрядов определяется выражением (1)

п м«кс

, .

Так как Т,

Т

Make

ТО макси:мальное время преобразования предлагаемого преобразователя определяется выражением

а

Т,

предл

Тп,ллс,« 10-2 -Тг

Соотношение TU-. /Т

14

иве npeAл

к2 Тг 3,2.показывает, что время преобразования предлагаемого преобра:зователя в 3,2 раза меньше времени преобразования известного преобразователя.

Пример 2. Принимает разрядность входного кода п 20. С помощью аналогичных рассуждений можно показать, что время преобразования предлагаемого преобразова1селя в 204,8 раз меньше времени преобразования известного преобразователя.

Примеры 1 и 2 показывают, что эффективность предлагаемого преобразователя увеличивается с увеличением разрядности входного кода.

5Э

лгГ

:5

с

.5 d

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU881730A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

т

Строб

А4L

/5

09

6 5 it

ITJL

i±t

16

77

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1980 |

|

SU970354A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-15—Публикация

1985-06-05—Подача