1

Изобретение относится к вычислительной и измерительной технике;

Известны многоканальные анализаторы случайных процессов с непосредственным вводом данных, содержащие два входных аналого-цифровых преобразователя, устройство умножения, блок коммутируемых накопителей, коммутируемый сдвиговый регистр, предназначенный для создания задержки, число каскадов в котором меньше числа коммутируемых накопителей, но больше одного, и синхронизатор, предназначенные для нахождения оценок авто- и взаимных корреляционных функций, а также дешифратор с накопителями на выходе, подсоединенный к выходу преобразователя аналог-цифра, предназначенных для нахождения оценок одномерных дифференциальных или интегральных законов распределения.

Недостатком. известных анализаторов является слабое использование элементов схемы, отсутствие возможности нахождения оценок двумерных законов распределения. Это ограничивает функциональные возможности схем и сужает область применения устройС1ва.

Цель изобретения - расширить функциональные возможности устройства и создать возможность нахождения оценок двумерных

законов распределения за счет незначительного увеличения объема оборудования.

Предложенное устройство отличается от известных тем, что для управления прохождением кодов от преобразователя к дешифратору, необходимому при нахождении двумерных законов распределения, оно дополнительно содержит два вентиля, коммутатор Каскадов регистра, дешифратор с коммутатором

Н выходах, пересчетную схему и переключатель па два положения и два направления, соединенные таким образом, что выходы каналов коммутатора каскадов регистра подключены ко входам добавочного дешифратора, выходной коммутатор которого подключен к информационному входу первого вентиля, выход которого подключен к одному входу переключателя, а управляюш;ий вход- к выходу пересчетной схемы, вход которой

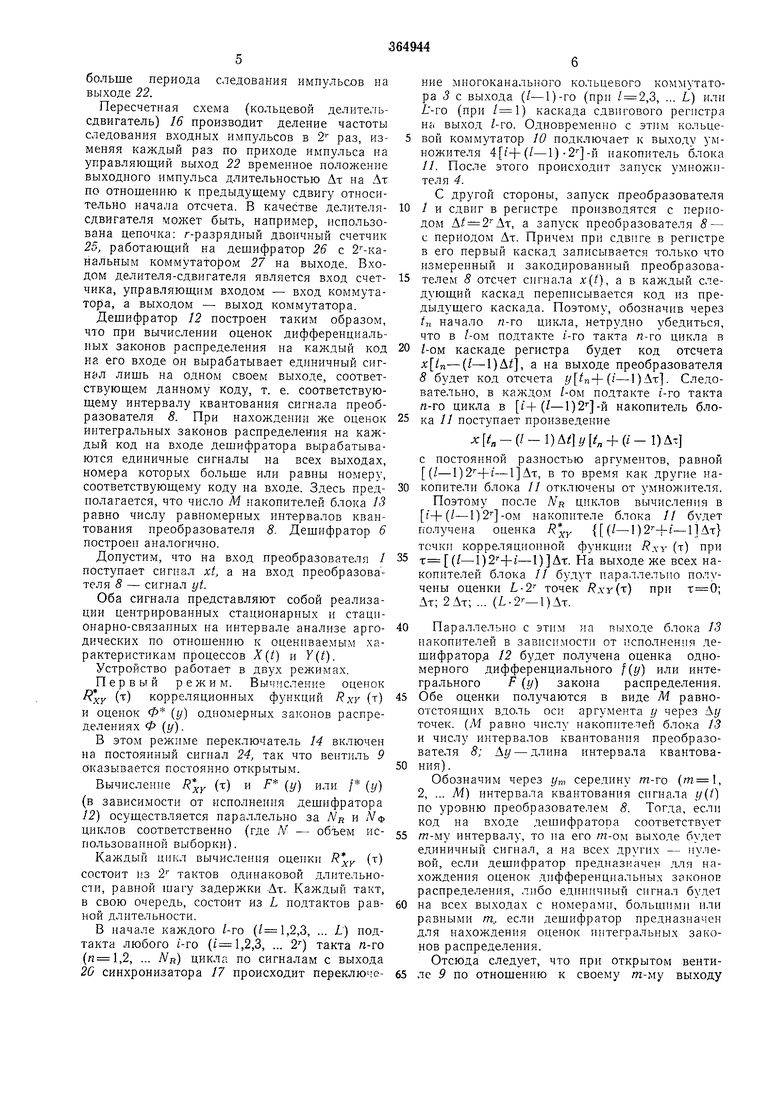

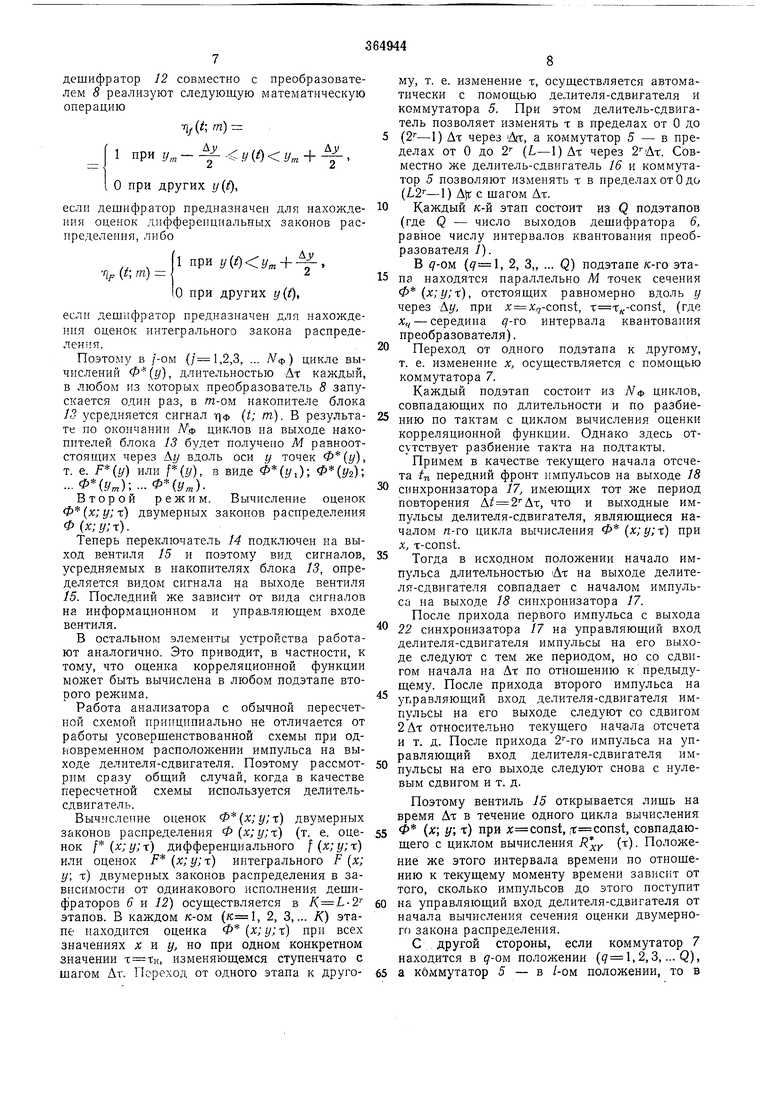

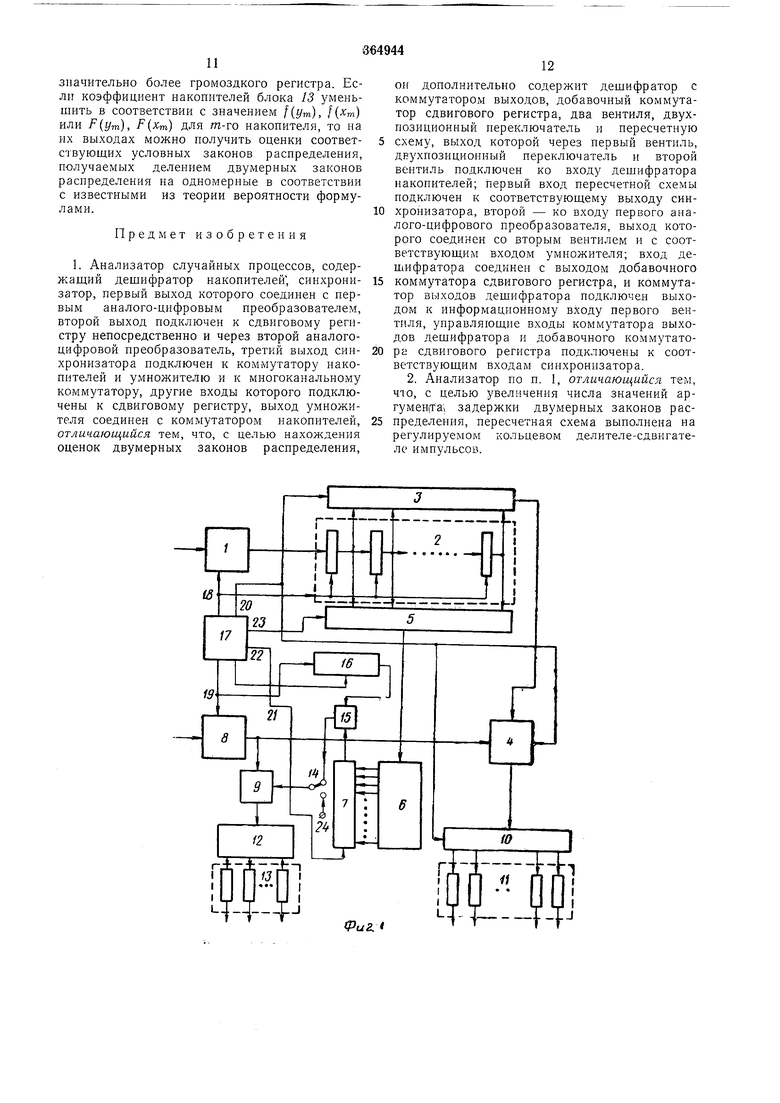

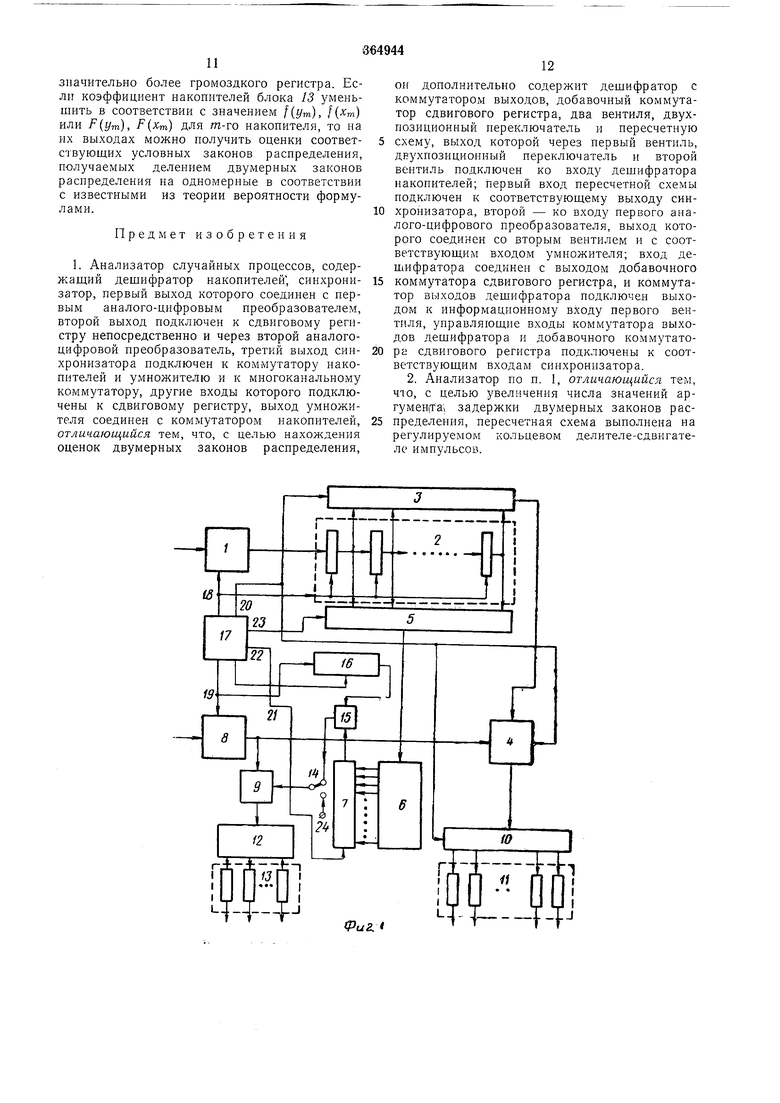

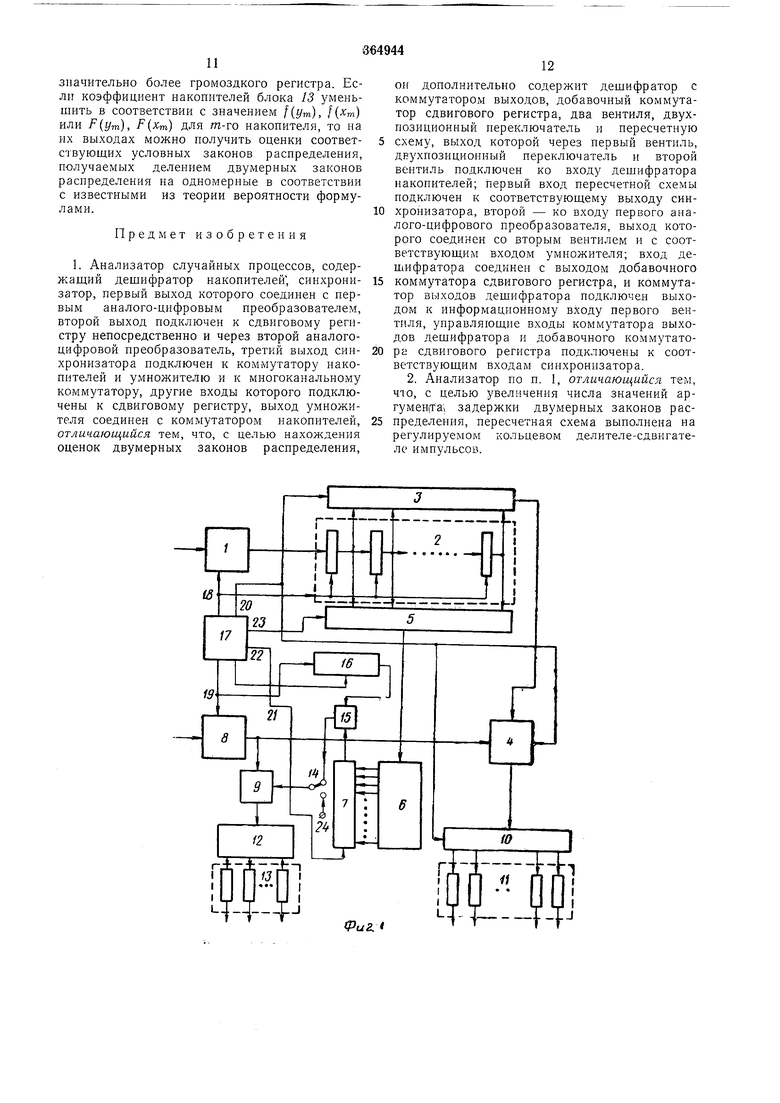

соединеи с управляющим входом преобразователя, работающего на умножитель. На второй вход переключателя подано постоянное напряжение, открывающее вентиль, а его выход подключен к управляющему входу второго вентиля, включенного между выходом преобразователя аналог-цифра, соединенного с устройством умножения, и входом исходного дешифратора с накопителями на выходах. Управляющие входы коммутаторов и пе3ресчетной схемы подключены к соответствующим выходам синхронизатора. В качестве пересчетной схемы предлагается использовать регулируемый кольцевой деЛ1:тель-сдвигатель импульсов, представляю-5 щнй собой устройство, позволяющее не тольхо делить частоту повторения входных имлульсов, но и изменять извне временное ноложрние выходного импульоа внутри всего пернода повторения ступенчато, с шагом,10 равным длительности импульса, равным, в свою очередь, периоду повторения входных импульсов. Последнее необходимо для правильной работы анализатора, если накопители закона распределеиня реагируют на ши-15 рину усредняемого импульса. Такое выполнение устройства позволяет расширить его функциональные возможности и обеспечить нахождение оценок двумерных дифференциальных илн интегральных (в за-20 висимости от исполнения дешифраторов) законов распределеиня. Если в качестве иересчетной схемы использовать обычную схему, производящую только деление частоты повторения входных нмпуль-25 сов на ностоянное число, то диапазон задержкн отсчетов одного сигнала по отношению к отсчетам второго сигнала при вычислении оценок двумерных законов распределения будет равен диапазону изменения ар-30 гумента оценки корреляционной функции. бднако шаг задержки для оценок двумерных законов распределепия будет больше шага задержки (шага изменения аргумента) для опенок корреляционных функций во столько35 раз, во сколько число каскадов регистра меньше числа коммутируемых накопителей, включенных на выходе умножителя (целесообразно, чтобы этот коэффициент кратности был степенью двойки). Это приводит к то-40 му, что число значений аргумента задержки оценок двумерного закона распределения оказывается меньше потенциально возможного нри принятом в устройстве способе осуществления задержки для нахождения оце-45 нок корреляционных функций. Поэтому шаг задержки оценок двумерных законов распределения умеиьшают, сделав его равным шагу изменения аргумента оценки корреляционной функции, в связи с чем и50 предлагается в качестве пересчетной схемы использовать делитель-сдвигатель. Это позволяет регулировать задержку при вычислении оценок двумерных законов распределения с тем же шагом и в том же диа-55 пазоне, что и при вычислении оценок корреляционных функций, т. е. полностью использовать возможности устройства задержки анализатора. На фиг. 1 изображена блок-схема устрой-60 ства; на фиг. 2 - блок-схема регулируемого делителя-сдвигателя. Аналого-цифровой преобразователь 1 подключен ко входу сдвигового регистра 2, который через многоканальный коммутатор 365 . 4 соединен с умножителем 4, а через добавочный коммутатор 5 сдвигового регистра с дешифратором 6, к выходам которого подключей коммутатор 7. Другой вход умножителя 4 подключен на выход второго аналого-цифрового преобразователя 8 на который подключей также информационный вход вентнля 9. Выход умножителя 4 соединен с информационным входом коммутатора 10 накопителей, выходы которого соединены с блоком 11 накопителей. Выход вентиля 9 подключен к входу дешифратора 12 наконителей, выходы которого соединены с блоком 13 накопителей. Управляющий вход вентиля 9 подключен к выходу двухнозиционного переключателя 14, на один вход которого включен выход первого вентиля 15, информационный вход которого подключен к выходу коммутатора 7 выходов дешифратора 6, а управляющий вход -- к выходу пересчетной схемы 16 кольцевого делителя-сдвигателя. Синхронизатор 17 включен таким образом, что его выход 18 подключен к управляющему входу преобразователя / и к цепи сдвига регистра 2, выход 19 подключен к управляющему входу преобразователя 8. и ко входу пересчетной схемы 16. Выход 20 подключен одновременно к управляющим входам коммутаторов 3, 10 и умножителя 4. Выход 21 подключен к управляющему входу коммутатора 7, выход 22 - к управляющему входу пересчетной схемы 16 и, выход 25 - к управляющему входу коммутатора 5. На второй вход переключателя 14 подается постоянный сигнал 24, открывающий вентиль 9. Устройство работает следующим образом, Положим, что число накопителей блока И в 2 раз больше числа каскадов регистра 2 (где ). Это позволяет наиболее полно использовать элементы схемы. Тогда коэффициент пересчета делителя-сдвигателя должен быть равен 2 а период Ы следования импульсов на выходе 18 синхронизатора 17 в 2 раз больше периода Ат следования импульсов иа выходе 19, равного шагу задержки, т. е. шагу изменения аргумента оценки корреляционной функции и временного аргумента т оценок двумерных законов распределеиия. Период следования импульсов на выходе 20 синхронизатора 17 в L раз меньше Ат (где L - число каскадов регистра 2). Период следования импульсов на выходе 21 равен времени однократного усреднения точек одного сечения двумерного закона с помощью блока накопителей 13. Период следования импульсов на выходе 22 синхронизатора /7 в Q раз больше периода следования импульсов на выходе 21 (где Q - число выходов дешифратора 6, равное числу интервалов квантования преобразователя /,). Период следования импульсов на выходе 23 в 2 раз больше периода следования импульсов на выходе 22. Пересчетная схема (кольцевой делительсдБИгатель) 16 производит деление частоты следования входных импульсов в 2 раз, измеияя каждый раз по приходе импульса на управляющий выход 22 временное положение выходного импульса длительностью Дт на Ат по отиошеиию к предыдущему сдвигу относительно начала отсчета. В качестве делителясдвигателя может быть, например, использована цепочка: г-разрядный двоичный счетчик 25, работающий на дешифратор 26 с 2 -канальным коммутатором 27 на выходе. Входом делителя-сдвигателя является вход счетчика, управляющим входом - вход коммутатора, а выходом - выход коммутатора. Дешифратор 12 построен таким образом, что при вычислении оценок дифференциальных законов распределения на каждый код на его входе он вырабатывает единичный сигнал лищь на одном своем выходе, соответствующем данному коду, т. е. соответствующему интервалу квантования сигнала преобразователя 5. При нахождении же оценок интегральных законов распределения на каждый код на входе дешифратора вырабатыва ются единичные сигналы на всех выходах, номера которых больше или равны номеру. соответствующему коду на входе. Здесь предиолагается, что число М накопителей блока 13 равно числу равномерных интервалов квантования преобразователя 8. Дешифратор 6 построен аналогично. Допустим, что на вход преобразователя / поступает сигнал xf, а на вход преобразователя 8 - сигнал yt. Оба сигнала представляют собой реализации центрированных стационарных и стационарно-связанных на интервале анализе аргодических по отношению к оцениваемым характеристикам ироцессов X(t) и Y(t). Устройство работает в двух режимах. Первый режим. Вычисление оценок j, (т) корреляционных функций КХУ (т) и оценок Ф (у) одиомериых законов распределениях Ф (у). В этом режиме переключатель 14 включен на постоянный сигиал 24, так что вентиль 9 Оказывается постоянно открытым. Вычисление (т) и F (у) или / (у) (в зависимости от исполнения дешифратора 12) осуществляется параллельно за и N циклов соответственно (где .V - объем исиользоваиной выборки). Каждый цикл вычисления оценки (т) состоит из 2 тактов одинаковой длительности, равной 1иагу задержки Дт. Каждый такт. в свою очередь, состоит из L подтактов равной длительности. В начале каждого 1-го (,2,3, ... L) подтакта любого t-ro (i 1,2,3, ... 2) такта п-го ,2, ... Nn) цикла по сигналам с выхода 2G синхронизатора 17 происходит переключение многоканального кольцевого коммутатора 5 с выхода (/-1)-го (при / 2,3, ... L) или L-ro (при ) каскада сдвигового регистра Hci выход /-ГО. Одновременно с этим кольцевон коммутатор 10 подключает к выходу умножителя 4(+(/-1) накопитель блока //. После этого происходит запуск умножителя 4. С другой стороны, запуск преобразователя / и сдвиг в регистре производятся с периодом Дг 2Дт, а запуск преобразователя S - с периодом Дт. Причем при сдвиге в регистре в его первый каскад записывается только что измеренный и закодированный преобразователем 8 отсчет сигнала л-(/), а в каждый следующий каскад иереписывается код из предыдущего каскада. Поэтому, обозначив через /„ начало п-то цикла, нетрудно убедиться, что в /-ОМ подтакте ;-го такта п-го цикла в /-ом каскаде регистра будет код отсчета (l-1)Д, а на выходе преобразователя 5 будет код отсчета (г-1)Дт. Следовательио, в /-ом подтакте г-го такта п-го цикла в t+(/-1) накопитель блока 11 поступает произведение г. /; плл ГУ i / 1 л i - V - ) У пг ( с постоянной разностью аргументов, равной (/-1)2Ч-1-1 Дт, в то время как другие накопители блока // отключены от умножителя, Поэтому после Лд циклов вычисления в +(/-1) накопителе блока // будет получена опенка {(I-l)2+t-1 Дт} точки корреляционной функции R.Y (т) при т(/-l)2-|-i-1)Дт. На выходе же всех накопителей блока // будут параллельно получены оценки L-2 точек (т) при Дт; 2Дт; ... (L.2--1)Дт. Параллельно с этим на выходе блока 13 накопителей в зависи.мости от исполнения дещифратор.а 12 будет получена оценка одномерного дифференциального f(y) или интегрального F (у) закона распределения. Обе оценки получаются в виде М равноотстоящих вдоль оси аргумента у через Дг/ точек. (М равно числу накопителей блока 13 и числу интервалов квантования преобразователя 8; Ау - длина интервала квантования). Обозначим через г/,,, середину т-го (, 2, ... Ai интервала квантования сигнала y(t} по уровню преобразователем 8. Тогда, если код на входе дешифратора соответствует т-му интервалу, то на его т-ом выходе будет единичный сигнал, а на всех других - нулевой, если дешифратор предназначен для нахождения оценок дифференциальных законов распределения, либо единичный сигнал будет на всех выходах с номерами, большими или равными т„ если дешифратор предназначен для нахождения оценок интегральных законов расиределеиия. Отсюда следует, что при открытом вентиле 9 по отношению к своему т-му выходу

дешифратор 12 совместно с преобразователем 8 реализуют следующую математическую операцию

flf() 1 приу,„-А,(у + ,

О при других y(f),

если дешифратор предназначен для нахождения оценок дифференциальных законов распределения, либо

1 при у(),/ + -.

(t; т

О при других y(f),

если дешифратор предназначен для нахождения оценок интегрального закона распределен я.

Поэтому в /-ОМ (,2,3, ... Мф) цикле вычислений ), длительностью Дт каждый, в любом из которых преобразователь 8 запускается один раз, в т-ом накопителе блока 13 усредняется сигнал Г1Ф (t; т. В результате по окончании Лф циклов па выходе накопителей блока 13 будет получено М равноотстоящих через Ау вдоль оси у точек Ф(у), т. е. F(y) или f(y), в виде Ф(у,); Ф(г/2); ...Ф(Уп,);...).

Второй режим. Вычисление оценок Ф(х;у;- :) двумерных законов распределения Ф{х;у;г).

Теперь переключатель 14 подключен на выход вентиля 15 и поэтому вид сигналов, усредняемых в накопителях блока 13, определяется видом сигнала на выходе вентиля 15. Последний же зависит от вида сигналов на информационном и управляющем входе вентиля.

В остальном элементы устройства работают аналогично. Это приводит, в частности, к тому, что оценка корреляционной функции может быть вычислена в любом подэтапе второго режима.

Работа анализатора с обычной пересчетной схемой принципиально не отличается от работы усовершенствованной схемы при одновременном расположении импульса на выходе делителя-сдвигателя. Поэтому рассмотрим сразу общий случай, когда в качестве пересчетной схемы используется делительсдвигатель.

Вычисление оценок Ф(л;;г/;т) двумерных законов распределения Ф (л;;г/;т) (т. е. оценок Г{х;у;т:) дифференциального f{x;y;t) или оценок Р(х;у;т:) интегрального F (х; у; т) двумерных законов распределения в зависимости от одинакового исполнения дещифраторов 6 и 12) осуществляется в K. L-2 этапов. В каждом /с-ом (, 2, 3,... К) этапе находится оценка Ф (х;у;т:) при всех значениях л; и г/ но при одном конкретном значении , изменяющемся ступенчато с шагом At. Переход от одного этапа к другому, т. е. изменение т, осуществляется автоматически с помощью делителя-сдвигателя и коммутатора 5. При этом делитель-сдвигатель позволяет изменять т в пределах от О до (2-1) AT через Art, а коммутатор 5 - в пределах от О до 2 (L-1)Ат через 2Ат. Совместно же делитель-сдвигатель 16 и коммутатор 5 позволяют изменять т в пределах от О до () Ajr с щагом Ат.

Каждый к-й этап состоит из Q подэтапов (где Q - число выходов дешифратора 6, равное числу интервалов квантования нреобразователя /).

В -ом (1, 2, 3,, ... Q) подэтапе к-го этаПсП находятся параллельно М точек сечения Ф (л:; г/;т), отстоящих равномерно вдоль у через Ау, при .or,i, T T -const, (где x,f - середина -го интервала квантования преобразователя).

Переход от одного подэтапа к другому, т. е. изменение х, осуществляется с помощью коммутатора 7.

Каждый подэтап состоит из Лф циклов, совпадающих по длительности и по разбиеПИЮ по тактам с циклом вычисления оценки

корреляционной функции. Однако здесь отсутствует разбиение такта на подтакты.

Примем в качестве текущего начала отсчета tn передний фронт импульсов на выходе 18

синхронизатора 17, имеющих тот же период повторения А/ 2Ат, что и выходные импульсы делителя-сдвигателя, являющиеся началом п-го цикла вычисления Ф (х;у;т;) при X, t-const.

Тогда в исходном положении начало импульса длительностью Ат на выходе делителя-сдвигателя совпадает с началом импульса на выходе 18 синхронизатора 17.

После прихода первого импульса с выхода

22 синхронизатора 17 на управляющий вход делителя-сдвигателя импульсы на его выходе следуют с тем же периодом, но со сдвигом начала на Дт по отношению к предыдущему. После прихода второго импульса па угфавляющий вход делителя-сдвигателя импульсы на его выходе следуют со сдвигом 2Ат относительно текущего начала отсчета и т. д. После прихода 2-го импульса на управляющий вход делителя-сдвигателя импульсы на его выходе следуют снова с нулевым сдвигом и т. д.

Поэтому вентиль 15 открывается лишь на время Ат в течение одного цикла вычисления

Ф (х; у, t) при x const, ,Tr const, совпадающего с циклом вычисления (т). Положение же этого интервала времени по отнощению к текущему моменту времени зависит от того, сколько импульсов до этого поступит

на управляющий вход делителя-сдвигателя от начала вычисления сечения оценки двумерного закона распределения.

С другой стороны, если коммутатор 7 находится в -ом положении ( 1,2,3,... Q),

а к&ммутатор 5 - в /-ом положении, то в п-ом цикле на информационный вход вентиля 15 с -го выхода дешифратора 6 поступает код нелинейного преобразования. Qy(fn;q;f) 1 при x,,-(l-l) О при других xltn - (l - }&.t, если дешифратор 6 предназначен для нахождения оценок дифференциальных законов распределения, либо ер(„; q; О ), 1 при xlt„-(i о при других -(/ -1)Д/, если дешифратор 6 предназначен для нахождения оценок интегральных законов распределения, (где Хд - среднее значение, а Лл: - ширина -го интервала квантования сигнала x{t преобразователем /). Поэтому после а-го (,2,3, ...2; I,2,3...2 1,2...) импульса на выходе 22 синхронизатора 17, когда делитель-сдвигатель осуществляет сдвиг выходного импульса на интервал ссДт по отношению к текушему началу отсчета tn (к началу п-го цикла вычислений), на вход т-го накопителя блока 13 проходит сигнал, равный произведению Хф(г„; т; ; /; а)--/1ф (/„+о-Дт;т)-вф(г„; q; /). Это значит, что если дешифраторы выполнены для нахождения оценок дифференциальных законов распределения, то 7./(«; m;q; а; /) 1 при .,(-l).A: + у С+:аА. , 0при других -(/-1) и/или у 1(„ + 5Дт1, S : 1,2,.. .л ... 2 Если же дешифраторы выполнены для нахождения опенок интегральных законов распределения, то /. m;q;:a.-l) 11 при X (Г- 1) Д Xq + {И + аД-:1 г/„ + , О при других X /„ - (/ - 1) Д/, и/или + 5Дт, ,2, ...а,...2. Полученные соотношения обусловлены тем, что вентиль 15 оказывается открытым но управляющему входу лишь в течение а-го такта цикла, а поэтому другие отсчеты y(Q, г/(„ +AT),... («-)AT, У 1):Ат,. .Vr/IC+ , не могут пройти через вентиль 9, даже если на выходе коммутатора 7 - единичный сигнал. А это соответствует получению на выходе блока накопителей 13 после циклов усреднения в пределах одного подэтапа одного этапа М равноотстоящих вдоль у с шагом Дг/ точек сечения Ф (х; у; т) при х у г/,, у, у„ ... у„; т - аДт + (/ - 1) Д а + (/ - 1)2 Дт. Все же сечения оценки Ф (х; у; т) получаются следующим образом. В первом подэтапе первого этапа коммутаторы 7 и 5 находятся в первом положении, делитель-сявигатель обеспечивает нулевой сдвиг импульса. Запуск преобразователей , 8 ц сдвиг в регистре 2 осуществляется так же, как в первом режиме. Поэтому после циклов вычисления получается М точек оценки Ф (х; у; т) при (поскольку коммутатор 7 находится в положении 1) , г/9, ... Ум (так как на выходе блока накопителей 13 получается сразу М точек оценки), . После этого по окончании считывания полученных оценок импульсом с выхода 21 синхронизатора 17 коммутатор 7 переводится во второе положение. Начинается второй подэтап первого этапа, в котором находится Ф (х; у; т) при х - х.,; у у„ г/з,..,у„; t 0. Далее аналогично находят М точек Ф (х; г/; т) при , х, ... XQ, но при . После этого коммутатор 7 опять ставится в первое положение, но на управляющий вход лелителя-сдвигателя поступает импульс, в результате чего его выходной импульс сдвигается на Дт. Начинается второй этап. Теперь за О подэтапов производятся вычисления всех Q сечений Ф (х; г/; т) вдоль , лго, ... .VQ по Af точек вдоль 2,... Ум, но теперь при . В третьем этапе 2 Дт и т. д., в 2-ом этапе т(2-1)Дт. В начале (2Ч-1)-го этапа делитель-сдвигатель опять дает нулевой сдвиг импульса, но теперь коммутатор 5 ставится в первое положение. В результате т 2Дт и за Q подэтапов опять находятся Q сечений вдоль X по М точек вдоль у при данном т. Затем делитель-сдвигатель добавляет еще Дт, становится т(2+1)Дт и т. д. до (22-1) Дт. Далее коммутатор 5 переходит в положение 2,4т будет равно 2.2Дт и т. д. пока в L.2-OM этапе т не станет равным (L2- -1) Дт. По его окончании вычисление оценки Ф (х: у, т) при всех возможных значениях х, у, т заканчивается. Если число каскадов регистра 2 равняется ислу накопителей блока //, то необходимость в вентиле /5 и лелителе-сдвигателе отадает. Однако это требует использования

И

значительно более громоздкого регистра. Если коэффициент накопителей блока 13 уменьшить в соответствии с значением 1(Ут), f(Xm) или Р{ут), F(xm) ДЛЯ /п-го накопителя, то на их выходах можно получить оценки соответствующих условных законов распределения, получаемых делением двумерных законов распределения на одномерные в соответствии с известными из теории вероятности формулами.

Предмет изобретения

1. Анализатор случайных процессов, содержащий дещифратор накопителей; синхронизатор, первый выход которого соединен с первым аналого-цифровым преобразователем, второй выход подключен к сдвиговому регистру непосредственно и через второй аналогоцифровой преобразователь, третий выход синхронизатора подключен к коммутатору накопителей и умножителю и к многоканальному коммутатору, другие входы которого подключены к сдвиговому регистру, выход умножителя соединен с коммутатором накопителей, отличающийся тем, что, с целью нахождения оценок двумерных законов распределения.

364944

12

он дополнительно содержит дещифратор с коммутатором выходов, добавочный коммутатор сдвигового регистра, два вентиля, двухпозиционный переключатель и пересчетную

схему, выход которой через первый вентиль, днухггозиционный переключатель и второй вентиль подключен ко входу дешифратора накопителей; первый вход пересчетной схемы подключен к соответствующему выходу синхронизатора, второй - ко входу первого аналого-цифрового преобразователя, выход которого соединен со вторым вентилем и с соответствующим входом умножителя; вход дешифратора соединен с выходом добавочного

коммутатора сдвигового регистра, и коммутатор выходов дешифратора подключен выходом к информационному входу первого вентиля, управляющие входы коммутатора выходов дещифратора и добавочного коммутатора сдвигового регистра подключены к соответствующим входам синхронизатора.

2. Анализатор по п. 1, отличающийся тем, что, с целью увеличения числа значений аргумен.та; задержки двумерных законов распределения, пересчетная схема выполнена на регулируемом кольцевом делителе-сдвигателе импульсов.

i-LJ

Фиг.

блод

ь.

2б

Y

1I

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный статистический анализатор | 1977 |

|

SU732890A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| БИБЛИОТЕКА | 1973 |

|

SU383057A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1970 |

|

SU275542A1 |

| КОРРЕЛЯТОР | 1972 |

|

SU424153A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU384115A1 |

| Устройство для определения закона распределения | 1987 |

|

SU1520545A1 |

| Устройство для диагностики дефектов машин и механизмов циклического действия | 1983 |

|

SU1138679A1 |

, Вшход

Риг.2

Авторы

Даты

1973-01-01—Публикация