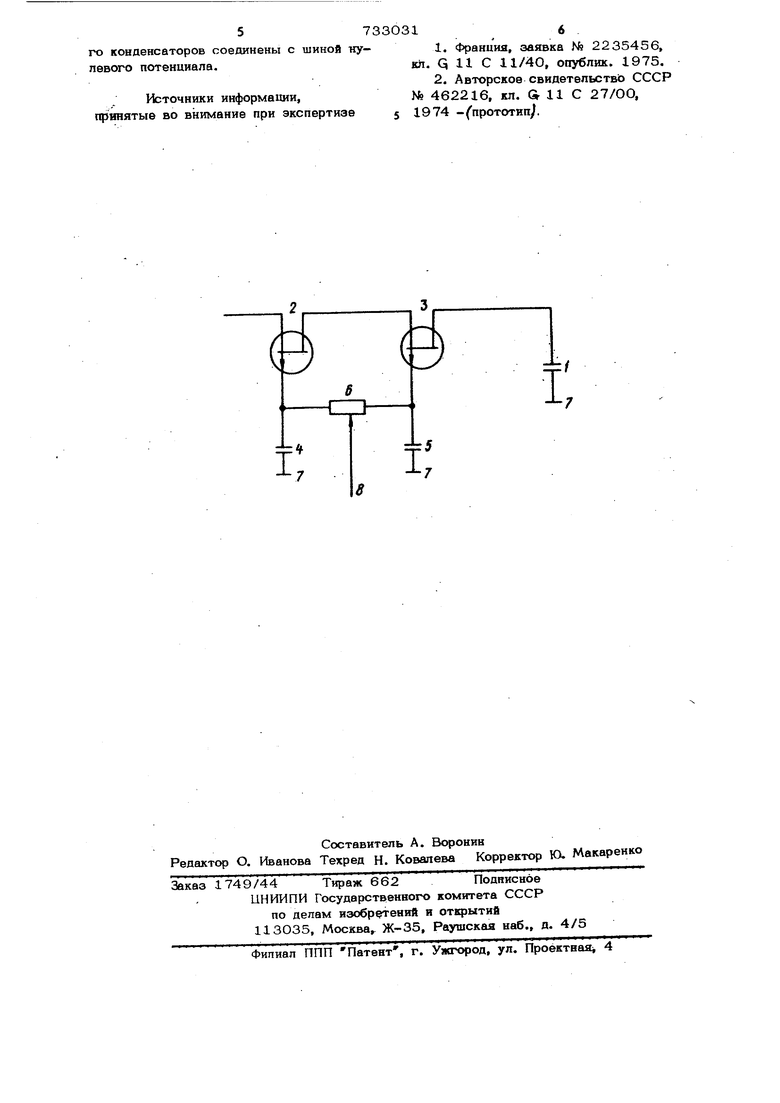

Изобретение относится к области импупьсной техники и может быть использовано в устройствах автоматики, аналсйговой вычислительной техники и различных радиоэлектронных устройствах Известна ячейка аналоговой памяти, содержащая ключ на полевом транзистор исток которого подключен к источнику входного сигнала, сток соединен с одной из обкладок запоминающего конденсатора, другая обкладка которого соединена с шиной нулевого потенциала, а затвор с шиной управления iQ. Существенный недостаток известной Ячейки памяти заключается ъ том, что при работе ключа через паразитные емкости поступают разнопопярные импульсы обусловленные передним и задним фронтами импульса управления, имеющие, как правило, различные длительности и ампли туды, которые интегрируются на запоминающем конденсаторе и приводят к появлению постоянного помехового сигнала. Наиболее близким техническим решением является ячейка аналоговой памяти, содержащая ключ на МОП-транзисторе, исток которого подключен к источникгу входного сигнала, сток - к одной из обкладок конденсатора, другая обкладка которого соединена с шиной нулевого потенциала, а затвор - к управляющей шине, соединенной через инвертор с затвором дополнительного ключа на МОП-транзисторе, сток которого соединен со стоком МОПтранзистора-ключаВыбросы ключей поступают в цепь сигнала в противофазе и компенсируют друг друга. Однако полная компенсация выбросов возможна только при полной идентичности параметров полевых транзисторов и строгом равенстве длительности фронтов импульсов в шине управления и на выходе инв тирующего элемента. Цель изобретения - повышение точнос.ти запоминания ячейки. Поставленная цель достигается тем, что в ячейку аналоговой памяти, содержащую первый накопительный элемент, например конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, первый ключ, например первый полевой транзистор, исток которого соединен со входом ячейки, второй ключ, например второй попевой транзистор, и шину управления, введены второй и третий накопительные элементы, например конденсаторы , регулирующий элемент, например переменный резистор, подвижный контакт которого подключен к шине управления, первый вывод переменного резистора соединен с одной из обкладок второго конденсатора и затвором первого полевого транзистора, сток которого соединен с истоком второго полевого транзистора, сток второго полевого тран зистора подключен к другой обкладке пер вого конденсатора, второй вывод переменного резистора соединен с затвором второго полевого транзистора и одной из обкладок третьего конденсатора, друГле обкпадки второго и третьего конденсаторов соединены с шиной нулевого потенциала. Изобретение поясняется чертежом, на котором представлена схема предлагаемой ячейки аналоговой памяти. Ячейка памяти содержит первый нако пительный элемент 1, например конденсатор, первый 2 и второй 3 ключи, например первый и второй полевые транзисторы, второй 4 и третий 5 накопительны элементы, например конденсаторы, одни из обкладок которых соединены с соответствующими выводами регулирующего элемента 6, например переменного резистора, другие обкладки конденсаторов 1, 4 и 5 подключены к шине 7 нулевог потенциала, подвижный контакт переменного резистора 6 соединен с шиной 8 управления, При поступлении с шины 8 управлени импульса ключ 3 в своей работе запаздывает по отношению к ключу 2 и отсекает часть его выброса, обусловленного передним фронтом импульса управления, в противном случае ключ 3 будет отсекать часть заднего выброса в ключе 2. При регулировании С-цепочек изменяется энергия выбросов ключей и величина отсечки выбросов ключа 2. При определенном соотношении постоянных времен (сопротивление части переменно резистора 6 и емкость соответствующе74 о конденсатора) возможна полная взаимая компенсация выбросов ключей на онденсаторе 1 . Включение последовательно с 2 ключа 3, опережающего ипи отстащего в своей работе в ключе 2 при егулировании постоянных времени интегирующих RC-цепочек в цепях затвоов обоих транзисторов, позволяет устраить постоянный помеховый сигнал на онденсаторе 1 с необходимой степенью очности, исключить из схемы инвертиующее устройство и применять любые ары транзисторов одного типа без редварительного подбора по параметрам, также сделать схему некритичной к лительности фронтов управляющего импульса. Регулировка постоянных времени интегрирующих f C-цепочек упрсщается, ли последние собраны на двух конденсаторах и одном потенциометре, а сигнал управления подается на среднюю точку потенциометра. формула из об р е т а н и я Ячейка аналоговой памяти, содержащая первый накопительный элемент, например конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, первый ключ, например первый полевой транзистор, исток которого соединен со входом ячейки, второй/ключ, например второй полевой транзистор, и шину управления, отличающаяс я тем, что, с целью повышения точности запоминания ячейки, в нее введены второй и третий накопительные элементы, например конденсаторы, регулирующий элемент, например переменный резистор, подвижный контакт которого подключен к шине управления, первый вывод переменного резистора соединен с одной из обкладок второго конденсатора и зaтвopo l первого полевого транзистора, сток которого соединен с истоком второго полевого транзистора, сток второго полевого транзистора подключен к другой обкладке первого конденсатора, второй вывод переменного,, резистора соединен с затвором второго полевого транзистор41 и одной из обкладок третьего конденсатора, /Чугие обкладки второго и третье-го конденсаторов соединены с шиной ну- певого потенциала.

Источники информации, принятые во внимание при экспертизе

1.Франция, заявка № 2235456, Kh. Q 11 С 11/40, опублик. 1975.

2.Авторское свидетепьствь СССР № 462216, кл. Gr 11 С 27/00,

1974 - прототип/.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1980 |

|

SU943853A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU890440A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU881864A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU575700A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU980164A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1014040A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Аналоговое запоминающее устройство | 1976 |

|

SU599283A1 |

Авторы

Даты

1980-05-05—Публикация

1977-11-09—Подача