(54) ЯЧЕЙКА ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU805412A1 |

| Ассоциативная ячейка памяти | 1976 |

|

SU605268A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Элемент памяти | 1979 |

|

SU788175A1 |

, Изобретение относится к вычисли- тепьвой технике, а именно к запоминающим ус-рройствам (ЗУ).

Дпя устройств параппепьной обратной . информации, например, ассоциативных .. процессов, многофункциональных ЗУ, при выполнении логических или арифметических операций возникает необходимость записи результата операции входного слова с некоторым множеством слов ЗУ : непосредственно в запоминающие элементы (внутренняя перезапись). Для ассоциативньге процессов на МДП-тра1Нзисторах это требует последовательного выполнения операций воразрядного ассоциативного поиска и записи, что увепичнвают время вышпнения операций l.

В подобных устройствах могут ИЕ пользоваться достаточно простьте запоминаюшйе элементы. Однако в них выполнение широкого набора логических операций внутри элемента практически невозможно. Возможность выпопнеНия логических- операций внутри элемента мо2

жет повысить быстродействие устройств параллельной обработки

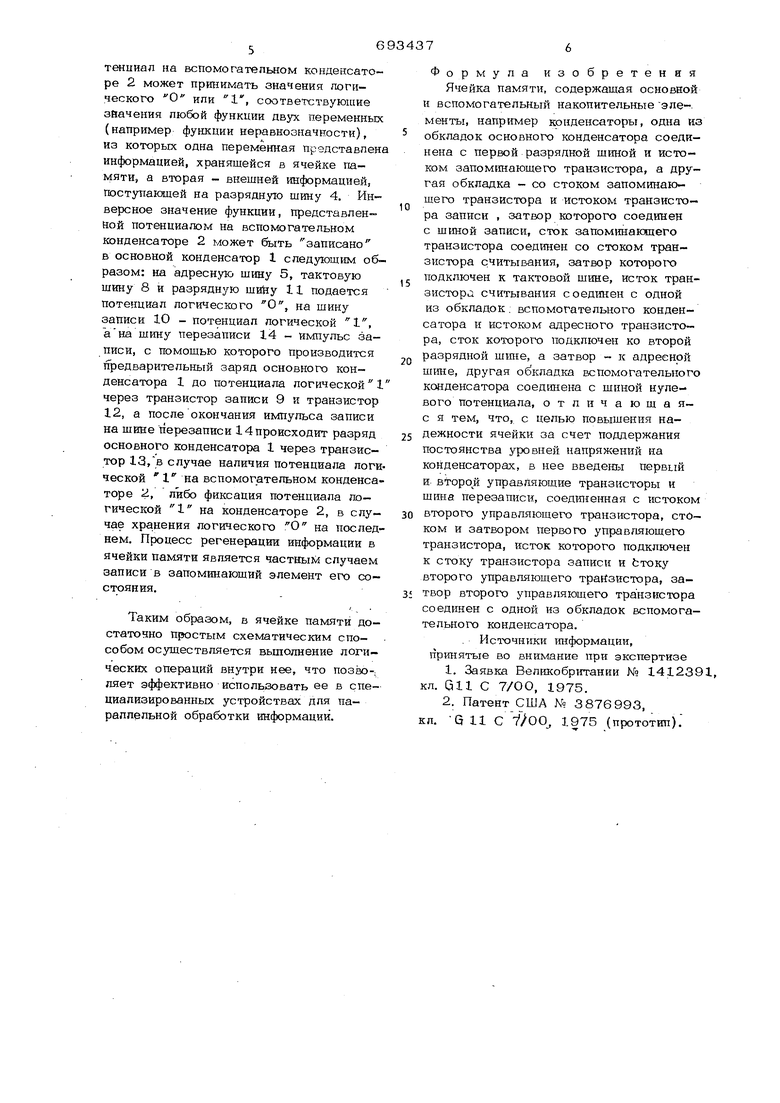

Наиболее близкой к предлагаемой по технической сушности является ячейка памяти, содержащая основной и вспо могательный накопительные элементы, например,- конденсаторы, одна из обкладок основного конденсатора соединена с первой разрядной щшой и истоком за0поминающего транзистбра, а другая обкладка - со стоком заноминактаего тран зйстора и истоком транзистора записи, затвор которого соединен с щ иной записи, сток запомйнйющего- транзистора сое5динен со стоком транзистора считывания, затвор которого подключен к тактовой шине, исток транзистора считывания соединен с одной из обкладок вспомогательного конденсатора и истоком ад0ресного транзистбра, сток которого подключен ко второй разрядной шине, а затвор - к адресной шше, другая о бкладка вс помогательно го конденсатора соединена с шиной нулевотх потенциала 2. Значение функции (потенциал вспомогательного конденсатора) может быть переписано на основной накопительный конденсатор. Перепись информации за счет перераспределения заряда связана с наличием остаточных потенциалов на конденсаторах, которые могут увеличить {уменьшить) уровни логических сигналов О (1) в зависимости от соотношения емкостей конденсаторов, что приведет к снижению информационной устойчивости запоминающего элемента и потребует значительного увеличения емкости вспомогательного накопительного конденсатора, что снижает технологическую надежность элемента. Цель изобретения - повышение надежности ячейки памяти за счет поддержания постоянства уровней напряжений на конденсаторах. .Поставленная цель достигается тем, что в ячейку памяти введены первый и второй управляклдие транзисторы и шина перезаписи, соединенная с,истоко второгчэ управляюшего транзистора, стоком и затвором первого управляющего транзистора, исток которого подключен к стоку транзистора записи и стоку вто рого управляющего транзистора, затвор второго управляюшего транзистора соединен с одной КЗ обкладок вспомогательного конденсатора. Сущность изобретения поясняется чертежом, на котором представлена электрическая схема ячейки памяти. Она содержит основной накопительный элемент, например конденсатор 1, .вспомогательный накопительный элемен например, конденсатор 2, адресный тра зистор 3, сток таторого соединен с раз рядной шиной 4, затвор - с адресной шиной 5, исток соединен с вспомогательным конденсатором 2, со стоком транзистора считывания 6, исток котор соединен со стоком запоминающего тра зистора 7, затвор - с тактовой шиной а затвор запоминающего транзистора 7 соединен с истоком транзистора записи 9 и основным конденсатором 1, ши ну записи 10, разрядную шину 11, первый управляюший транзистор 12, второ управляющий транзистор 13, затвор коTopotx соединен с вспомогательным кон денсатором 2, исток - с шиной перезаписи 14 и со стоком н затвором транзистора 12, исток которого соединен с стоками транзистора 13 и транзистора записи 9. Устройство работает следуюшим образом. В режиме записи информации код записываемого числа в виде уровня логическо.го О или подается на разрядную шину 4, а управляклцие потенциалы на адресной шине 5, шине записи Ю открывают адресный транзистор 3 и транзистор записи 9, потенциал разрядной шины 11 равен О. В Кюмент действия указанных сигналов на шину перезаписи 14 подается импульс, обеспечивающий предварительный разряд основного конденсатора 1 через открытые транзистор записи 9 и транзистор 12. После окончания импульса на шине перезаписи 14 на выходе инвертора, образованного транзисторами 12 и 13 и связанного с затвором запоминающего транзистора 7 и конденсатором 1 через открытый транзистор записи 9, устанавливается лот ический уровень, соответствующий инверсии,когда на разч рядной шине 4, то есть происходит запись информации в ячейку. Затем управляюший потенциал с шины записи 1О принимает значение логического О и и информация фиксируется на основном конденсаторе 1. . В режиме считывания информации подается импульс логической 1 на адресную шину 5 и тактовую шину 8, а также импульс опроса на разрядную шину 11. . В случае хранения на основном конденсаторе 1, на разрядной шине 4 появляется сигнал считывания в виде уровня логической 1, обусловленной гальванической связью разрядной . шины 11с разрядной шиной 4 через открытые транзисторы: адресный 3; запоминающий 7 и транзистор считывания 6. В случае хранения О, запоминающий транзистор 7 закрыт и разрядная шана 11 изолирована от разрядной шины 4, вследствие чего выходной сигнал соответствует считыванию логичес- кого О, С помощью подачи управлякших штенциалбв на адреснзгю шину 5, тактовую шину 8 и разрядную шину 11 по-

тенииал на вспомогательном конденсаторе 2 может принимать значения логического О или , соответствующие зйачения любой функции двух переменных (например функции неравнозначности), из которых одна переменная представлена информацией, хранящейся в ячейке памяти, а вторая - внешней информацией, поступаклдей на разрядную шину 4. Инверсное значение функции, представленйой потенциалом на вспомогательном конденсаторе 2 может быть записано в основной конденсатор 1 следующим образом: на. адресН5То шину 5, тактовую шину 8 и разрядную шийу 11 подается потенциал логического О, на шину записи 10 - потенциал логической 1, инашину перезаписи 14 - импульс за; писи, с помошью которого производится предварительный заряд основного конденсатора 1 до потенциала логической через транзистор записи 9 и транзистор 12, а после окончания импульса записи на шине перезаписи 14 происходит разряд основного конденсатора 1 через транзистор 13,в случае наличия потенциала логической 1 на вспомогательном конденсаторе 2, либо фиксация потенциала логической 1 на конденсаторе 2, в случае хранения логического О на последнем. Процесс регенерации информации в ячейки памяти является частньШ случаем записи в запоминаюший элемент его состояния.

Таким образом, е ячейке памяти достаточно простым схематическим способом осуществляется выполнение логических операций внутри нее,, что позво-: ляет эффективно использовать ее в специализированных устройствах для параллельной обработки информации.

Формула изобретения Ячейка памяти, содержашая основной и вспомогательный накопительные элё-. менты, например ж)нденсаторы, одна из обкладок основного конденсатора соединена с первой разрядной шиной и истоком запоминающего транзисто.ра, а другая обкладка - со стоком запоминаюшего транзистора и истоком транзистора записи , затвор которого соединен с шиной записи, сток запоминающего транзистора соединен со стоком транзистора считывания, затвор которого подключен к тактовой шине, исток тран5зистора считывания соединен с одной из обкладок, вспомогательного конденсатора и истоком адресного транзистора, сток которого подключен ко второй разрядной шине, а затвор- к адресной

0 шине, другая обкладка вспомогательного конденсатора соединена с шиной нулевого потенциала, отличающаяс я тем. Что,, с целыр повышения надежности ячейки за счет поддержания

5 постоянства уровней напряжений на конденсаторах, в нее введены первый и вТоро й управляюшие транзисторы и шина перезаписи, соединенная с истоком второго управляющего транзистора, стО0ком и затвором первого управляющего транзистора, исток которого подключен к стоку транзистора записи и Ьтоку второго управляющего трайзистора, затвор второго управляюшего тра нзистора

3i соединен с одной из обкладок вспомогател.ьного конденсатора.

;. Источники информации,

принятые во внимание при экспертизе

1,Заявка Великобритании № 1412391, кл. GH С 7/00, 1975.

кл. QllcV/OO 1975 (прототип).

,..:.-. V-

e-93W5V- -

5oJ-L

fffjf

64

Авторы

Даты

1979-10-25—Публикация

1977-03-09—Подача