I

Изобретение относится к измерительной текнике, а именно к измерительным устройствам ядерного приборостроения, и предназначено для кодирования временных интервалов наносекундного диапазона в ядернофизических экспериментах.

Известные преобразователи временной интервал - цифровой код,построенные по принципу прямого кодирования, обычно имеют минимальную ширину канала порядка 5 - 1О НС, ограниченную быстродействием триггеров адресного счетчика, построение которых с быстродействием 200 мГц и выше сопряжено с большими техническими трудностями, поэтому для обеспечения ширины канала меньше 5 не временные преобразователи строят по принципу линейного преобразования временной интервал - амплитуда Lll- Амп- ;литуда, несущая информацию о временном интервале, затем преобразуется ампли- тудно временным преобразователем в цифровой код. Частота импульсов кодирования в амплитудно-временном преобразова-

теле обычно составляет 5-10 мГц. Следовательно, еспн число каналов преобра- дования равно 100О, го время процесса преобразования, когда система не реагирует на поступающую на вход информацию, равно 20О-1ОО мкс. Такая величина мертвого времени является существенным недостатком линейных преобразователей временной интервал - амплитуда временной интервал.

10

Наиболее близким по технической сущности к предлагаемому является амплитудный преобразователь с нелинейным кодированием, служащий ОЛЯ непосредственного кодирования амплитуды в цифровой

15 код и состоящий из схемы запоминания входной амплитуды, линейного ключа (схемы ИЛИ), интегрального дискриминатора или компаратора, схемы выборки

25 амплитуды, схемы выборки остатка, генератора весового напряжения и схемы суммирования, причем цве последние схемы выполняют функцию устройства удвоения, а также адресного счетчика и счетчика числа циклов 21.

Однако этот преобразователь не может быть использован непосрецетвеино :ДЛя Кодирования временных интервалов. Его моишо применить для кодирования временных интервалов только в совокупности с линейным преобразователем временной интервал - амплитуда. В процессе преобразования возможно появление ошибки кодирования при измерении вхош; ых амплитуд, равных llo/2., где tt О, 1, 2, ...

Целью изобретения является расшире:ние функциональных возможностей и по- :вышение точности преобразования.

Под расширением функциональных возможностей подразумевается обеспечение непосредственного преобразования временных интервалов в цифровой код, исключение предварительного преобразования временной интервал - амплитуда; повышение точности происходит за счет устранения ошибок кодирования.

Поставленная цель достигается тем, что в преобразователь, содержащий элемент ИЛИ, выход которого соединен с первым входом компаратора, первый, второй и третий выходы которого соединены соответственно с входами адресного счетчика, счетчика циклов и с первым входом преобразователя временных интер валов, дополнительно введены три логических элемента задержки и элемент ИЛИ, причем третий выход компаратора через первый логический элемент задержки соединен со вторым входом преобразователя временных интервалов, выход которого через второй логический элемент задернски подключен к первом; входу дополнительного элемента ИЛИ, выход которого соединен со вторым входом компаратора, третий выход компаратора через третий логический элемент задержки соединен с первым входом элемента ИЛИ, вторые входы элементов ИЛИ подключены соответственно к шинам старт и стоп сигналов.

Компаратор может содержать последовательно соединенные блоки опорного времени интервала и временной селекции, причем вход блока опорного временного интервала является первым входом компаратора, вторым входом которого яЕ ляется один из входов блока временной селекА1ИИ, выходы которого являются выходами компаратора.

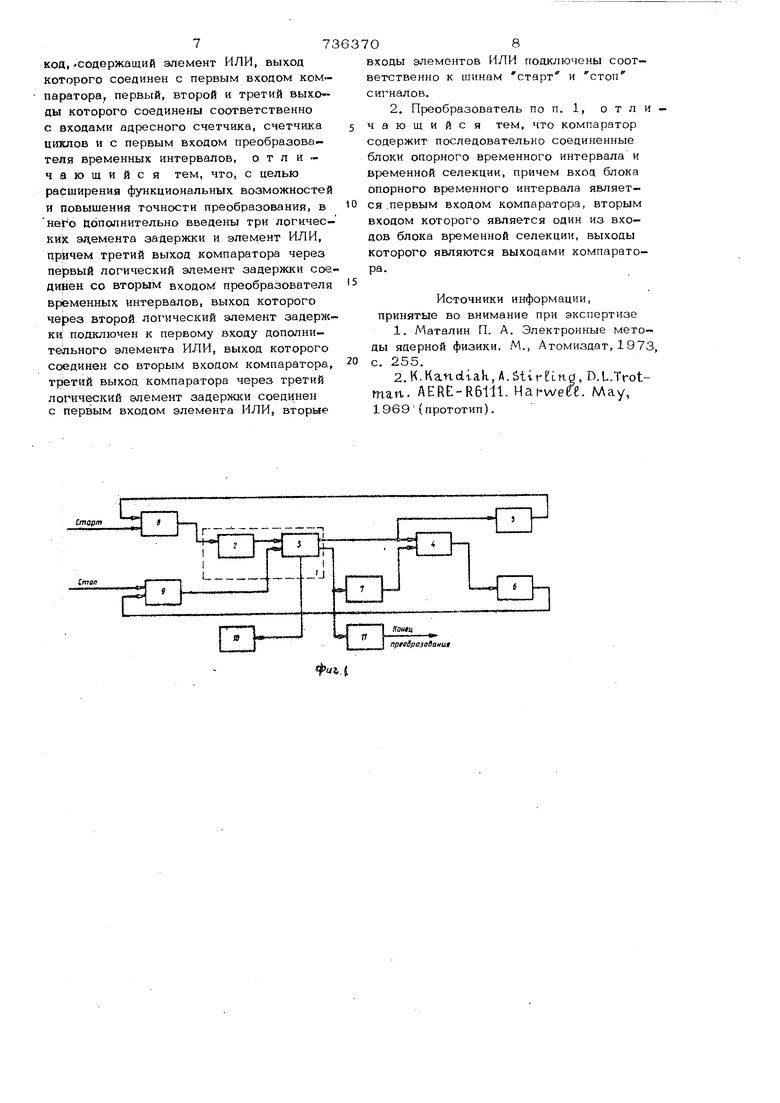

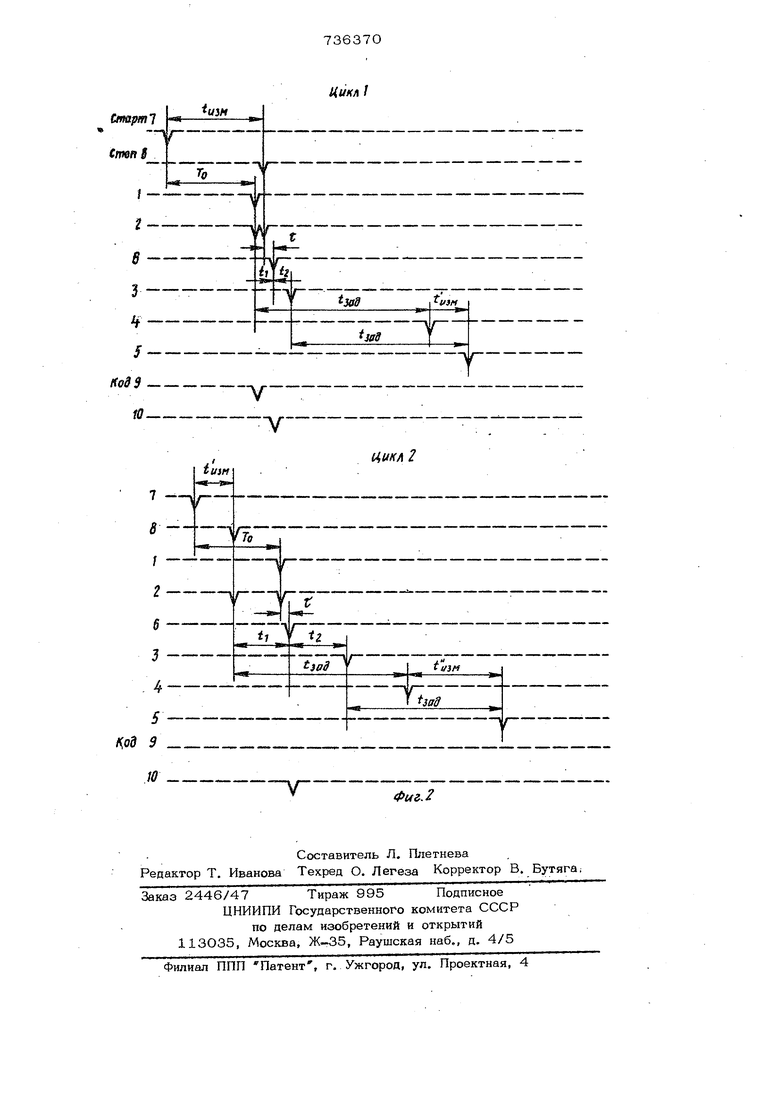

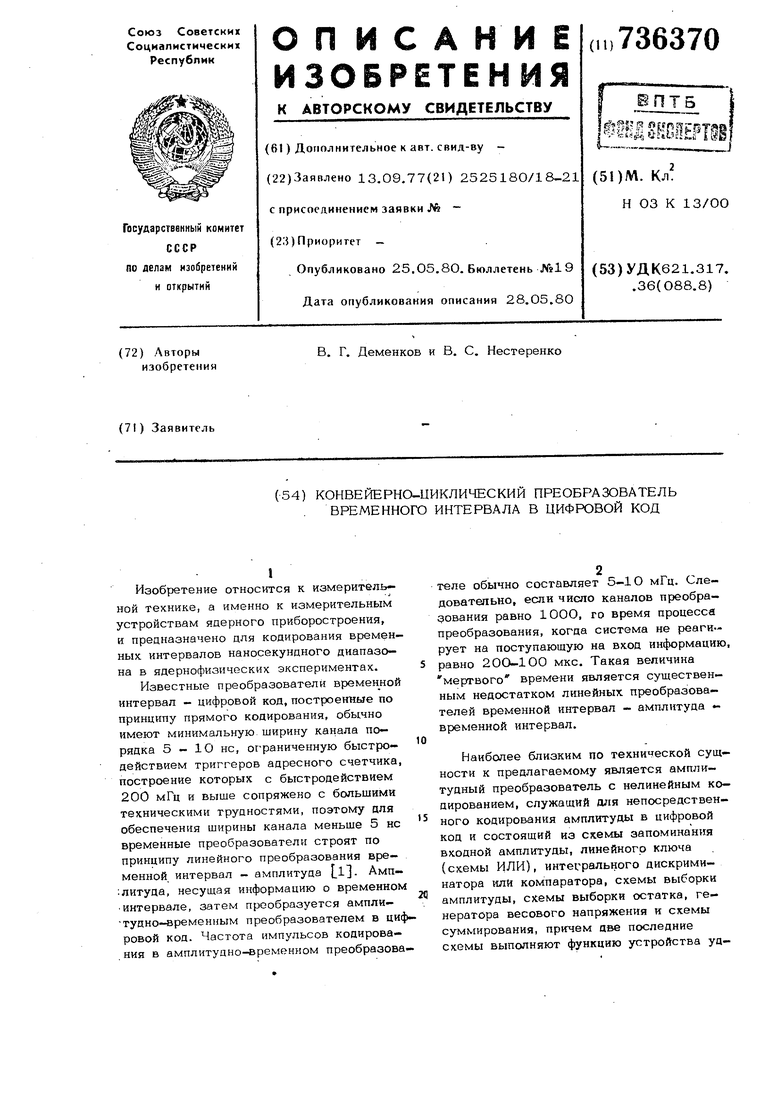

На фиг. 1 показана структурная схема конвейерно-чдиклического преобразователя временного интервала в цифровой код; на фиг, 2 - временные диаграммы, поясняющие его работу.

Преобразователь содержит компаратор 1, который состоит из блока 2 опорного временного интервала, блока 3 временной селекции, преобразователя 4 временных интервалов, трех логических элементов задержки 5, 6 и 7, двух логических элементов ИЛИ 8 и 9 адресного счетчика 1О и счетчика циклов 11.

Выход элемента 5 соединен с первым входом элемента ИЛИ 8, другой вход которого соединен с шиной старт сигнала. Выход элемента ИЛИ 8 соединен с входом блока 2, его выход соединен с одним из входов блока 3, один из выходов которого соединен с входом элемента задержки 5 и одним из входов преобразователя 4. Выход последнего соединен с входом элемента задержки 6. Его выход соединен с первым входом дополнительного логического элемента ИЛИ 9 другой вход которого соединен с шиной стоп сигнала. Выход логического элемента ИЛИ 9 соединен с другим входом .блока 3, второй выход которого соединен с входом счетчика циклов 11 и входом элемента задержки 7. Его выход содинен со вторым входом преобразователя 4, а первый выход блока - с входом адресного счетчика 10.

Блок 2 опорного временного интервала выполняет функцию фиксированной задержки на величину TQ. Блок 3 определяет временную последовательность поступления сигналов по его входам. .Причем на выходе, соединенном с элементом 5, всегда появится первый из поступивших на входы блока 3 сигналов. На выходе блока 3, соединенном с элементом 7, всегда будет второй из поступив- ших на входы блока 3 сигналов. Блок временной селекции не меняет временных соотношений между сигналами, поступившими на его входы, а только коммутирует их по входам в зависимости от порядка их поступления. На выходе блока 3, который соединен с входом адресного счетчика 10, сигнал появится только в случае, если сигнал на входе блока 3, который соединен с блоком 2 опорного временного интервала, опережает сигнал по другому входу. Если сигнал на входе блока 3, который соединен с блоком 2, появляется позже сигнала по другому 5 иходу, го сигнал на первом выходе блока 3 отсутствует. Преобразователь 4 временных ингервалов обеспечивает нормальное-его функ ционирование в случае малых задержек между выходными сигналами блока 3. Элементы 5 и 6 служат для выбора вре менных соотношений в пределах одного цикла преобразования, т. е. обеспечиваю четкое разделение циклов преобразования и тем самым исключают искажение временной информации в преобразователе 4. Адресный счетчик 10 регистрирует код каждого цикла преобразования. Число циклов, преобразования, которое постоян- но в пределах каждого измерения, задается счетчиком циклов 11. Преобразователь работает следующим образом. Измеряемый временной интервал заключенный между сигналами старт и стоп, поступает на компаратор 1, состоящий из блоков 2 и 3, где сравнивает ся с Т . Если1; 5; Т, то триггер адресного счетчика 1О, соответствующий старшему разряду, устанавливается в единичное состояние. К временному инте валу {tusM- TO), получаемому на выходе компаратора 1, т. е. блока 3, добавляется небольшой временной интервал С логическим элементом задержки 7. Полученный временной интервал ( -TO + t ) удваивается- в преобразователе 4, т. е. получают временной интервал, равный 2 ( Тр +Т). Сигнал, соот ветствующий концу временного интервала, получаемому на выходе компаратора, поступает на счетчик циклов 11. Так ка величины задержки логических элементов задержки 5 и 6 выбираются равными и из условия 1зАА о временной интервал между сигналами на выходах элементов 5 и 6 равен 2 (1ц,- TQ +С.). Этот временной интервал снова сравнивается с TO временным компаратором. Если 2 (iMiM-T o +Т) Тр , то следующий триггер адресного счетчика 1О остается в нулевом состоянии. К временному интервалу на выходе компаратора, , равному (ЗТц t), добавляется временной интервал t , и полученный временной интервал (ЗТ - 2t«sM-C) удваивается, а на счетчик циклов 11 поступает сигнал, соответствующий концу временного интервала на выходе компаратора 1. Удвоенный временной интервал, равный (6T(j - 41н5м- 21), снова поступает через элементы 5 и 6 на вре- 706 менной компаратор, и циклы преобразования будут продолжены. На временных диаграммах преобразования, представленных на фиг. 2, -ПО оси ординат нанесены номера блоков, по оси абсцисс - текущее время. Вследствие того, что в конвейерно- циклическом преобразователе временного интервала в цифровой код компаратор, состоящий из блоков опорного временного интервала и временной селекции, не меняет временных соотношений между входными сигналами, а только коммутирует их в зависимости от порядка их по- ступления, на вход преобразователя временного интервала поступает временной интервал, равный модулю разнвды (/twiM- TO/ ), а информация о величине входного временного интервала представляется в коде Грея. Это обеспечивает устранение ошибок кодирования входных временных интервалов, равных То/2 , где П- О, 1, 2, ... Предлагаемое устройство обеспечивает непосредственное кодирование бремен- ных интервалов в цифровой код, исключает предварительное преобразование временной -интервал - амплитуда и устраняет ошибки кодирования временных интервалов tex - TO /2 . В результате улучшается точность преобразования, повышаются интегральная и дифференциальная линейности и надежность, что расширяет область практического использования преобразователя для кодирования временных интервалов в различных областях науки и техники, а также исключается необходимость разработки целого ряда преобразователей типа временной интервал - цифровой код для кодирования временных интервалов наносекундного диапазона. Замена предлагаемым преобразователем временных преобразователей линейного кодирования временной интервал - амплитуда позволит уменьшить время проведения физических экспериментов и повысить эффективность использования дорогостоящего оборудования, так как мертвое время нелинейного кодирования временных интервалов предлагаемого преобразователя почти на порядок меньше мертвого времени преобразователей линейного кодирования временных интервалов. Формула идоб.ретения 1. Конвейерно-ч:1Иклический преобра- зователь временного интервала в цифровой

код,-содержащий элемент ИЛИ, выход которого соединен с первым входом компаратора, первый, второй и третий выходы которого соединены соответственно с входами адресного счетчика, счетчик:а циклов и с первым входом преобразователя временных интервалов, отличающийся тем, что, с целью расширения функциональных возможностей и Повышения точности преобразования, в не1го Дополнительно введены три логический эдемента задержки и элемент ИЛИ, причем третий выход компаратора через первый логический элемент задержки соединен со вторым входом преобразователя временных интервалов, выход которого через второй логический элемент задерж- ки подключен к первому входу дополнительного элемента ИЛИ, выход которого соединен со вторым входом компаратсра, третий выход компаратора через третий логический элемент задержки соединен с первым входом элемента ИЛИ, вторые

ВХОДЫ элементов ИЛИ подключены соответственно к шпнам старт и стоп сигналов.

2. Преобразователь по п. 1, о т л и чающийся тем, что компаратор содержит последовательно соединенные блоки опорного временного интервала и временной селекции, причем вход блока опорного временного интервала является .первым входом компаратора, вторым входом которого является один из входов блока временной селекции, выходы которого являются выходами компаратора.

Источники информации, принятые во внимание при экспертизе

1. Маталин П. А. Электронные мето ды ядерной физики, М., Атомиздат, 1973 с. 255.

2.K.Kandtak,A.Sti.f ELng, D.L.Trotmatt. AERE-RBIll. Mar-weft. May,

1 969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерно-циклический временной интерполятор | 1980 |

|

SU951691A1 |

| Измеритель временных интервалов | 1982 |

|

SU1052097A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU894860A1 |

| СПОСОБ ИЗМЕРЕНИЯ ФИЗИЧЕСКОГО ПАРАМЕТРА В СКВАЖИНЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013534C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| Измеритель временных интервалов | 1981 |

|

SU981925A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2496228C1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

Авторы

Даты

1980-05-25—Публикация

1977-09-13—Подача