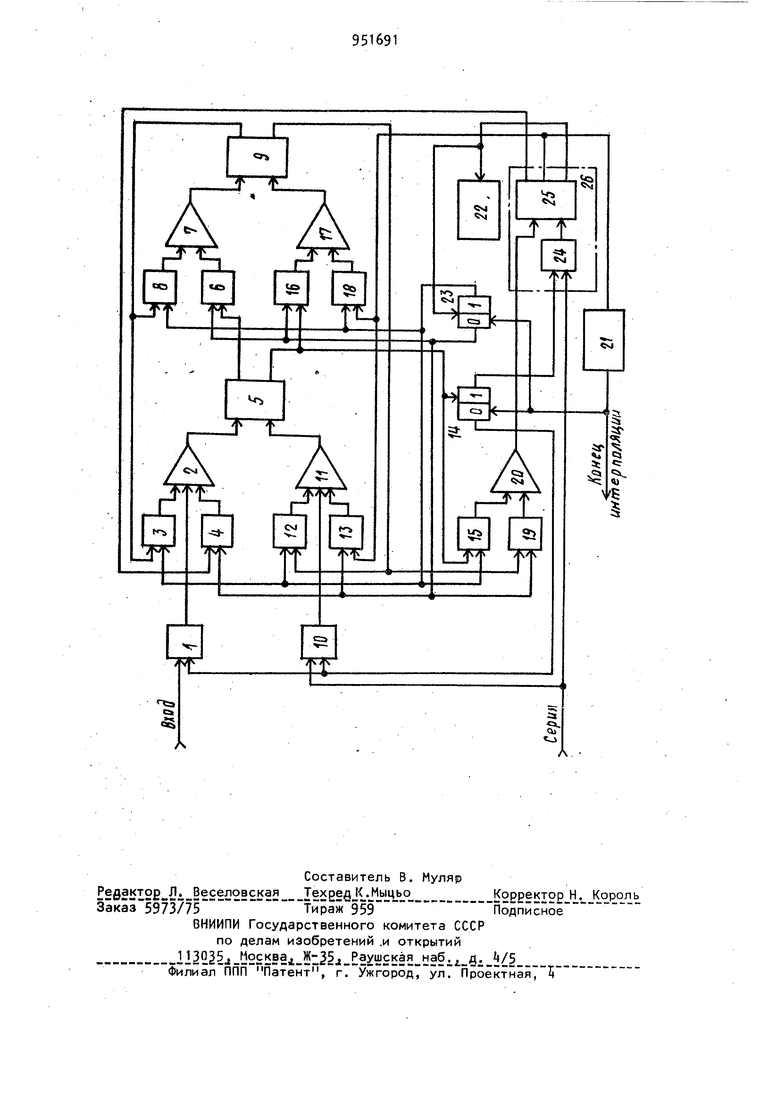

(S) КОНВЕЙЕРНО-ЦИКЛИЧЕСКИЙ ВРЕМЕННОЙ ИНТЕРПОЛЯТОР Изобретение относится к измеритель ной технике, а именно к измерительным устройствам ядерного приборостроения и предназначено для повышения точности измерения временных интервалов. Уменьшение ширины канала при заданной опорной серии в пределах ее периода обеспечивается применением ин терполяционных методов. В качестве интерполяторов, как правило, используют различные комбинации линий задержки и схем совпадений, к параметрам которых предъявляются повышенные требования ( однородность и согласованность линий задержки, чувствительность схем совпадений, стабильность их разрешающего времени и т.д.), чтобы обеспечить равномерность ширины канала, т.е. дифференциальную линейность, как между каналами в пределах одного периода опорной серии, так и между группами каналов в пределах последующих периодов опорной серии 1, Недостатком таких интерполяторов является сложность изменения ширины временных интервалов, так как она задается либр длиной линии задержки, либо разницей между двумя линиями задержки . Наиболее близким по технической сущности к предложенному устройству является конвейерно-циклический преобразователь временного интервала в цифровой код, служащий для непосредственного кодирования временного интервала, который содержит компаратор, состоящий из блока временного интервала и блока временной селекции, преобразователя временных интервалов, трех логических элементов задержки, двух логических элементов ИЛИ, адресного счетчика и счетчика циклов . Данный преобразователь можно использовать непосредственно для интерполяции в пределах периода опорной серии только в том случае, если задержка в блоке опорного временного интервала равна периоду опорной серии. Это условие, как и в случае построения интерполяторов на основе линий задержки и схем совпадений, явля ется существенным недостатком, исключающим возможность обеспечить эквидистантную интерполяцию и однозрачность кодирования временного интерва ла, заключенного между входным сиг налом и последующим импульсом опорно серии, при изменении частоты последней. Эквидистантная интерполяция и однозначн сть кодирования являются необходимым условием достижения хорошей равномерности ширины канала, т.е. дифференциальной линейности в пределах периода опорной серии. Цель изобретения - расширение функциональных возможностей устройства, а именно обеспечение эквидистантной интерполяции и однозначности кодирования временного интервала, заключенного между входным сигналом и последующим импульсом опорной серии, при перестройке частоты последней. Поставленная цель достигается тем что в конвейерно-циклический временной интерполятор, содержащий два элемента ИЛИ, преобразователь временного интервала, временной компаратор, счет чик циклов и адресный счетчик, дополнительно введены преобразователь временного интервала, два триггера, три элемента ИЛИ и тринадцать элементов И причем выход первого элемента И соединен с первым входом первого основного элемента ИЛИ, второй и третий входы которого связаны соответственно с выходом второго и третьего элементов И, а выход первого основного элемента ИЛИ соединен с первым входом основного преобразователя временного интервала, первый выход которого подключен к первому входу четвертого эле мента И, выход которого соединен с первым входом второго основного элемента ИЛИ, второй вход которого связан с выходом пятого элемента И, а выход второго основного элемента ИЛИ соединен с первым входом дополнительного преобразователя временного интервала, первый выход которого подклю чен к первым входам второго и пятого элементов И, при этом выход шестого элемента И соединен с первым входом первого дополнительного элемента ИЛИ второй и третий входы которого связаны соответственно с выходами седьмого и восьмого элементов И, а выход первого дополнительного элемента ИЛИ соединен с вторым входом основного преобразователя временного интервала, второй выход которого подключен к первому установочному входу первого триггера и к первым входам девятого и десятого элементов И, выход последнего соединен с первым входом второго дополнительного элемента ИЛИ, второй вход которого связан с выходом одиннацатого элемента И, а выход второго дополнительного элемента.ИЛИ соединен с вторым входом дополнительного преобразователя временного интервала, второй выход которого подключен к первым входам седьмого и двенадцатого элементов И, выход последнего соединен с первым входом третьего дополнительного элемента ИЛИ, второй вход которого связан с выходом девятого элемента И, а выход третьего дополнительного элемента ИЛИ соединен с первым входом временного компаратора, второй вход которого соединен с первым выходом первого триггера, а третий вход компаратора подключен к первому входу шестого элемента И, причем первый выход компаратора соединен с первым входом третьего элемента И, второй выход компаратора соединен с входом счетчика циклов и с первыми входами восьмог о и одиннадцатого элементов И, а третий выход компаратора связан с входом адресного счетчика и счетным входом второго триггера, первый выход которого соединен с вторыми входами второго, пятого, седьмого, девятого и одиннадцатого элементов И, а второй выход второго триггера соединен с вторыми входами третьего, четвертого, восьмого, десятого и двенадцатого элементов И, выход счетчика циклов подключен к установочному входу второго триггера и к второму установочному входу первого триггера, второй выход которого соединен с пepвы л и вторым входом соответственно первого и шестого элементов И. Такое схемное решение позволяет обеспечить эквидистантную интерполяцию и однозначность кодирования временного интервала, заключенного между входным сигналом и последующим импульсом опорной серии, при перестройке частоты последней, так как величина временного интервала находится путем сравнения во временном компараторе удвоенного временного интервала 2t с периодом опорной серии Т, длительность которого может изменяться в зависимости от требуемой точности или параметров используемого генератора опорной серии. В результате срав нения получают разницу (2t-Tn), которая опять удваивается и снова сравнивается с Tjj. В процессе сравнения в каждом цикле интерполяции определяется знак разницы (Zt-T ) который является кодом Грея и однозначно определяет величину временного интервала Удвоение временного интервала осуществляется двумя преобразователями временных интервалов с коэффициентом преобразования, равным двум, причем если один осуществляет привязку временного интервала к началу периода опорной серии, то другой преобразователь удваивает его, и наоборот. В процессе интерполяции преобразователи могут обмениваться этими функциями. На чертеже представлена блок-схема конвейерно-циклического временного интерполятора. Конвейерно-циклический временной интерполятор содержит первый элемент И 1 , первый основной элемент ИЛИ 2 второй элемент И 3, третий элемент И основной преобразователь временного интервала 5, четвертый элемент И 6, второй основной элемент ИЛИ 7, пятый элемент И 8, дополнительный преобразователь временного интервала 9 шестой элемент И 10, первый дополнительный элемент ИЛИ 11, седьмой элемент И 12, восьмой элемент И 13, Р вый триггер k, девятый элемент И 15. десятый элемент И 1б, второй дополнительный элемент ИЛИ 17, одиннадцатый элемент И 18, двенадцатый элемент И 19 третий-дополнительный элемент ИЛИ 20, -. „ 1 счетчик циклов 21, адресный счетчик 2 второй триггер 23 тринадцатый элемент И 2k, блок временной селекции 25 временный компаратор 26, который состоит из элемента 2А и блока 25. Преобразователь временного интервала (ПВИ) 5 9 удваивает временной интервал, заключенный между сигналами, поступившими на его входы. Положение второго выходного сигнала ПВИ соответствует концу удвоенного временного интервала, а положение первого выходного сигнала ПВИ соответствует концу аходного временного интервала. Сигналы на выходе ПВИ появляют ся в случае, если сигнал по первому входу ПВИ опережает сигнал по второму входу ПВИ Элементы ИЗ, и ИЛИ 2 служат дли отбора одного сигнала на первый вход ПВИ 5 из двух поступивших сигналов: сигнала с первого выхода ПВИ 9 и сигнала с первого выхода блока временной селекции ( БВС 25. Аналогично логические элементы И 6 и 8, ИЛИ 7 осуществляют отбор одного сигнала на первый вход другого ПВИ 9 из двух сигналов: сигнала с первого выхо- ; да ПВИ 5 и сигнала с первого выхода ВВС 25. Элементы И 12 и 13, ИЛИ 11 отбирают Один сигнал на второй вход ПВИ 5 из двух поступивших сигналов: : сигнала с второго выхода ПВИ 9 и сигнала с второго выхода БВС 25. Аналогично элементы И 1( и 18 и ИЛИ 17 служат для отбора одного сигнала на второй вход ПВИ 9 из двух поступивших сигналов: сигнала с второго выхода ПВИ 5 и сигнала с второго выхода БВС 25. Выбор одного из сигналов на каждом входе каждого ПВИ определяется состоянием второго триггера 23. Кроме того, состояние второго триггера 23 и совокупность элементов И 1$ и 19 и ИЛИ 20 определяют порядок поЬтупления сигналов с второго выхода обоих ПВИ 5 и 9 на один из входов БВС 25, на другой вход которого с элементов И поступают импульсы опорной серии. Если второй триггер находится в состоянии, указанном на чертеже, то на первый и второй входы ПВИ 5 сигналы поступают соответственно с первого и второго выходов БВС 25, на входы другого ПВИ 9 сигналы поступают с первого и второго выходов ПВИ 5, а на вход БВС 25 посту, „ви п пают сигналы с второго выхода ПВИ 9. Первый триггер И служит для управления входами временного интерполятора {.элементы И 1, 10 и 2), Состояние триггера, показанное на черте «е, блокирует элементы И 2 и обеспечивает поступление сигналов Вход и Серия соответственно через логические элементы И 1 и 10 на вхя . ды ПВИ 5« Сигнал, поступивший по установочному входу триггера, соединенному с вторым выходом ПВИ 5, опрокидывает триггер Il, блокируя тем самым элементы И 1 и 10, и обеспечивает поступление импульсов серии через элемент И 24 на другой вход ВВС 25. ВВС 25 опрхеделяет временную последовательность поступления сигналов по его входам, причем на выходе, соединенном с входами элементов И k и 8, всегда появляется первый из поступивших на вход ВВС 25 сигналов. Н выходе ВВС 25, соединенном с входами элементов И 13 и 18 и счетчика ци лов 21, всегда появляется второй из .поступивших на вход ВВС 25 сигналов, ВВС 25 не меняет временных соотношений между сигналами, поступившими на его входы, а только коммутирует их по выходам в зависимости от поряд ка их поступления. На выходе 25, который соединен с адресный счетчиком 22 и счетным входом второго триг гера 23, сигнал .появляется только в случае, еслисигнал на выходе ВВС 25 который соединен с выходом элемента И 2, опережает сигнал, поступивший на вход ВВС 25, соединеннь|й с эл ментом ИЛИ 20. Если временная последовательность входных сигналов обрат ная, т.е. сигнал, поступивший на вход БВС 25, соединенный с элементом ИЛИ 20, опережает сигнал, поступивший по другому входу ВВС 25, соединенному с элементом И 2, то сигнал на третьем выходе ВВС 25, который соединен с адресным счетчиком и счетным входом триггера 23, отсутствует СчетчиКциклов 21 задает чис ло циклов интерполяций, которое постоянно при заданной точности интер поляции. За один цикл интерполяции осуществляется с точностью до полови .ны периода опорной серии. За два цикла интерполяции осуществляется с точностью до четверти периода, а за три цикла - с точностью до одной вос мой периода опорной серии и т.д. Адресный счетчик 22 регистрирует код каждого цикла интерполяции. I Временной интерполятор работает следующим образом. Измеряемый временной интервал t, заключенный между входным сигналом, поступившим с выхода элементов И 1 и ИЛИ 2, и последующим импульсом опо ной серии, поступившим с выхода элементов И 10 и ИЛИ 11, удваивается ПВИ 5. Сигнал с первого выхода ПВИ 5 соответствующий концу измеряемого вр менного интервала, через элемент И 6 и ИЛИ 7 поступает на первый вход дру ТОГО ПВИ 9. Сигнал с второго выхода ПВИ 5, соответствующий концу удвоенного временного интервала, через элементы И 16 и И 17 поступает на второй вход другого ПВИ 9. Этот же сигнал поступает на один из установочный входов первого триггера 1 и опрокидывает его, обеспечивая тем самым поступление импульсов.серии на вход ВВС 25 и блокировку элементов И 1 и 10. Сигнал, поступивший с второго выхода ПВИ 5 на вход элемента И 15, не проходит через него, так как уровень с второго триггера 23 блокирует элемент И 15. Временной интервал t, заключенный между выходными сигналами ПВИ 5 равен входному измеряемому временному интервалу, т.е. t t и начало этого временного интервала t четко привязано к последующему импульсу опорной серии. Временной интервал t удваивается в ПВИ 9, и сигнал с второго выхода ПВИ 9 соответствующий концу удвоенного временного интервала 2t , поступает через элементы И 19 и ИЛИ 20 на временной компаратор, который сравнивает длительность удвоенного временного интервала 2t с длительностью периода опорной серии Т, Если 2t 7 TQ, то на первом выходе ВВС 25 первым появляется импульс серии, а на втором выходе ВВС 25 вторым появляется сигнал конца удвоенного временного интервала 2t. В этом случае на третьем выходе ВВС 25 появляется сигнал, который поступает на вход адресного счетчика 22 и счетный вход второго триггера 23 и изменяет его состояние. Сигнал с первого выхода БВС 25 через элементы И 4 и ИЛИ 2 поступает на первый вход ПВИ 5 на второй вход которого через элементы И12 и ИЛИ 11 поступает сигнал удвоенного временного интервала : 2t с второго выхода ПВИ 9. Этот сигнал на первый вход ПВИ 9 не воздействует, так как элемент И 6 блокирован уровнем второго триггера 23- Второй сигнал с второго выхода ВВС 25 на ПВИ 5 не воздействует,, так как элемент И 13 блокирован уровнем с второго триггера 23, а ПВИ 9 не реагирует на этот сигнал, так как ранее не поступил сигнал по первому входу ПВИ 9. Сигнал с второго выхода БВС 25, поступивший на вход счетчика циклов 21, Фиксирует окончание первого цикла ин99терполяции. Временной интервал на вхо де ПВИ 5равен (2t-Тд), и начало это го временного интервала привязано к импульсу серии. ПВИ 5 удваивает этот временный интервал, и сигнал с второго выхода ПВИ 5, соответствующий концу удвоенного временного интервала 2(2t-TO), через элементы.И 15 и ИЛИ 20 поступает на временной компаратор 26, который сравнивает длительность удвоенного временного интервала 2(2t-To) с очередным периодом опорной серии TO. Если 2(2t-TQ) Тд, то на первом выходе ВВС 25 первым появляется CHI- нал конца временного интервала 2(2t -TQ), а на втором выходе ВВС 25 вторым появляется импульс серии. В этом случае на третьем выходе ВВС 25 сигнал отсутствует,и второй триггер 23 остается в том же состоянии, как после первого цикла интерполяции. Сигнал с первого выхода ВВС 25 на первый вход ПВИ Э не поступает, так как элемент И k блокирован уровнем с второго триггера-23, а через элементы И 8 и ИЛИ 7 он проходит на первый вход ПВИ 5, на второй вход которого через элементы И 18 и ИЛИ 17 поступает сигнал с второго выхода ВВС 25. Этот же сигнал, поступивший на вход сметчика циклов 21, фиксирует окончание второго цикла интерполяции. Таким образом, длительность временного интервала, заключенного между входными сигналами ПВИ 9 равна 2(2t -То)Т0 и удваивается с помощью ПВИ 9, т.е. равна (2t -Tp). Временной интервал Х заключенный между выходными сигналами ПВИ 9 ра вен входному временному интервалу, т.е. ly (2t-Tp) -t,.,H начало этого временного интервала Т четко привязано к очередному импульсу серии Сигнал, соответствующий началу временного интервала Т , с первого выхода ПВИ 9 через элементы И 3 и ИЛИ 2 поступает на первый вход ПВИ 3 на второй вход которого через элементы И 12 и ИЛИ 11 поступает сигнал с второго выхода ПВИ 9. Сигнал с второго выхода ПВИ 9 на вход временного компаратора не поступает, так как эле мент И 19 блокирован уровнем с второго триггера 23. В этом случае ПВИ 9 выполняет функцию перевода временного интервала, заключенного между входными сигналами ПВИ 9, в очередной пе1риод опорной серии и привязки его к импульсу начала этого периода. Временной интервал (21 -Tg) Тр удваивается. ПВИ 5, и сигнал с второ- го .выхода ПВИ 5. соответствующий удвоенному временному интервалу (2t -T,),-TO, через элементы И 15.и ИЛИ 20 поступает на временной компаратор 2б, который сравнивает длительность удвоенного временного интервала (2t-TO) длительностью опорной серии Тр. Если 2 тг 7 TO , то на первом выходе ВВС 25 первым появляется импульс серии, а на втором выходе ВВС 25 вторым появляется сигнал конца удвоенного временного интервала 2t. В этом случае на третьей выходе ВВС 25 появляется сигнал, который поступает Ча вход адресного счетчика 22 и счетный вход второго триггера и изменяет его состояние. Сигнал с первого выхода ВВС 25 через элементы И 8 и ИЛИ 7 поступает на первый вход ПВИ 9 на второй вход которого через элементы И 16 и ИЛИ 17 поступает сигнал конца удвоенного временного интервала 2 С с второго выхода ПВИ 5. Этот сигнал на первый вход ПВИ 5 не воздей- ствует, так как элемент И 3 блокирован уровнем второго триггера 23. Второй сигнал с второго выхода ВВС 25 на ПВИ 9 не воздействует, так как элемент И 18 блокирован уровнем с второго триггера 23, а ПВИ 5 не реагирует на этот сигнал, так как ранее не поступил сигнал по первому входу ПВИ 5. Сигнал с второго выхода ВВС 25, поступивший на вход счетчика циклов 21, фиксирует окончание третьего цикла интерполяции. Временной интервал на входе ПВИ 9 равен (2г-То) 2i:2(2t-To) , и начало этого временного интервала привязано к импульсу серии. ПВИ Э УДВвивает этот временной интервал,и сигнал с второго выхода ПВИ 3, соответствующий концу удвоенного временного интервала 2(), через элементы И 19 и ИЛИ 20 поступает на временной компаратор, который сравнивает длительность удвоенного временного интервала 2(2Т/-То) с очередным периодом опорной серии TOТак как 2(2tr-To) Т, то на первом выходе ВВС 25 первым появляется сигнал конца временного и тepвaлa 2(2f-To), а на втором выходе ВВС 25 n9 рторый появляется импульс серии, В этом случае на третьем выходе ВВС 25 сирнал отсутствует, и второй триг гер 23|Остается в том же состоянии, что и после предыдущего цикла интерполяции. Сигнал с первого выхода ВВС 25 на первый вход ПВИ 9 не поступает, так как элемент И 8 блоки рован уровнем с второго триггера 23, s через элементы И и ИЛИ 2 он проходит на первый вход ПВИ 5, на второй вход которого через элементы И 13 и ИЛИ 1 поступает сигнал с второго выхода БЕС 25. Этот же сигнал, поступивший на вход счетчика циклов 21, фиксирует окончание четвертого цикла интерполяции и т.д. В первом цикле интерполяции один ПВИ 5, осуществляя.-удвоение поступившего временного-интервала, выполняет функцию перевода его в очередной период опорной серии и четкой привязки поступившего временного интервала к импульсу начала этого периода опорной серии, а другой ПВИ 9, осуществляя удвоение привязанного поступившего временного интервала, выдает его на сравнение с периодом опорной серии Т во временном компараторе. Если в результате сравнения оказывается, что удвоенный временной интервал больше периода опорной серии TQ, то следующий цикл интерполяции идет сразу путем удвоения в ПВИ 5 разницы удвоенного временного интервала и периода опорной серии Т и вы- даЧи этой удвоенной разницы опять на сравнение с последующим периодом опор TQ во временном компаратоНОИ серии ре и т.д. Если в результате сравнения окачто удвоенный временной зывается, интервал меньше периода опорной серии Tj, , то следующий цикл интерполяции осуществляется аналогично первому циклу интерполяции и т.д. Так как временной )aTOp 2б состоит из элемента И 2 и БВС 25 и осуществляет сравнение удвоенных временных интервалов с ПВИ 5 и 9 с периодом опорной серии Т0 и БВС 25 не меняет временных соотношений между поступившими на вход БВС 25 сигналами, а только коммутирует их на соответствующие выходы БВС 25 в зависимости от порядка их поступления, то на входы ПВИ 5 и 9 Поступают временные интервалы, равные модулю разницы /2t-To./, 1 а информация о величине удвоенного временного интервала представляется в коде Грея. Использование во временном компарат Оре в качестве опорного временного интервала периода опорной серии, анапогичного преобразователя временного интервала с коэффициентом преобразования, равным двум, двух триггеров, трех логическим элементов ИЛИ и тринадцати логических элементов И, а также новых связей между узлами выгодно отличает предлагаемый конвейерно-циклический временной интерполятор от известного устройства, так как обеспечивается эквидистантная интерполяция и однозначность кодирования временного интервала, заклюг чанного между входным сигналом и последующим импульсом опорной серии, при перестройке частоты последней, что расширяет функциональные возможности устройства. Вместе с тем достигается уменьшение общего времени преобразования, что позволяет более эффективно использовать оборудование в различных ядернофизических экспериментах. Формула изобретения Конвейерно-циклический временной интерполятор, содержащий два логических элемента ИЛИ, преобразователь временного интервала, временной компаратор, счетчик циклов и адресный счетчик, отличающийся тем, что, с целью расширения функциональных возможностей устройства, в него дополнительно введенв преобразователь временного интервала, три эле-, мента ИЛИ, два триггера и тринадцать элементов И, выход первого из которых соединен с первым входом первого основного элемента ИЛИ, второй и третий входы которого связаны соответственно с выходом второго и третьего элементов И, а выход первого основного элемента ИЛИ соединен с первым входом основного преобразователя временного интервала, первый выход которого подключен к первому входу четвертого элемента И, выход которого соединен с первым входом второго основного элемента ИЛИ, второй вход которого связан с выходом пятого элемента И, а выход второго основного элемента ИЛИ соединен с первым входом дополнительного преобразователя временного интервала, первый выход которого подключен к первым входам втс рого и пятого элементов И, при этом выход шестого элемента И соединен с первым входом первого допЪлнительног элемента ИЛИ, второй и третий входы которого связаны соответственно с вы ходами седьмого и восьмого элементов И, а выход первого дополнительно го элемента ИЛИ соединен с вторым входом основного преобразователя вре 1. менного интервала, второй выход которого подключен к первому устано вочному входу первого триггера и к первым входам девятого и десятого элементов И, выход последнего соединен с первым входом второго дополнительного элемента ИЛИ, второй вход к торого связан с выходом одиннадцатог элемента И, а выход второго дополни тельного элемента ИЛИ соединен с вто рым входом дополнительного преобразо вателя временного интервала, второй выход которого подключен к первым входам седьмого и двенадцатого элементов И, выход последнего соединен с первым входом третьего дополнитель ного элемента ИЛИ, второй вход которого связан с выходом девятого элемента И, а выход третьего дополнительного элемента ИЛИ соединен с пер вым входом временного компаратора, второй вход которого соединен с первым входом первого триггера, в третий вход компаратора подключен к первому входу шестого элемента И, причем первый выход компаратора соединен с первым входом третьего элемента И, второй выход компаратора соединен с входом счетчика циклов и с первыми входами восьмого и одиннадцатого элвментов И, а третий выход компаратора связан с входом адресного счетчика и счетным входом второго триггера, первый выход которого соединен с вторыми входами второго, пятого, седьмого, девятого и одиннадцатого элементов И, а второй выхЬд второго триггера соединен с вторыми входами третьего, четвертого, восьмого, десятого и двенадцатого элементов,И, выход счетчика циклов подключен к установочному входу второго триггера и к второму установочному входу первого триггера, второй выход которого соединен с первым и вторым входом соответственно первого и шестого элементов И. Источники информации, принятые во внимание при экспертизе 1.Электронные методы ядерной физики. Под ред. проф. Л.А. Маталииа, Атомиздат, 1973, с. 2бЗ. 2.Авторское свидетельство СССР № 730370, кл. Н 03 К 13/00, 1980.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерно-циклический преобразователь временного интервала в цифровой код | 1977 |

|

SU736370A1 |

| Измеритель временных интервалов | 1981 |

|

SU981925A1 |

| Линейный интерполятор | 1982 |

|

SU1075276A1 |

| Устройство для измерения временных интервалов | 1985 |

|

SU1293692A1 |

| Преобразователь временных интервалов | 1988 |

|

SU1525914A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| Устройство для синхронизации информации,считываемой с магнитной ленты | 1980 |

|

SU982079A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Устройство для программного управления | 1982 |

|

SU1108392A1 |

| Устройство для программного управления | 1986 |

|

SU1376065A1 |

Авторы

Даты

1982-08-15—Публикация

1980-12-29—Подача