1 : . . Изобретение относится к/области Вычислительной техники и может быть (использовано в устройствах прерьшания электронных вычислитель.ных машин в целях обеспечения переменного при- 5 оритета сигналам прерывания.

Известно устройство приоритета, содержащее элементы И, НЕ, выходы входных элементов И соединены со входами элементов или, а выходы этих Ю элементов ИЛИ через элементы НЕ подключены ко входам элементов ИЛИ меньшего приоритета 1 .

Недрстатком такого устройства явт ляется невозможность динамического 15 перераспределения приоритетов меаду сигналами прерывания.

Наиболее близким по технической сущности к изобретению является уст.- 20 ройстззо переменного приоритета, содержащее регистр хранения приоритета, выходы которого соединены со входами узлов блокировки сигналов прерывания;. Регистр хранения приоритета состоит 25 из счетчика, блока управления, выходы которого соединены с управляющими входами регистра хранения приоритета, циклическрго регистра сдвига, выходы которого подключены к блоку анализа ЗО

на-единицу старшего разряда црклйчеСкого регистра сдвига 2 .

Недостатком этого известного устройства является то, что оно, кроме своего Низкого быстродействия,,не обладает возможнсрстью присвоения сигналам прерывания произвольных приоритетов .

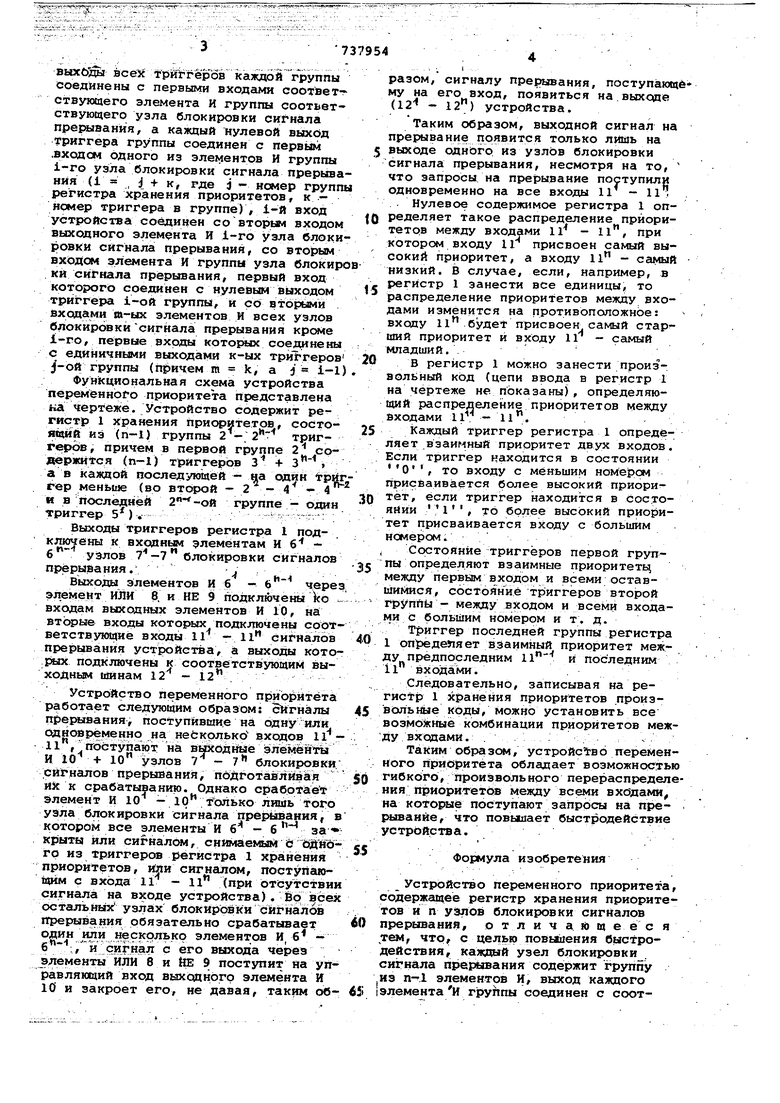

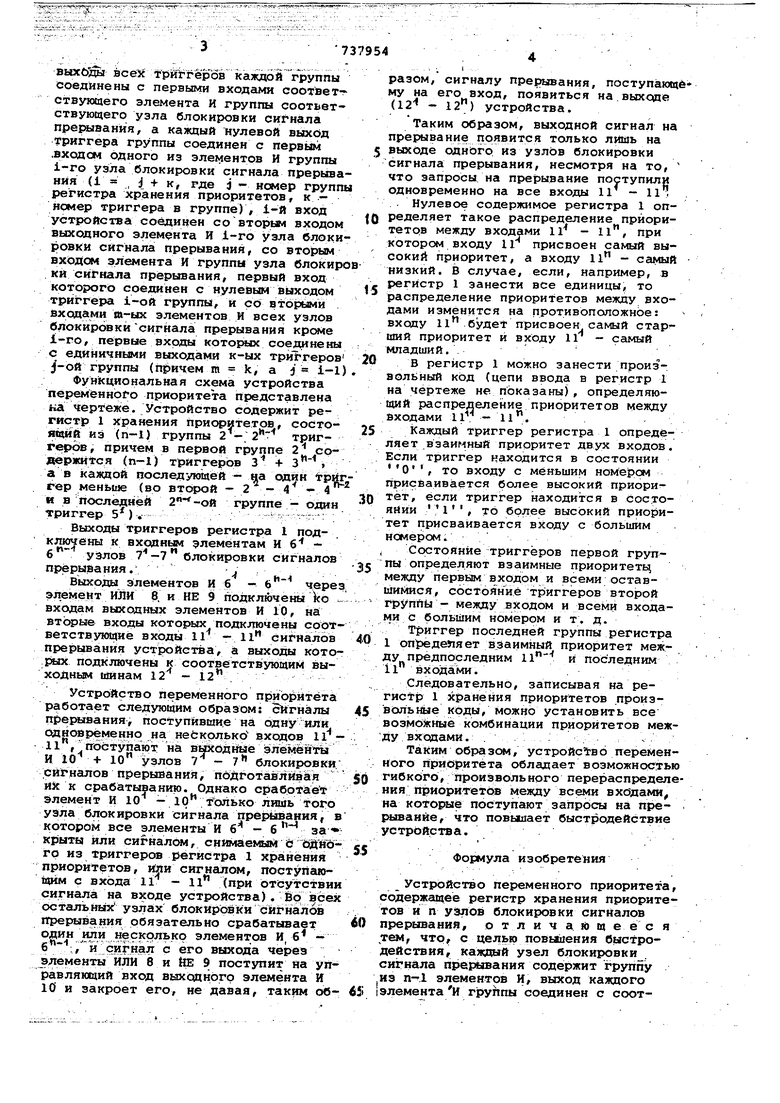

Целью настоящего изобретения является повьпиенИе быстродействия и обеспечение произвольного динамичес-кого перераспределения приоритетов между сигналами прерывания, т. е. расширение возможностей перераспределения приоритетов. Указанная цель достигается тем, в уст1эойстве переменного приоритета, содержащего регистр хранения приоритетов и п узлов блокировки сигналов прерывания каждый узел блокировки сигнала прерывания сод ержит группу из п-1 элементов.И, выход каждого элемента и группы соединен с соответствующим входом элемента ИЛИ, выход которого через элемент НЕ соединен с первйм входом выходного элемента И, выхсд которого является выходом устройства, а регистр хранения приоритетов состоит из п-1 групп /триггеров, -причем единичные выхб55ы seek триггеров каждой Fjpynnu соединены с первыми входс1ми соответт ствукадего элемента И группы соотьетствующего узла блокировки сиРналл прераваняя, а каждый 11улевой выход триггера группы соединен с первым .входом одного из элементов И группы i-ro узла блокировки сигнала прерыва ния (1 , j + к, где j - номер группы регистра хранения приоритетов, кномер триггера в группе) , 1-й вход устройсгва соединен со вторым входом выходного элемента И i-ro узла блоки ровки сигнала прерывания, со вторым входом элемента и группы узла блокир кй си1нала прерывания, первый вход которого соединен с нулевым выходом триггера i-ой группы, и со вТорьми входами т-ых элементов И всех узлов блокировкисигнала прерывания крсяче 1-го, первые входы которых соединены с единичными выходами к-ых триггеров j-ой группы ( m k, а i i-1 Функциональная схема устройства переменного приоритета представлена на чертеже. Устройство содержит регистр 1 хранения приоритетов, состотфий из (ri-l) группы 2 - 2 триггерсв, причем в первой группе 2 содержится () триггеров 3 + 3 , а в каждой последукядёй - на один триг С-ер меньше (во второй - 2 ..... , и в п х;ледней 2 --ой группе один триггер 5). ЧПГЧ1ЛТ г а С . . - . „-t ..,,-.-...-...- Выходил триггеров регистра 1 под- . ключены к входным элементам И 6 6 уЭлов блокировки сигналов прерывания. 4 Выходы элементов И 6 - 6 через элемент ИЛИ 8, и НЕ 9 подключены ko J входам выходных элементов И 10, ни входы которых подключены со ртветствующие входы 11 -и Сигна лов прерывания устройства, а выходы которых подключены к соответствующим выходным шинам 12 - 12 . Устройство переменного приоритета работает следующим образом: сигналы Прерывания, поступйвшне на одну или одновременно на несколько входов , .поступают на выходные :элёмёнты И 10+ 10 узлов 7 - 7 блокировки сигналов прерывания, пойготавЛивия и;к к срабатыванию. Однако срабоТает элемент И 10 -1() ТЪлько лищь Того узла блокировки сигнала прерывания, в котором все элементы И 6 - 6 за крыты или сигналом, снимаемым йойкогр из триггеров регистра 1 хранения приоритетов, нЕли сигналом, поступаиоJEwiM с входа 11 - 11 (при отсутствии сигнала на входе устройства). Вр всех осТальнь1х узлах блокиров1ки сигналов прерывания обязательно срабатывает один шти нескрлькр элементов - б ;,й сигнал с его выхода через элементы ИЛИ 8 и ЙЕ 9 поступит на управляющий вход выхсдногр элемента И ICf и закроет его, не давая, таким образом, сигналу прерывания, поступающему на его вход, появиться на выхспе (12 - 12) устройства. таким образом, выходной сигнал на прерывание появится только лишь на выходе одного из узлов блокировки сигнала прерывания, несмотря на то, что запросы на прерывание поступили одновременно на все входы 11 - 11 Нулевое содержимое регистра 1 определяет такое распределение приоритетов между входами 11 - п, при котором входу 11 присвоен самый высокий приоритет, а входу и - самый низкий. В случае, если, например, в регистр 1 занести все единицы, то распределение приоритетов между входами изменится на противоположное: входу 11 будет присвоен самый стар ший приоритет и входу 11 - самый младший. . В регистр 1 можно занести произвольный код (цепи ввода в регистр 1 на чертеже не показаны), определяющий распределение приоритетов между ами - И. входами Каждый триггер регистра 1 определяет взаимный приоритет двух входов. Если триггер находится в состоянии , то входу с меньшим HoMejpcM присваивается более высокий приоритет, если триггер находится в Состоянии 1, то более высокий приори. - .-. , . тет присваивается входу с большим номером. Состояние триггеров первой группы определяют взаимные приоритетц между первым входрм и всеми оставшимися, состояние тр иггеров второй rpynfiy - между входом и всеми входами с большим номером и т. д. Триггер последней группы регистра 1 определяет взаимный приоритет между предпоследним и последним 11 входами. Следовательно, записывая на регистр 1 хранения приоритетов произвольные коды, можно установить все возмо кныё комбинации приоритетов меж:ду входами. . Таким образом, устройство переменного приоритета обладает возможностью гибкого, произвольного перераспределения приоритетов между всеми входами на которые поступают запросы на пре{нлванйе, что повыиает быстродействие устройства. Формула изобретения Устройство переменного приоритета, содержащее регистр хранения приоритетов и п узлов блокировки сигналов прерывания, о т л и ч а ю щ е е с я тем, что с целью повышения быстродействия, каждый узел блокирювки. сигнала пре1жизания содержит группу из п-.1 элементов И, выход каждого |элемента/И группы соединен с соответствующим вхоДоМ элемента ИЛИ, выход которого через элемент НЕ соединен с пербым входом выходного элемента И, выход которого является выходом устройства, а регистр хранения приоритетов состоит из п-1 групп триггеров, причем единичные выходы всех триггеров Каждой группы соединены с первыми входами соответствующего элемента И группы соответств1тоwero узла блокировки сигнала прерывания, а каждый нулевой выход триггера группы соединен с первым входе одного из элементов И группы i-го узла блокировки сигнала прерывания (1 j + к, где j - группы регистра хранения приоритетов, к - номер триггера в группе), 1-ый вход устройства соединен со вторые входом

выходного элемента И i-ro узла блокировки сигнала прерывания,/со вторым входом элёйбйта-И группы узла блокировки сигнала прерывания, первый вход которогосоединен с нулевым вы- с ходом триггера 1-ой группы, и с вторыми входами т-ых элел еитов И всех узлов блокировки сигнала прерывания кроме 1-го, первые входы которых соединены.с единичными выходами к-ых триггеров j-ой группы (причем m k,

o а j i-1).

Источники информации, принятые во внимание при экспертиэе

1.Авторское свидетельство СССР 332461, КЛ.СГ 06 F 9/18, 1970.

5

2.Авторское свидетельство СССР

506654, кл G,06 Р 9/18 1974 (про|ТОТИП) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переменного приоритета | 1984 |

|

SU1208554A2 |

| Устройство переменного приоритета | 1986 |

|

SU1388867A2 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для управления прерыванием программ | 1981 |

|

SU978150A1 |

| Многоканальное устройство переменного приоритета | 1983 |

|

SU1120332A1 |

| Устройство для обмена информацией | 1984 |

|

SU1180905A1 |

| УСТРОЙСТВО ПРИОРИТЕТНЫХ ПРЕРЫВАНИЙ С АВТОМАТИЧЕСКОЙ ВЫРАБОТКОЙ КОДА ПРИОРИТЕТНОЙЗАЯВКИ | 1968 |

|

SU206891A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Авторы

Даты

1980-05-30—Публикация

1978-11-01—Подача